单周期CPU设计与Vivado仿真实践

需积分: 0 21 浏览量

更新于2024-08-04

收藏 459KB DOCX 举报

"简易单周期CPU实验指导书"

在本次实验中,我们将构建一个简易的单周期CPU,基于MIPS架构。MIPS架构CPU的工作流程包括五个主要阶段:取指(Instruction Fetch, IF)、译码(Decode, DE)、执行(Execution, EX)、访存(Memory Request, MEM)和回写(Write Back, WB)。实验分为多个步骤,逐步构建CPU的各个模块。

实验一已经设计了ALU并熟悉了存储器IP的使用。实验二则实现了CPU的取指和译码阶段,制作了PC(程序计数器)和控制器。现在,我们需要利用数字逻辑实验中的多路选择器、加法器等组件,结合前两个实验的成果,来完成单周期CPU的数据通路。

实验目标包括理解不同指令在数据通路中的执行路径,并掌握Vivado仿真工具的使用。实验所需的设备有个人电脑、特定的实践平台或实验开发板,以及Xilinx Vivado 2017.x版本开发套件。

实验内容涉及设计多个模块,包括已经完成的ALU和PC,以及需要实现或复用的adder、mux2、signext、sl2。adder和mux2在数字逻辑课程中已经实现,而signext和sl2的实现细节可以在实验原理中找到。此外,还需要Controller的两部分——main_decoder和alu_decoder。同时,需要使用Block Memory Generator IP创建指令存储器inst_mem(SinglePortRom)和数据存储器data_mem(SinglePortRam),确保PC地址位数的一致性。

为了完成实验,需要按照指令执行的顺序连接这些模块。提供的top文件定义了接口,需要确保新设计的模块与其兼容。实验还提供了一个仿真程序,最终通过仿真结果验证指令的正确执行。

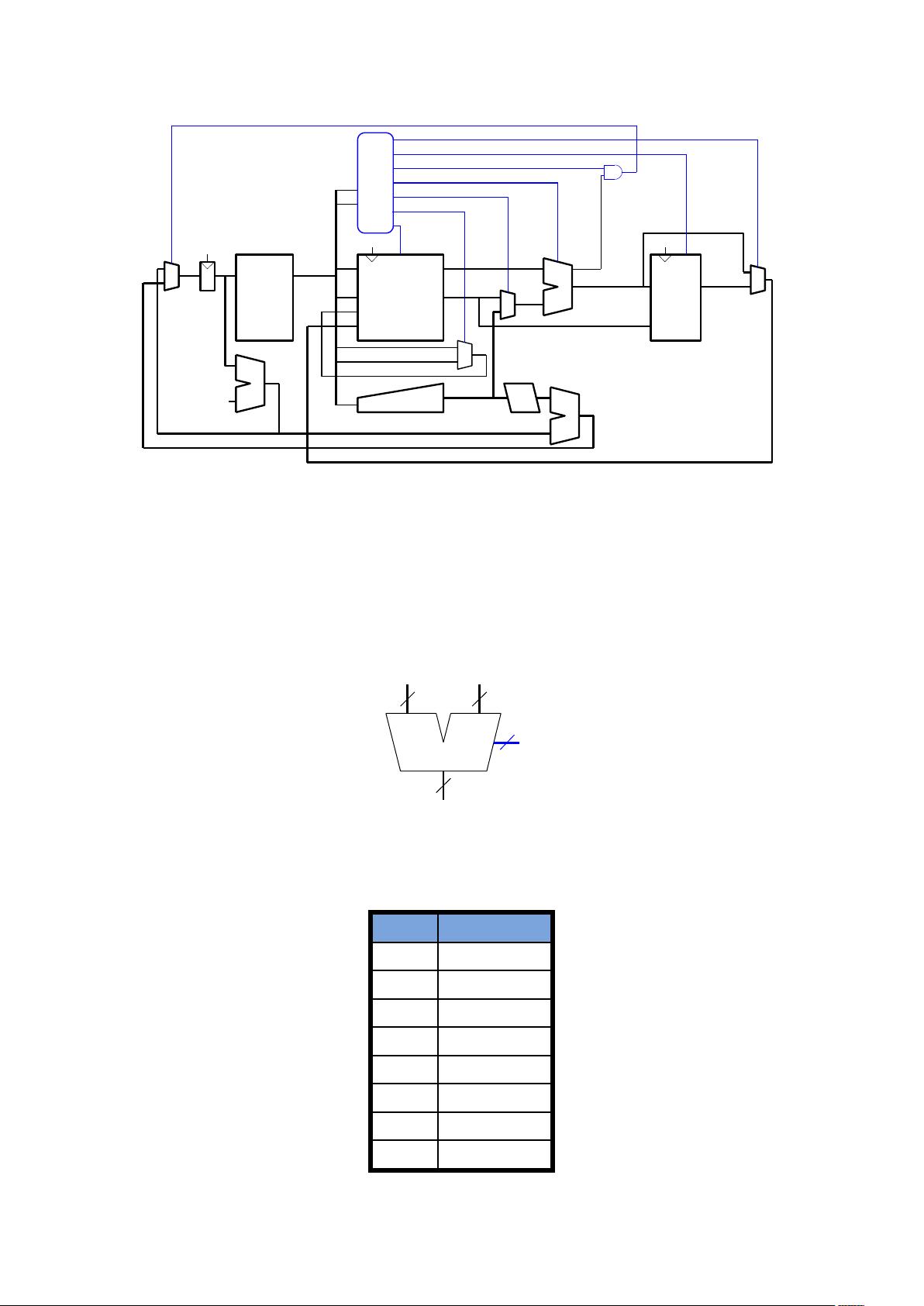

实验原理部分介绍了单周期CPU的总体框架和数据通路图。图3.1展示了已完成部分和待完成的datapath。图3.2详细描绘了包括add、and、sub、or、slt、beq、j、lw、sw、addi等指令在内的数据通路,这些指令是实验三的目标。虽然这里只实现了一部分MIPS指令,但目的是通过这个过程掌握数据通路的分析方法。

通过这个实验,学生不仅可以深化对MIPS架构的理解,还能提升Vivado的使用技能,以及硬件描述语言(HDL)设计和验证的实际操作能力。

忧伤的石一

- 粉丝: 31

- 资源: 332

最新资源

- 基于ssm+vue毕业生交流学习平台.zip

- mini usb接口SX1308+KV-201X设计超声波雾化加湿器控制器AD原理图+PCB工程文件.zip

- jms-simple:JMS Spring Boot 队列主题

- Resources:我创建了此存储库来存储和访问几个链接,图像和资源,以使其在全球范围内可用,以用于非商业项目

- 数据库管理后台dashboard .sketch素材下载

- Python 程序设计(微课版)电子课件ppt.zip

- ins_单片机电子琴_INS_单片机_taskj4m_

- jQuery实现猜猜你是谁微信小游戏源码.zip

- stickyboard-core:StickyBoard核心

- uart_led.zip

- 基于ssm的电影订票互动系统.zip

- 三菱的布袋除尘器程序.zip三菱PLC编程案例源码资料编程控制器应用通讯通信例子程序实例

- ble103AT-demo-V1.0.rar

- 行业文档-设计装置-一种用于七氟丙烷热分解产生HF的浓度实时测量装置.zip

- 基于ssm+jsp的水果商城.zip

- SAP005-cipher