FPGA上的硬件构造语言:灵活设计空间探索

PDF格式 | 3.27MB |

更新于2024-06-17

| 37 浏览量 | 举报

"这篇文档是Bruno Ferres的一篇关于在FPGA上使用硬件构造语言进行灵活设计空间探索的学术论文。该论文由格勒诺布尔阿尔卑斯大学出版,作者在微和纳米技术/微电子学领域进行了深入研究。论文的HAL ID为tel-03709710,于2022年6月30日提交到HAL,这是一个多学科的开放获取档案馆。Bruno Ferres的博士研究由UGA/Polytech的Frédéric Rousseau教授和Grenoble INP/Ensimag的Olivier Müller共同指导,专注于FPGA上的结构设计技术和设计空间探索。论文于2022年3月23日公开答辩,评审委员会包括Sebastien Pillement、Frédéric Eresse、Christophe Jego、Régis Leveugle和Pierre-Henri Auren作为技术负责人。"

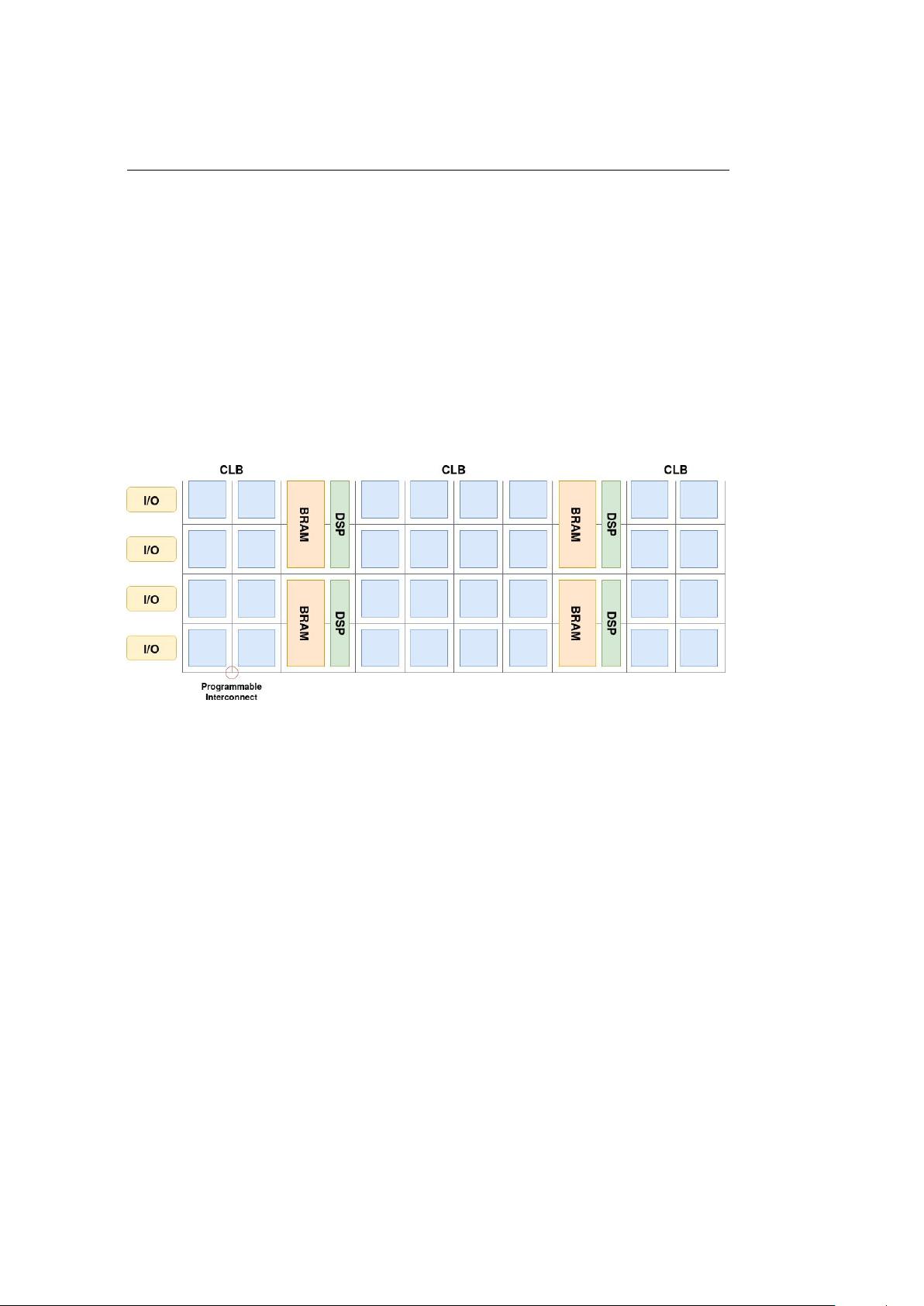

在FPGA(现场可编程门阵列)上进行设计空间探索是现代电子系统设计中的一个关键环节,因为它允许开发者在满足性能、功耗和成本目标的同时,实现设计的灵活性和优化。硬件构造语言(如VHDL和Verilog)是实现这一目标的主要工具,它们允许设计师直接描述硬件逻辑,而非依赖于高级软件语言的抽象。

这篇论文的核心在于如何有效地利用这些硬件描述语言来探索FPGA上的设计空间。设计空间探索涉及到多个方面,包括逻辑综合、布局布线以及时序分析。逻辑综合是将高级设计语言(如C、SystemC或硬件描述语言)转换成门级网表的过程,这个过程可以调整以优化特定指标,如速度、面积或功耗。布局布线则涉及到将这些逻辑门放置并连接在FPGA的物理结构上,这一步骤也对性能有重大影响。时序分析则是确保设计满足预定的时序约束,如最大时钟周期。

Bruno Ferres的研究可能涵盖了以下关键点:

1. **高级语言到硬件描述的转换**:探讨了如何将系统级设计有效地转换为FPGA可执行的硬件描述,可能包括算法的硬件实现方法和优化策略。

2. **设计参数化**:研究了如何通过参数化设计来探索不同配置下的性能和资源利用率,以找到最优解。

3. **自动化设计流程**:可能开发了自动化工具或脚本,以加速设计空间的遍历和评估。

4. **性能建模和预测**:可能涉及了建立数学模型来预测不同设计决策对最终实现的影响。

5. **优化技术**:可能研究了各种优化技术,如逻辑分区、时钟树合成和逻辑重用,以提高FPGA设计的效率。

6. **实验与案例研究**:通过实际FPGA项目展示了设计空间探索的实践方法和效果,提供了具体的结果和比较。

通过这样的研究,Bruno Ferres的工作为电子工程师提供了一种更高效的方法来利用FPGA的潜力,尤其是在纳米电子学和微电子学领域,这对于快速发展的嵌入式系统和高性能计算应用至关重要。这种设计空间探索的灵活性有助于应对不断变化的技术需求和市场挑战。

相关推荐

cpongm

- 粉丝: 6

最新资源

- VC++实现OpenGL 3D俄罗斯方块游戏教程

- 探索Swift在西澳大利亚的应用实践

- 商业咨询表单网页模板——高效设计与管理工具

- 重现论文“Top-k Entity Augmentation”结果的REX源代码解析

- 美国大都市经济网络地图的分析与批判

- Angular 8入门详解与实践指南

- Java基础入门项目压缩包解析

- Terraform Cloud入门指南:创建AWS空表

- ServerSuperIO: 轻型高级通信框架与设备驱动开发套件

- Discord监控机器人:实时ping网站离线警报

- GKSVM: Orfeo ToolBox远程模块集成旧版libSVM代码

- 彩色精致SWOT分析图表PPT模板下载

- 404网页错误模板的设计与应用

- JavaScript幕后操作:Backroom技术解析

- Django学习网络应用开发经验分享

- k8s-config:掌握Kubernetes配置存储库技巧