DC入门指南:常用命令详解及参数配置

需积分: 44 171 浏览量

更新于2024-07-18

6

收藏 512KB PDF 举报

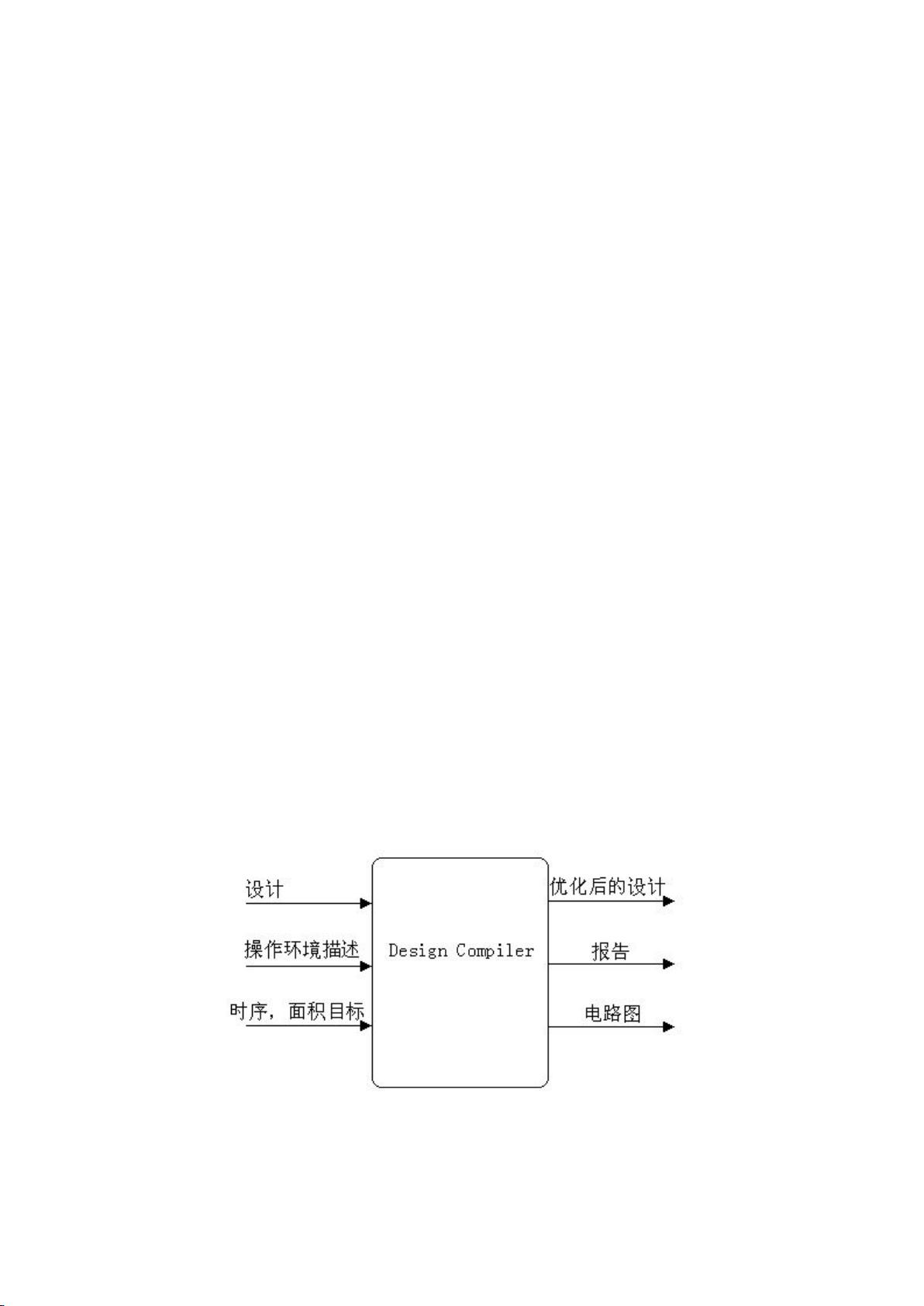

DC,全称为Design Compiler,是Synopsys公司提供的高级逻辑综合工具,用于将硬件描述语言(HDL)如Verilog、VHDL或EDIF描述的电路转化为符合特定工艺的门级实现。DC的核心功能在于它能够自动处理设计描述和约束,通过逻辑综合算法优化电路结构,以达到最佳的性能指标,如功耗、面积和时序一致性。这个工具支持多种输入格式,包括.db、.v、.vhd、EDIF等,并能够生成多种输出格式,如.db、.v、.vhd、EDIF、SDF等,便于后续的验证和集成。

对于新接触DC的设计者来说,理解其工作原理和基本操作至关重要。首先,DC能够接受多种输入源,无论是高级语言描述还是低级网表文件,这使得设计师可以根据自己的习惯选择最合适的输入形式。它会根据用户提供的设计描述和约束条件,生成一个经过优化的门级电路,同时考虑到用户对性能的需求,如在保持时间准确性的同时最小化面积或功耗。

DC的配置过程是关键环节,用户需要在.synopsys_dc.setup文件中设置重要的参数,如搜索路径(search_path),目标库(target_library),链接库(link_library)和符号库(symbol_library)。搜索路径决定工具查找所需库的顺序,目标库则指在映射阶段使用的具体工艺库,链接库则是编译过程中引用的库,通常需要使用星号(*)通配符来指定所有内存中的库。

此外,DC还提供了多途径的帮助文档和支持,可以通过SOLD (Synopsys Online Documentation)在线查询,或者在命令行中使用man和info命令获取命令帮助。SOLD文档可以通过在终端中运行sold&命令或定位到安装目录的online子目录来访问。

DC是一个强大且灵活的工具,对于从事硬件设计的工程师来说,掌握其基本命令、输入输出格式以及配置方法,能够显著提升设计效率和结果的质量。通过合理配置和利用DC的特性,设计师能够在满足性能需求的同时,实现设计的高效和精准。

2008-11-11 上传

点击了解资源详情

2012-05-21 上传

2021-10-07 上传

qq_35681626

- 粉丝: 0

- 资源: 2

最新资源

- Angular实现MarcHayek简历展示应用教程

- Crossbow Spot最新更新 - 获取Chrome扩展新闻

- 量子管道网络优化与Python实现

- Debian系统中APT缓存维护工具的使用方法与实践

- Python模块AccessControl的Windows64位安装文件介绍

- 掌握最新*** Fisher资讯,使用Google Chrome扩展

- Ember应用程序开发流程与环境配置指南

- EZPCOpenSDK_v5.1.2_build***版本更新详情

- Postcode-Finder:利用JavaScript和Google Geocode API实现

- AWS商业交易监控器:航线行为分析与营销策略制定

- AccessControl-4.0b6压缩包详细使用教程

- Python编程实践与技巧汇总

- 使用Sikuli和Python打造颜色求解器项目

- .Net基础视频教程:掌握GDI绘图技术

- 深入理解数据结构与JavaScript实践项目

- 双子座在线裁判系统:提高编程竞赛效率