PCIe 4.0电气规范预览解析

需积分: 33 6 浏览量

更新于2024-07-22

1

收藏 2.41MB PDF 举报

"PCIe_4.0_electrical preview.pdf"

本文档主要介绍了PCI Express(PCIe)4.0电气规范的预览内容,由PCI-SIG(Peripheral Component Interconnect Special Interest Group)成员和工作小组共同编撰。PCI-SIG开发者大会是发布这一预览信息的平台,旨在分享PCIe 4.0规格开发过程中的最新进展。

PCIe 4.0的推出主要受到以下动机和假设的驱动:

1. 随着技术的进步和市场需求的增长,对更高数据传输速率的需求日益强烈,PCIe 4.0在PCIe 3.0的基础上翻倍,达到了每通道16 GT/s(吉比特每秒),显著提升了系统间的通信速度。

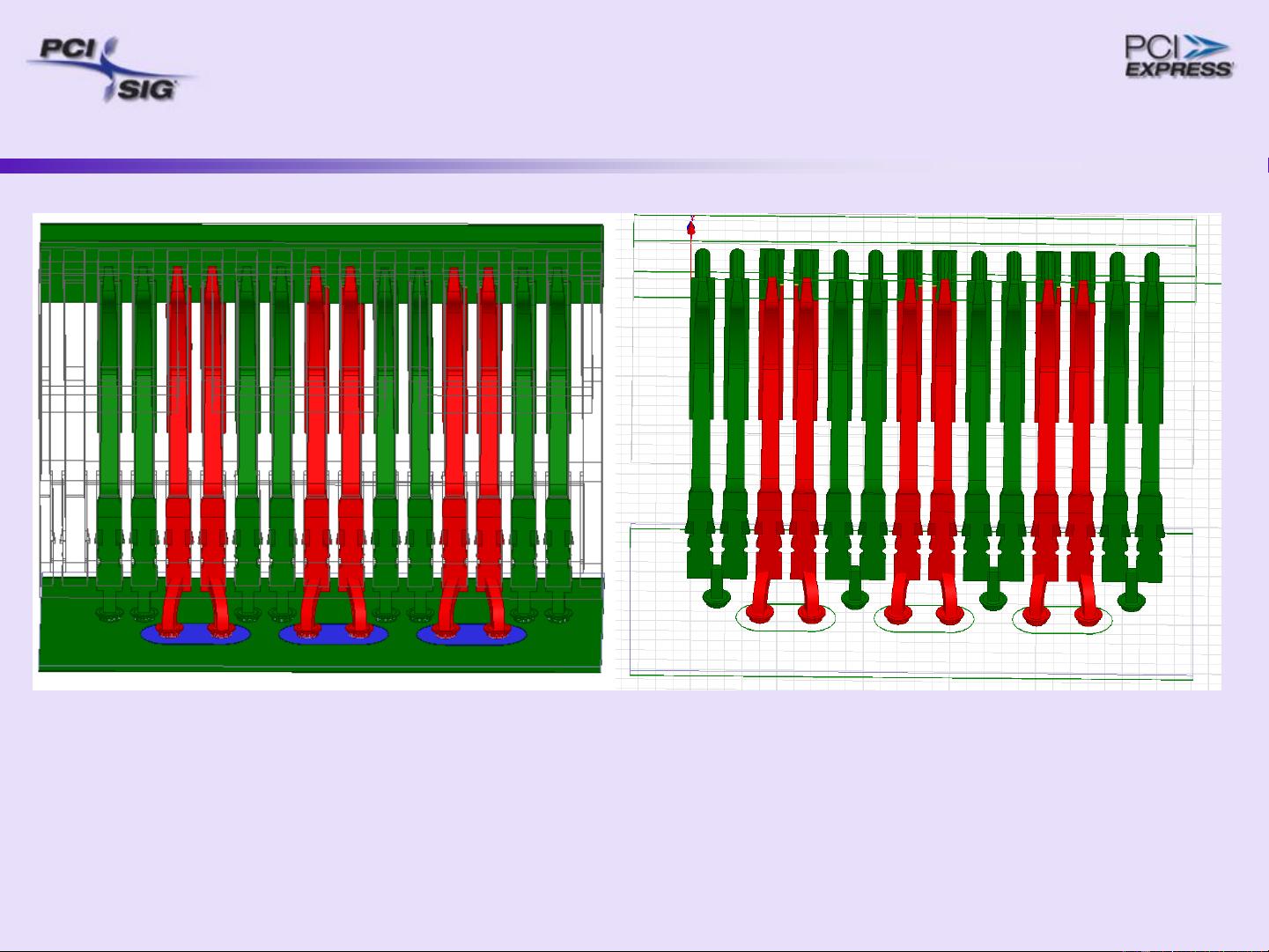

2. 设计者进行了通道路径寻找研究,以确保在高速率下信号的完整性。这包括对CEM(Compliant Edge-Mount)连接器的评估,以及对通道改进的探讨,如材料、布局和设计优化,以减少信号损失和噪声。

3. 为了实现可靠的数据传输,进行了硅路径寻找研究,包括发射器(Tx)和接收器(Rx)的规格设定,以及如何通过die-pad电容缓解(capmitigation)来控制芯片上的电磁干扰(EMI)问题。

在规范更新方面:

1. 电气部分的重新组织使得设计者能更清晰地理解规范要求,简化了设计流程。

2. 预期会提供更多的设计辅助材料,帮助工程师理解和实施PCIe 4.0标准。

3. 提供了规格发布的时间线,以便业界可以规划自己的产品开发计划。

后续步骤包括继续推进PCIe 4.0的开发,同时也会关注PCIe 3.0的增强功能请求(ECRs),以确保现有标准的持续优化。

总结,PCIe 4.0的电气预览涵盖了从规格制定的动机到实际物理层设计的诸多细节,包括数据速率选择、通道和硅片级别的挑战,以及规范的不断更新和完善。这一技术升级对于提升计算机系统和外设之间的通信效率具有重要意义。

2018-04-19 上传

2020-03-05 上传

2020-10-20 上传

2022-07-13 上传

2019-11-13 上传

2021-07-13 上传

2020-03-04 上传

2024-08-08 上传

edisee

- 粉丝: 0

- 资源: 1

最新资源

- 深入浅出:自定义 Grunt 任务的实践指南

- 网络物理突变工具的多点路径规划实现与分析

- multifeed: 实现多作者间的超核心共享与同步技术

- C++商品交易系统实习项目详细要求

- macOS系统Python模块whl包安装教程

- 掌握fullstackJS:构建React框架与快速开发应用

- React-Purify: 实现React组件纯净方法的工具介绍

- deck.js:构建现代HTML演示的JavaScript库

- nunn:现代C++17实现的机器学习库开源项目

- Python安装包 Acquisition-4.12-cp35-cp35m-win_amd64.whl.zip 使用说明

- Amaranthus-tuberculatus基因组分析脚本集

- Ubuntu 12.04下Realtek RTL8821AE驱动的向后移植指南

- 掌握Jest环境下的最新jsdom功能

- CAGI Toolkit:开源Asterisk PBX的AGI应用开发

- MyDropDemo: 体验QGraphicsView的拖放功能

- 远程FPGA平台上的Quartus II17.1 LCD色块闪烁现象解析