Vivado FPGA设计实战:从新建工程到Chipscope调试

"这篇教程详细介绍了如何在Vivado环境下进行FPGA开发,包括新建工程、选择器件、源代码输入、IP核的调用与例化、功能仿真、Chipscope的使用以及时钟约束、管脚锁定和工程实现等关键步骤。教程以实例为引导,涵盖PLL时钟生成、DDS信号发生器的配置,以及如何利用Chipscope进行调试。"

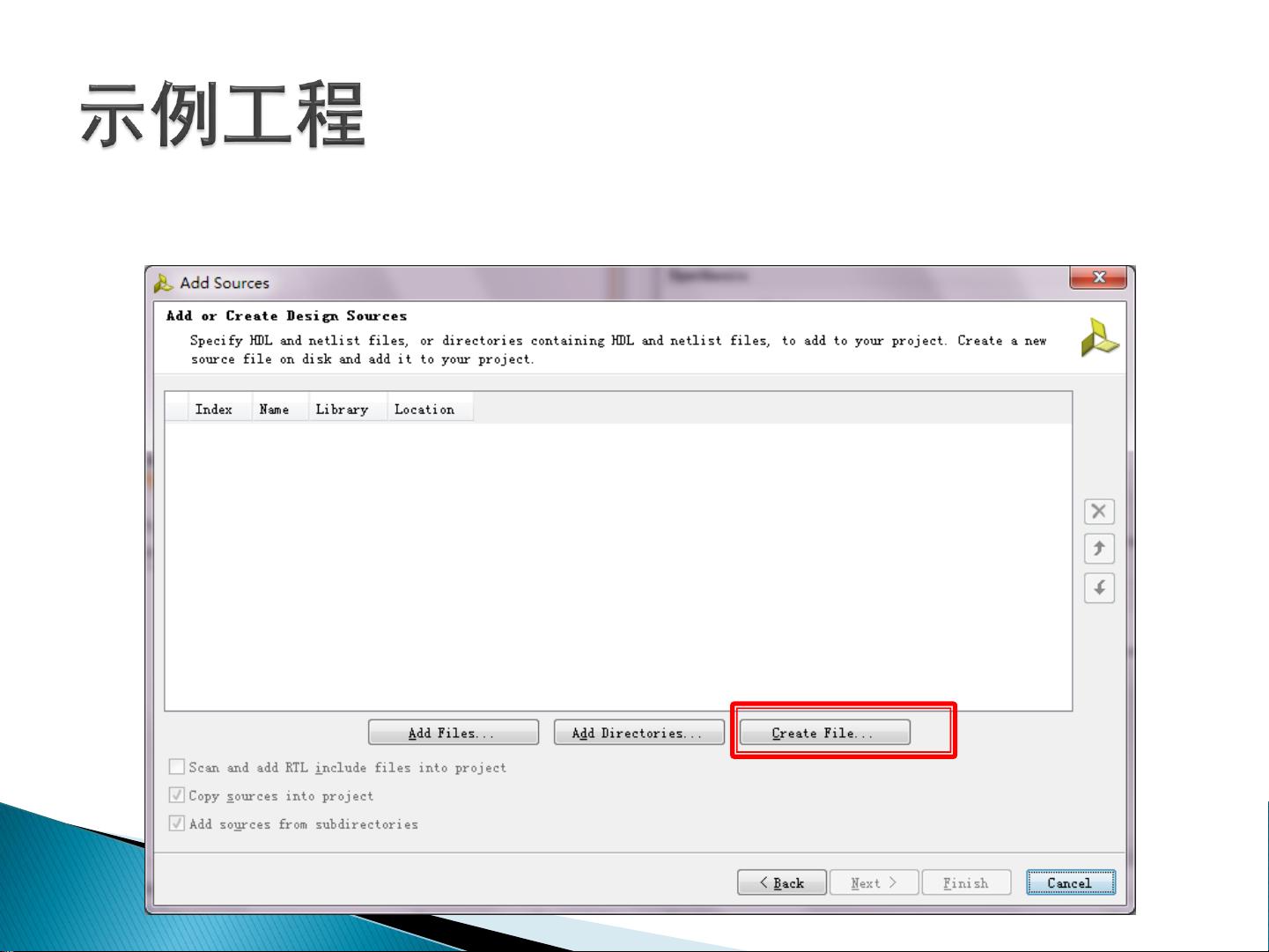

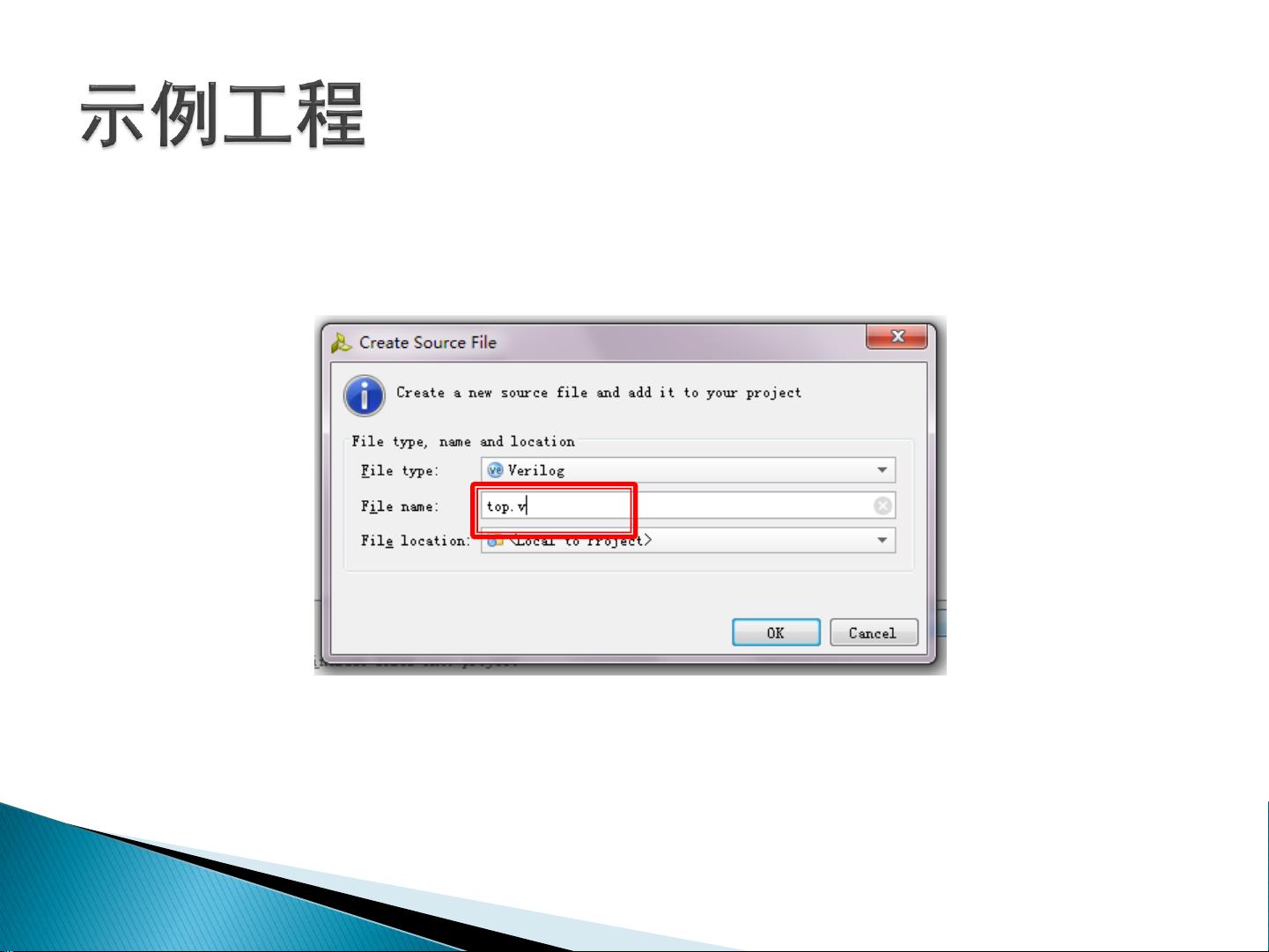

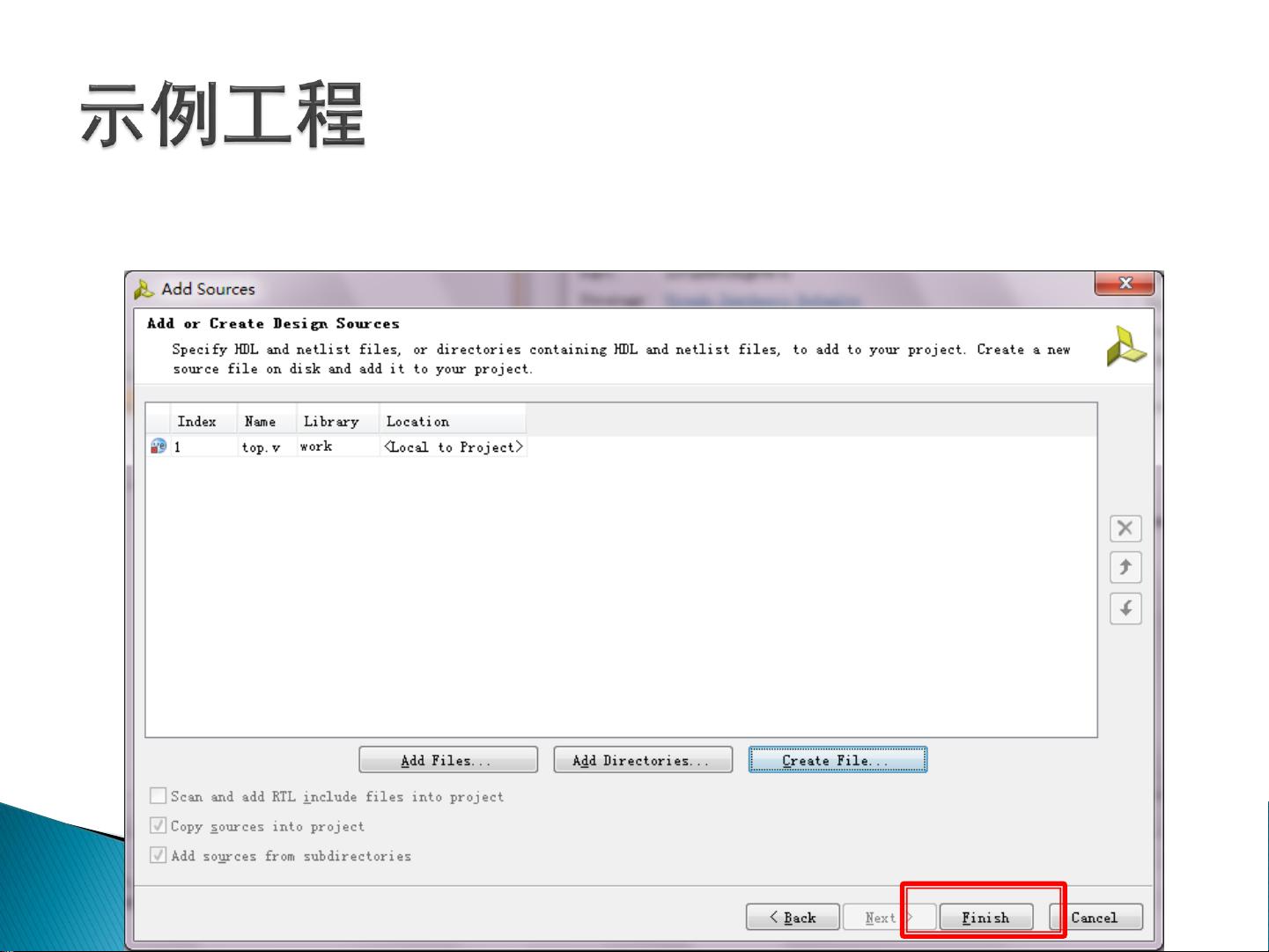

在Vivado中,首先需要新建工程,选择合适的FPGA器件。这一步至关重要,因为不同的器件具有不同的逻辑资源和时钟速度,会影响到设计方案的选择和性能。接着,用户需要输入源代码,这通常包括定义顶层文件和各个子模块的Verilog或VHDL代码。在源代码中,可以创建计数器、DDS(直接数字频率合成)等模块,通过调用IP核如PLL来生成不同频率的时钟。

调用IP核是Vivado的一大特色,例如PLL(锁相环)IP核用于频率合成,可以根据输入时钟生成多种输出频率。用户可以通过界面配置时钟输入频率,并对信号进行重命名,以便在代码中更好地识别和管理。同样,DDS IP核则用于生成精确的数字频率信号,用户需要指定所需的输出频率,并声明相关信号。

为了进行功能仿真,Vivado提供了集成的仿真工具,可以验证设计的功能是否符合预期。此外,Chipscope是一种内建的逻辑分析仪,用于在硬件级别调试设计。在代码中声明DEBUG变量,即使未连接到其他模块,也能在Chipscope中观察到,这对于查找问题非常有用。在设置Chipscope的Debug信号时,需要选择合适的采样时钟,并添加要监控的设计信号。

在完成所有设计工作后,需要进行综合(Synthesis)步骤,这将把高级语言代码转化为硬件描述语言,然后进行实现(Implementation),包括布局布线等,最终生成用于编程FPGA的bit文件。在这一过程中,还需要设置时钟约束,确保设计满足实时性要求,并锁定管脚,以确保硬件连接正确无误。

Vivado中文教程详细阐述了FPGA设计流程,从创建工程到实现和调试,为初学者和有经验的工程师提供了一条清晰的学习路径。通过实践这些步骤,用户能够有效地掌握Vivado工具并成功地进行FPGA项目开发。

2019-06-21 上传

2022-07-15 上传

2018-04-15 上传

2024-12-23 上传

2019-12-01 上传

2020-11-16 上传

2017-07-20 上传

bingoyuchxi

- 粉丝: 0

- 资源: 1

最新资源

- Grace Gmail Plugin for Chrome-crx插件

- 在您的本机应用程序中设置应用程序图标-Swift开发

- FittingSurvivalModelss.zip_matlab例程_matlab_

- qqbot:QQBot:基于腾讯的SmartQQ的对话机器人

- exportDoc:使用Itext API解决使用Java创建Word文档的问题

- nodebootstrap-clustering:NodeBootstrap的群集组件

- heroku_template

- lab-06-后端

- 前端+php+Apache压缩文件

- 具有PKCE的轻量级OAuth 2.0客户端-Swift开发

- javascript

- vcDigitalImageProcess.zip_图形图像处理_Visual_C++_

- Arkiver Web Collector-crx插件

- App-TimeTracker:从命令行进行分布式时间跟踪

- ActiveUsers Block for Moodle-开源

- PyPI 官网下载 | sklearn2pmml-0.73.3.tar.gz