Nios CPU详解:结构、编程模型与Avalon总线

"本章详细介绍了Nios CPU的结构、编程模型、Avalon总线以及外设的组织与使用。Nios CPU是基于RISC架构的5级流水线微处理器,采用Harvard结构,拥有独立的指令和数据总线。Avalon总线作为其与外部组件通信的基础,支持灵活的主从端口连接和仲裁。Nios的可配置性和可优化性使其能适应不同的系统需求。此外,章节内容还包括了Nios CPU的各个组成部分,如高速缓存、移位单元、乘法器、中断支持和调试模块。在编程模型部分,讲解了寄存器、存储器结构、寻址方式、程序流程控制、异常处理和流水线机制。Avalon总线部分涵盖了其基本概念、传输类型、从端口和主端口的特性,以及与外部设备的接口。最后,章节讨论了如何使用SOPCBuilder配置外设,包括定时器、并行I/O、UART、DMA控制器和SPI接口。"

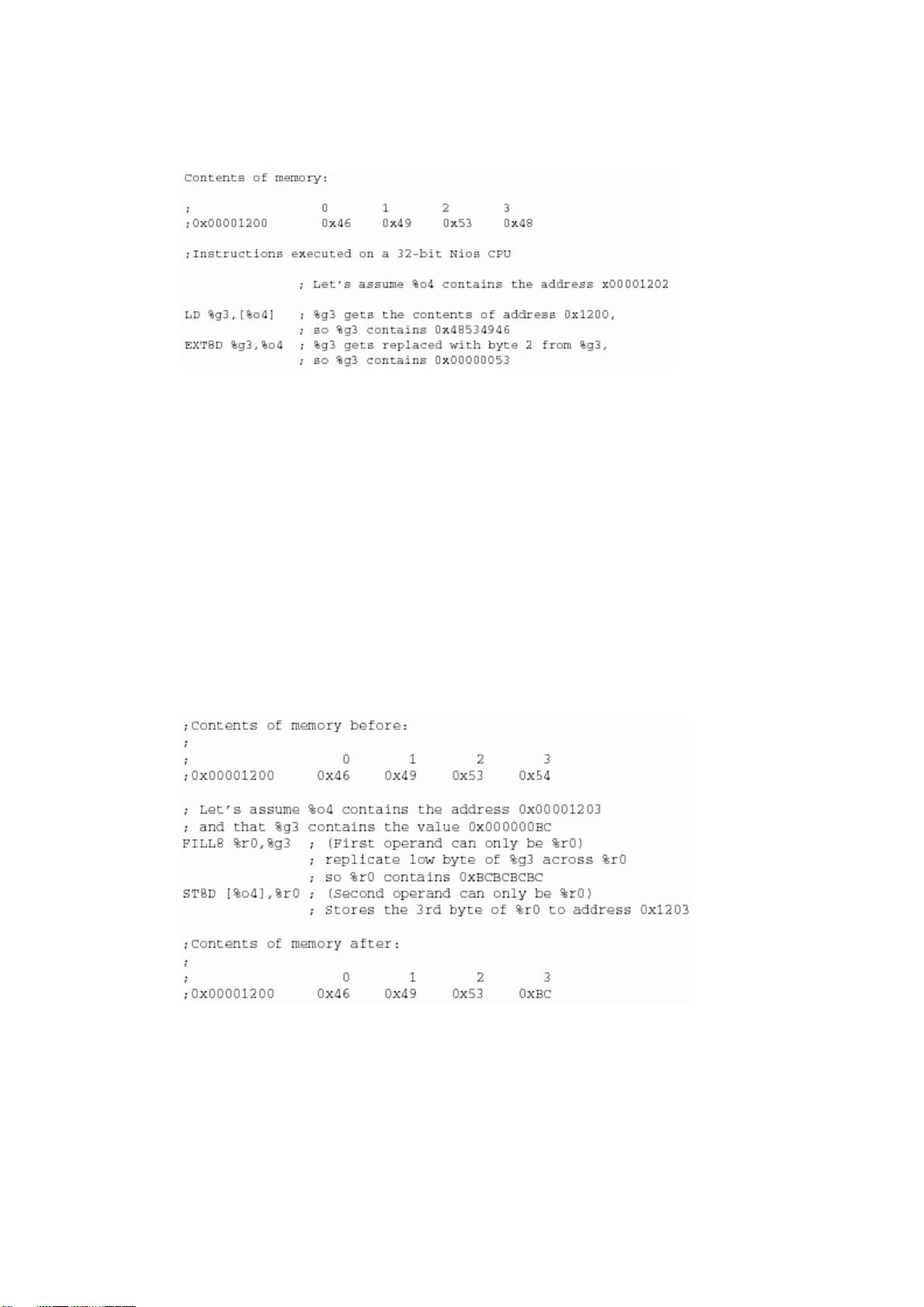

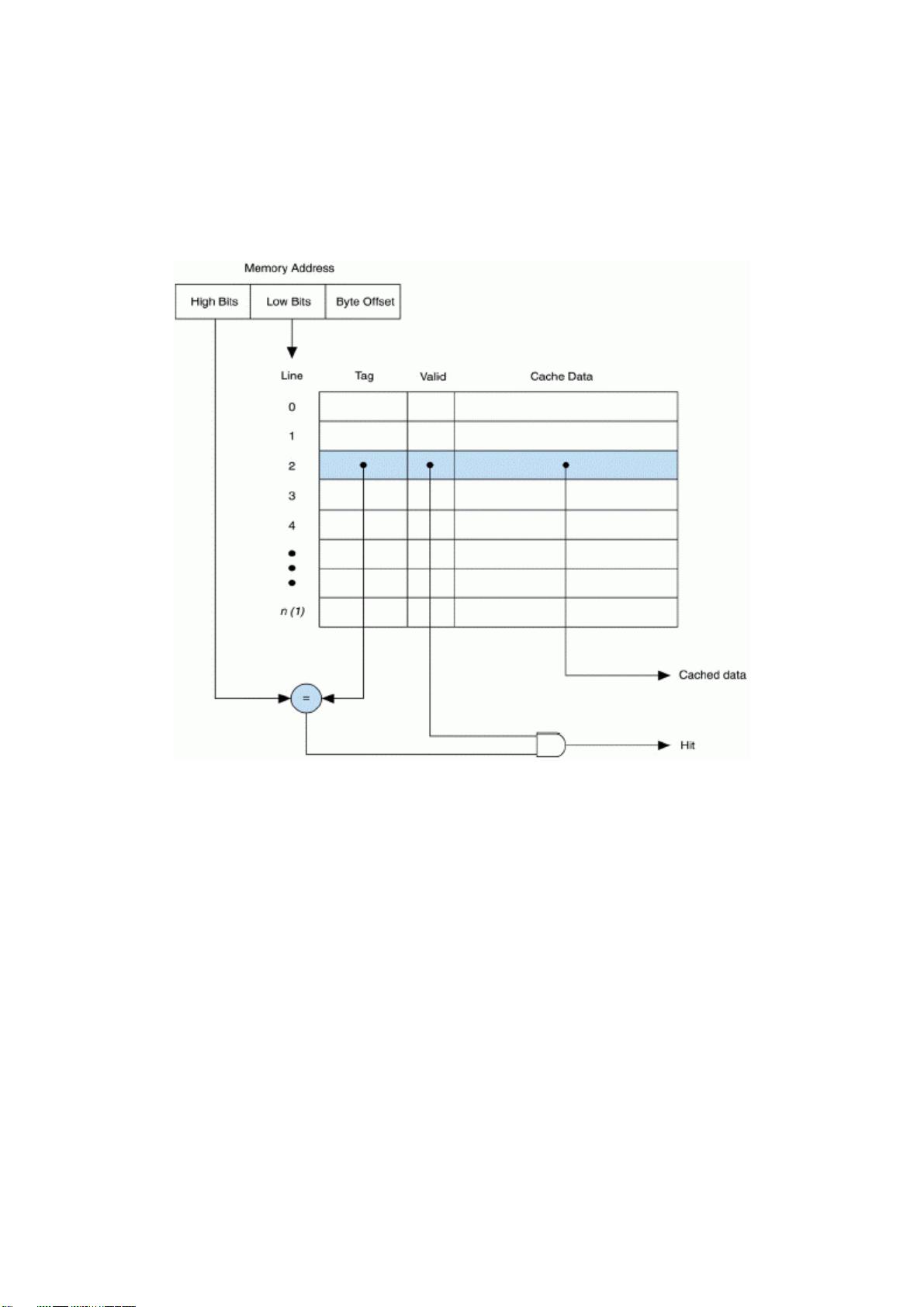

在Nios CPU结构中,除了基本的硬件特性外,还特别强调了指令总线主端口和数据总线主端口的角色,它们分别负责指令的读取和数据的读写操作。高速缓存用于提高CPU访问数据的速度,移位单元支持位操作,乘法支持提供了硬件乘法功能,中断支持允许CPU响应外部或内部事件,而NIOS片上调试模块(OCI模式)则为软件开发和故障排查提供了便利。

在编程模型中,寄存器是执行指令的基础,存储器结构包括了不同级别的缓存和主存储器,寻址方式决定了CPU如何访问这些存储位置,程序流程控制涉及分支、跳转等指令,异常事件处理则关乎错误和中断的管理,流水线技术提高了CPU的处理效率。

Avalon总线是 Altera 平台中重要的通信协议,它定义了主从设备之间的交互方式。从端口和主端口的传输特性使系统能够灵活扩展,而高级传输特性如突发传输和预取操作进一步优化了性能。通过SOPCBuilder,开发者可以轻松配置和集成各种外设,如定时器用于计时和同步,GPIO口实现并行输入输出,UART用于串行通信,DMA控制器则能够高效地进行大块数据传输,SPI接口则常用于连接其他低速外围设备。

本章内容深入浅出地解析了Nios CPU的内部工作原理和外部扩展方法,对于理解和设计基于Nios的嵌入式系统至关重要。

118 浏览量

138 浏览量

123 浏览量

点击了解资源详情

2021-10-12 上传

112 浏览量

2022-11-10 上传

2021-07-13 上传

137 浏览量

ligang411

- 粉丝: 0

- 资源: 13

最新资源

- 2009年电子商务资料全

- 最初级的PB入门教程。

- 计算机网络课后答案 谢希仁

- linux操作系统的操作与搜索命令

- 2009网络工程师考试大纲

- starting-struts2-chinese starting-struts2-chinese

- 第10章 Web开发基础知识

- 学习Linux操作系统的基本

- SQL Server 2005安装使用教程.pdf

- 如何把Windows Vista系统打造成局域网的FTP服务器

- linux系统分析进程管理

- ADO.NET完全攻略

- java 非常好的10个主题

- hibernate快速学习指南

- 模拟电子(第四版华成英主编)习题答案02

- linux操作系统下c语言编程入门