零延迟时钟缓冲器:新型PLL设计与特性

179 浏览量

更新于2024-08-28

收藏 265KB PDF 举报

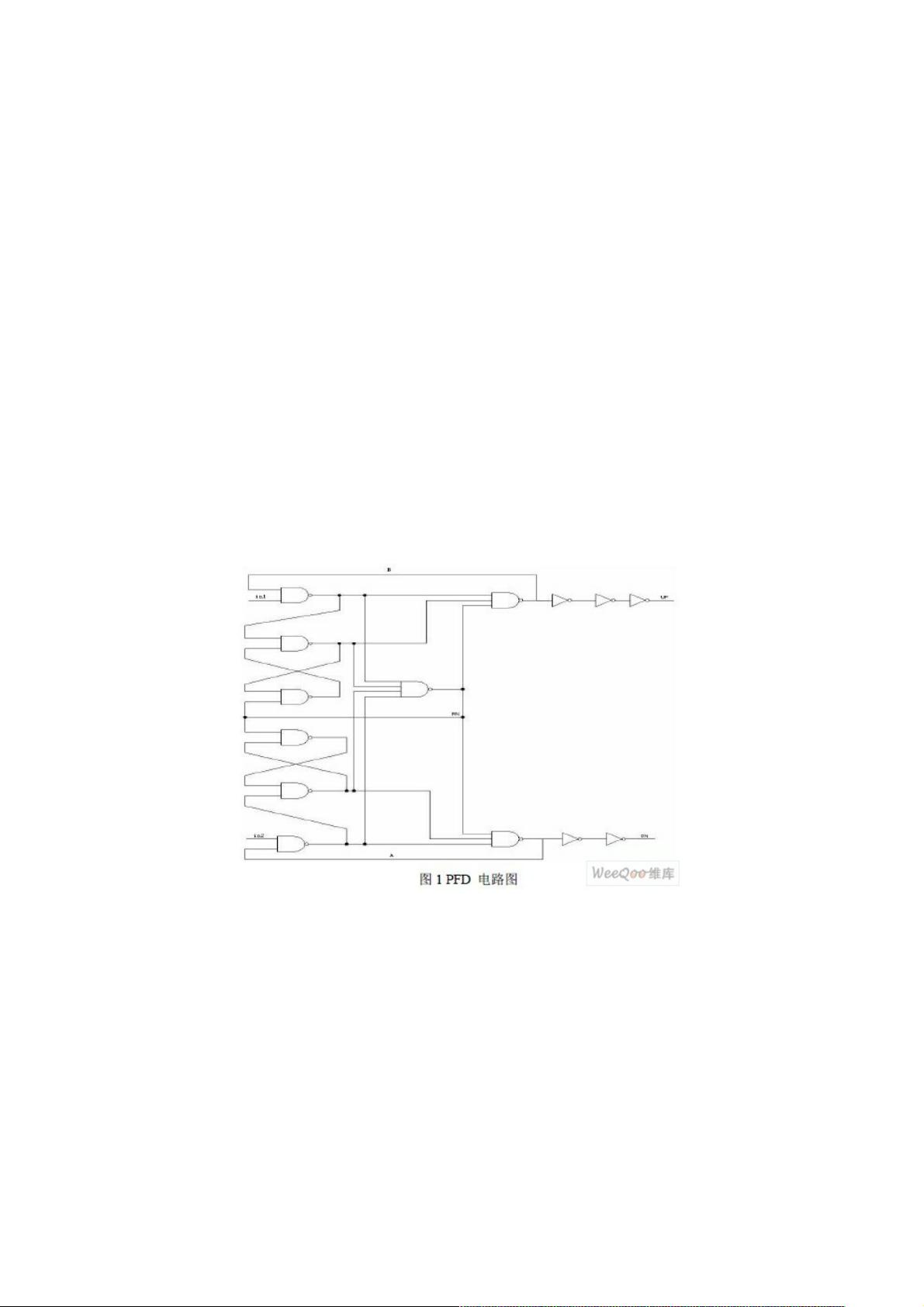

本文主要探讨的是"用于零延迟缓冲器的PLL设计",这是一种高性能的锁相环路(Phase-Locked Loop, PLL)电路,特别针对高速数字电路的需求而设计。作者利用了先进的0.5微米CMOS工艺(CMOS Complementary Symmetric Metal-Oxide-Semiconductor,CSMC),如N阱工艺,以提高电路的集成度和可靠性。

设计的核心组件包括一个低失配的电荷泵,这种结构简单但效率高的元件在PLL中起到关键作用,确保了时钟信号的稳定传输。此外,文中着重介绍了一种差分结构的压控振荡器,这种设计具有出色的抗噪声性能,能够有效抑制电路中的噪声干扰,确保时钟信号的纯净度。

在技术参数方面,该PLL在3.3伏电源下工作,覆盖的频率范围从10MHz到140MHz,这使得它能够适应多种应用需求。在性能指标上,周对周抖动在50MHz下仅有45皮秒(ps),这表明其频率稳定性极高。此外,设计的功耗控制在4.8毫瓦(mW),表明了良好的能效比,而芯片面积则小巧至1.2微米×1.7微米,显示了极佳的芯片设计和封装技术。

在实际应用中,这种PLL作为零延迟时钟缓冲器,对于需要高精度和高同步性的多路输出时钟系统至关重要,它能根据需要生成多个频率精确匹配的时钟信号,从而优化高性能计算机的系统时序,避免了外部时钟源同步问题,提升了整个系统的稳定性和效率。

总结来说,本文的研究重点在于开发一款紧凑型、低功耗且具有优异频率稳定性的PLL,用于解决高速数字电路中对高质量时钟信号的需求,这在现代电子系统中具有重要的实际价值。通过精密的设计和优化,这款PLL不仅提高了电路性能,还降低了功耗,对于推动电子行业的前沿发展具有显著贡献。

2020-11-09 上传

171 浏览量

120 浏览量

点击了解资源详情

166 浏览量

655 浏览量

248 浏览量

2021-10-31 上传

957 浏览量

weixin_38691641

- 粉丝: 5

最新资源

- 经典J2ME坦克对战游戏:回顾与介绍

- ZAProxy自动化工具集合:提升Web安全测试效率

- 破解Steel Belted Radius 5.3安全验证工具

- Python实现的德文惠斯特游戏—开源项目

- 聚客下载系统:体验极速下载的革命

- 重力与滑动弹球封装的Swift动画库实现

- C语言控制P0口LED点亮状态教程及源码

- VB6中使用SQLite实现列表查询的示例教程

- CMSearch:在CraftMania服务器上快速搜索玩家的Web应用

- 在VB.net中实现Code128条形码绘制教程

- Java SE Swing入门实例分析

- Java编程语言设计课程:自动机的构建与最小化算法实现

- SI9000阻抗计算软件:硬件工程师的高频信号分析利器

- 三大框架整合教程:S2SH初学者快速入门

- PHP后台管理自动化生成工具的使用与资源分享

- C#开发的多线程控制台贪吃蛇游戏源码解析