Verilog实现FSM:状态机设计与应用实例

需积分: 10 97 浏览量

更新于2024-07-31

收藏 360KB PPT 举报

"硬件描述语言与数字系统设计-状态机的结构与设计"

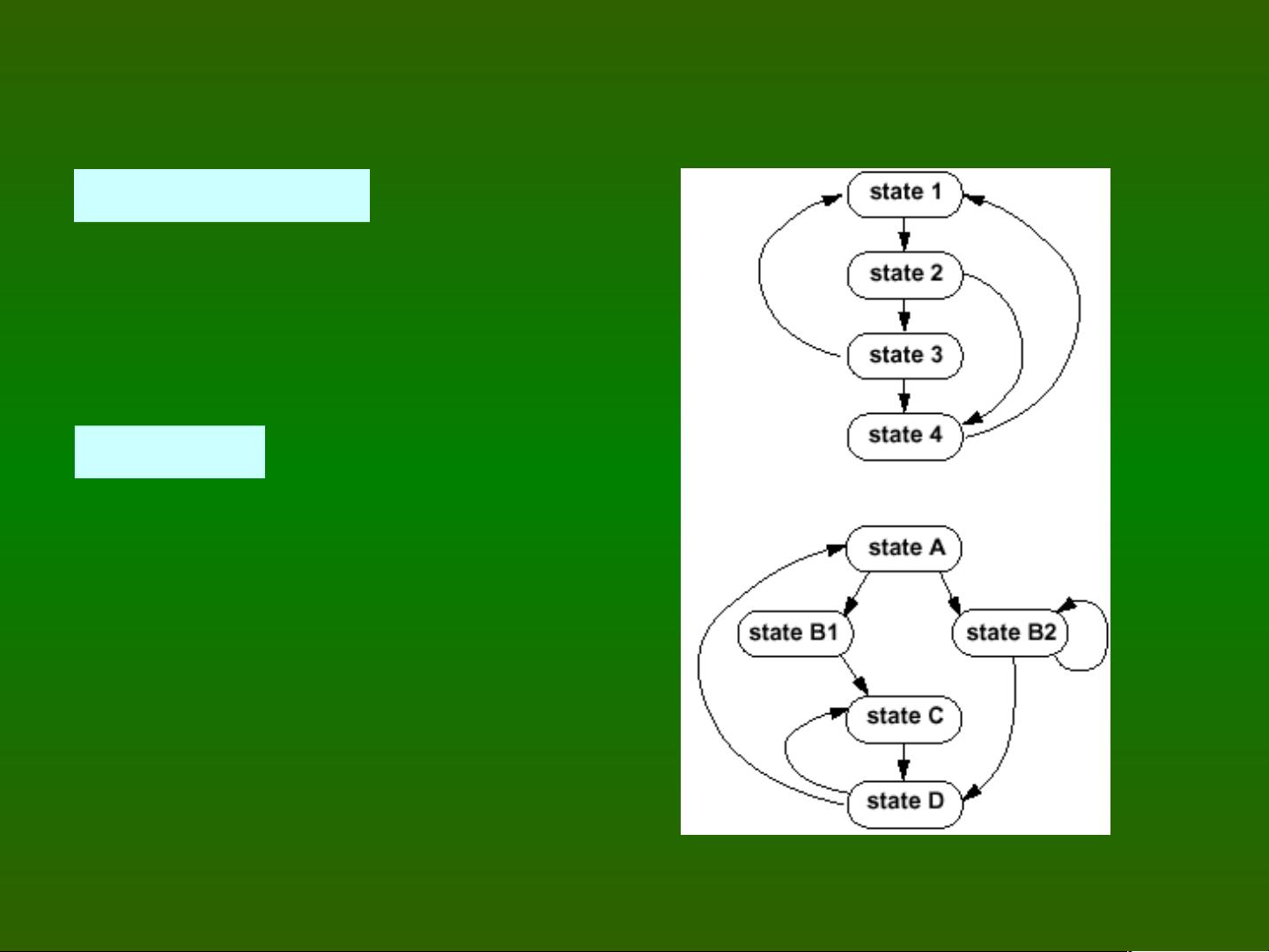

在数字系统设计中,状态机(Finite State Machine, FSM)扮演着至关重要的角色,它是一种能够根据当前状态和输入来决定下一个状态的逻辑控制单元。在本课程中,我们将深入探讨状态机的结构与设计方法,特别是如何利用硬件描述语言(如Verilog)进行实现。

有限状态机(FSM)是描述系统行为的一种模型,它可以用来表示系统在不同时间点的行为状态以及状态之间的转换。FSM由一组状态、一个当前状态、输入变量、状态转移条件和输出函数组成。在实际应用中,常见的状态机类型包括Moore型和Mealy型,两者的主要区别在于输出是否依赖于当前输入和当前状态。

设计状态机通常包括以下步骤:

1. 定义状态:首先,需要确定系统可能存在的所有状态,这些状态代表了系统在不同条件下的工作模式。

2. 描述状态转换:定义每个状态下,对于不同的输入,系统如何转移到其他状态。

3. 设计输出:根据当前状态和可能的输入,确定输出值。

4. 实现逻辑:使用硬件描述语言(如Verilog或VHDL)将状态机逻辑编码,通常会使用D触发器和组合逻辑来存储和更新状态。

5. 验证:通过仿真和测试,确保状态机按照预期工作。

在数字集成电路(IC)设计的面试和作业中,状态机设计是常见的考察点。例如,题目中提到的检测特定序列(如10010或101101)的状态机,或者设计交通信号灯控制器、自动饮料售卖机等,都需要运用状态机的概念。这些问题要求我们绘制状态图,然后用Verilog等语言实现,并且要满足FPGA设计的语法要求。

交通信号灯设计中,状态机需要管理红绿黄三种颜色的切换,考虑各种可能的定时和交互情况。自动饮料售卖机的设计则涉及到硬币识别、金额计算、饮料分发和找零等复杂逻辑,需要合理地定义状态并处理各种输入输出关系。

同步有限状态机是最常见的实现方式,它使用时钟信号来同步状态的改变。在一个时钟周期内,状态不会发生变化,只有在时钟上升沿到来时,输入信号才会被读取,状态才会根据输入和当前状态进行更新。这种设计避免了数据竞争和不确定性的风险,提高了系统的稳定性和可靠性。

状态机的设计对于理解和实现复杂数字系统至关重要。它们能够帮助我们以有序、模块化的方式组织逻辑,使得设计更容易理解、验证和调试。特别是在FPGA和ASIC设计中,状态机被广泛用于控制逻辑,实现高效的时序操作。通过熟练掌握状态机的原理和设计技巧,可以更高效地应对数字IC设计中的各种挑战。

点击了解资源详情

点击了解资源详情

点击了解资源详情

149 浏览量

2022-06-17 上传

2011-06-23 上传

516 浏览量

2022-06-20 上传

439 浏览量