多功能ALU设计实验:掌握Verilog HDL与运算器构建

需积分: 42 64 浏览量

更新于2024-09-03

1

收藏 148KB DOCX 举报

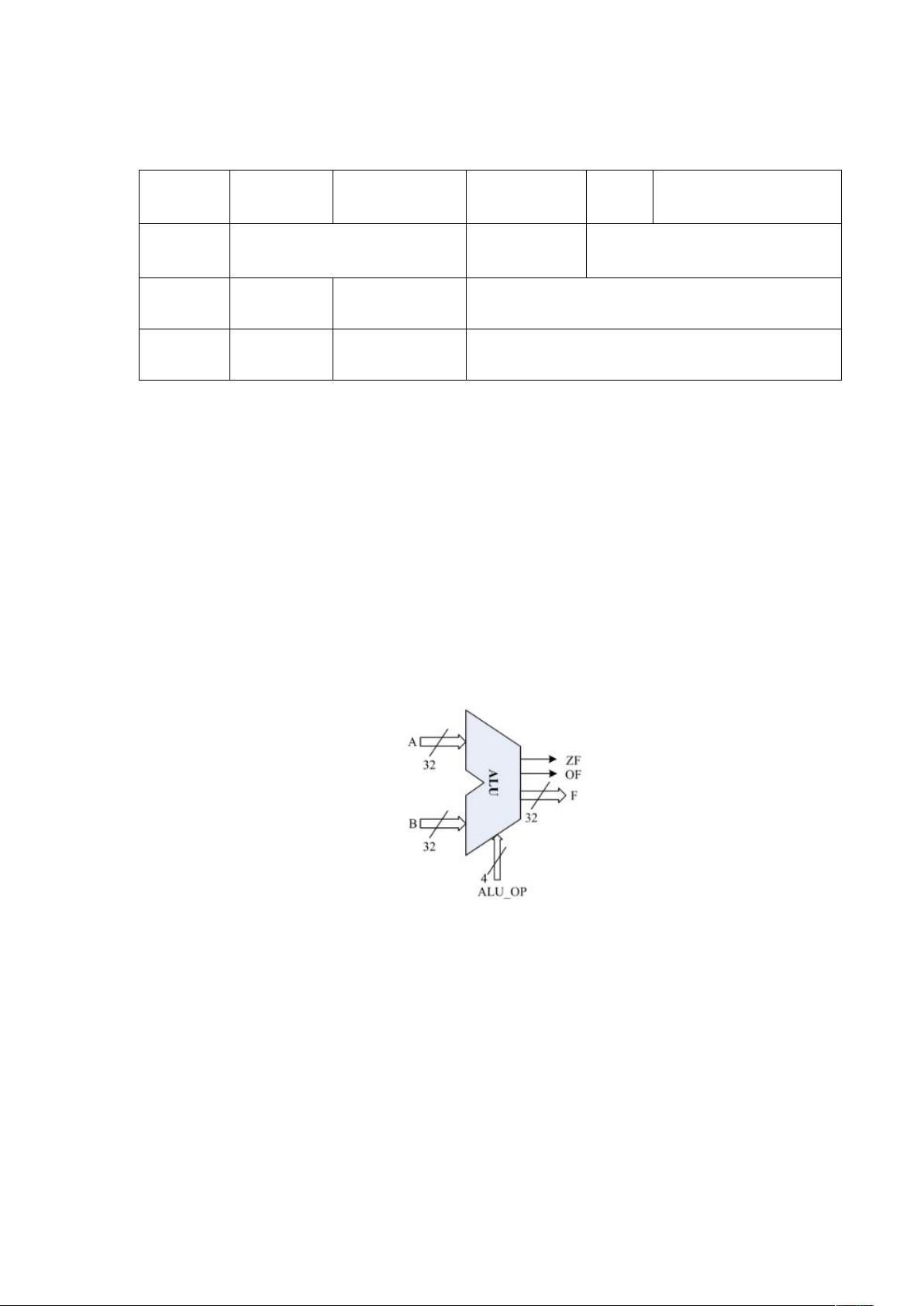

本次实验主要聚焦于多功能ALU的设计,目的是让学生深入理解运算器的工作原理和计算机组成原理中的ALU部分。参与者需利用Verilog HDL语言进行行为描述和建模,设计一个具备16种运算功能的32位ALU,其中包括加法、减法、逻辑与、逻辑或、逻辑异或等基本操作,以及产生结果标志ZF(零标志)和OF(溢出标志)。实验设计的ALU通过4位控制线ALU_OP[3:0]选择不同的运算功能,并且实验内容涵盖了逻辑电路图的绘制、功能模块说明、测试用例设计、仿真时序图的分析以及对实验结果的讨论。

实验的关键知识点包括:

1. **ALU工作原理**:ALU(算术逻辑单元)是运算器的核心组成部分,负责执行基本的算术和逻辑运算。它根据不同的控制信号选择不同的操作,如加法、减法、逻辑运算等。

2. **Verilog HDL应用**:通过Verilog语言,学生将学习如何描述ALU的行为,包括输入、输出信号的定义,以及控制信号如何影响运算过程。这是一种硬件描述语言,常用于数字系统设计。

3. **标志位处理**:实验着重于结果标志ZF和OF的设计,这两个标志用于检测运算结果的特性,例如是否为零和是否有溢出。对于无符号数和有符号数的处理,虽然硬件层面不区分,但在软件层面上,数据类型会影响处理方式。

4. **限制与挑战**:实验中提到,设计的ALU并不能实现MIPS核心指令集的所有功能,比如跳转、自减、置一和算数左移等,这表明在实际应用中,ALU设计可能需要扩展以满足更复杂的指令集需求。

5. **算术运算**:无符号数的逻辑右移和算数右移在硬件层面可通过相同操作表示,但需要编程逻辑来区分是否进行算数运算,而在MIPS架构中,算术左移由于末尾补零与逻辑左移相同,通常不单独作为一个操作。

6. **标志位的判断**:SF(符号标志)用于判断有符号数的运算结果,而PF(进位标志)通过统计1的个数来确定,C32在加减法中用于设置CF(进位标志),区分无符号运算和有符号运算的结果。

7. **溢出问题**:在处理无符号数时,可能会出现OF标志错误地显示为1的问题,这可能涉及到符号数运算条件的添加以解决这一问题。

最后,实验的附录提供了详细的源代码,展示了ALU模块的具体实现,这对于理解和实践ALU设计至关重要。整个实验不仅锻炼了学生的硬件设计能力,也加深了他们对计算机体系结构的理解。

2018-11-29 上传

2022-07-10 上传

316 浏览量

2020-04-24 上传

2020-09-29 上传

2021-07-18 上传

2021-11-25 上传

○_●

- 粉丝: 69

- 资源: 9

最新资源

- getting started with JBoss4.0 中文版

- SQL语法大全中文版(其中两章)

- 开源_200903.pdf

- C语言趣味程序百例精解

- 动态场景下的运动目标跟踪方法研究.pdf

- 英语词根词缀记忆大全

- DS1302_中文资料.pdf

- How to solve it: A new aspect of mathematical method

- 美国MIT EECS系本科生课程设置简介

- 小程序(在网页上找Email地址)

- C#完全手册(新手学习C#必备手册)

- 数字信号处理、计算、程序、

- 详细设计说明书案例.DOC

- 课程设计航空客运订票系统

- JSF自定义组件 JSF自定义组件

- Visual C++与Matlab混合编程