边缘到边缘PWE3:TDM电路仿真中的保真度与挑战

边缘到边缘的伪线仿真(PWE3),尤其是5. TDM电路仿真,是一种在分组交换网络(PSN)中模拟同步光网络(SONET)/同步数字体系(SDH)电路的技术。它通过Circuit Emulation Protocol (CEP) 实现,这是一种封装层协议,允许在PSN上处理SONET/SDH的同步信息流。当底层PSN是多协议标签交换(MPLS)网络时,CEP也可能被称为CEM。

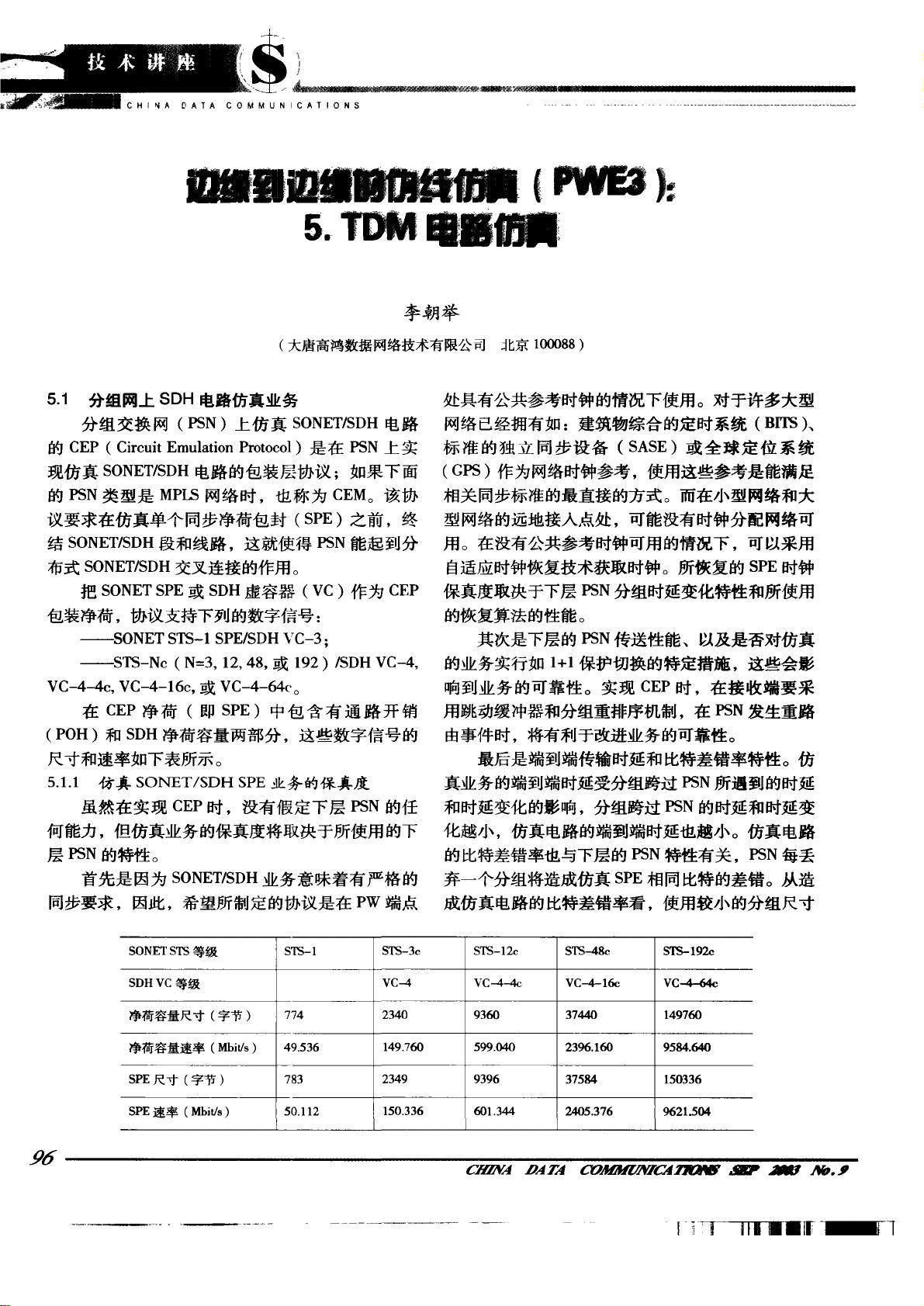

CEP的关键在于在仿真单个同步净荷包封(SPE)前完成SONET/SDH链路和线路的配置,这样PSN可以作为分布式SDH交叉连接。支持的数字信号包括不同等级的SONET STM-1 SPE/SDH VC、STM-Nc(N值不同)、SDH VC-4等,其中SPE中包含了路径开销(POH)和SDH净荷容量信息。

保真度是仿真业务的核心,依赖于底层PSN的特性。为了满足严格的同步要求,CEP期望在两端节点处有公共参考时钟,如BITS、SASE或GPS。在缺乏这些时钟的情况下,自适应时钟恢复技术可以用来确保SPE时钟的精度。PSN的传输性能、保护措施(如1+1备份切换)以及对抖动和丢包的管理都会影响业务的可靠性和保真度。

在接收端,为了提高可靠性,CEP采用了跳动缓冲器和分组重排序机制,能在PSN路由改变时快速调整。此外,端到端的传输时延和比特错误率也是衡量仿真电路质量的重要指标,网络中的延迟和延迟变化直接影响到仿真电路的性能。理想的网络设计应该尽可能减小分组穿越PSN时的延迟和波动,以实现低延迟和高质量的仿真服务。

总结来说,边缘到边缘的PWE3 TDM电路仿真是一种复杂的技术,它结合了分组网络的灵活性与SDH的严谨性,通过精确的时间同步和有效的协议设计,确保在异构网络环境中提供高质量的SDH业务仿真。

2022-10-29 上传

2022-10-29 上传

2021-01-10 上传

2021-09-19 上传

2024-06-23 上传

点击了解资源详情

点击了解资源详情

taylor3766

- 粉丝: 2

- 资源: 6

最新资源

- IEEE 802.16入网退避算法的设计

- iso C99 standard

- MiniGUI编程指南

- 计算机操作系统(汤子瀛)习题答案

- 《构建高性能Web站点》节选 - 动态脚本加速 - 避免重复编译.pdf

- D语言参考文档,第二版

- 民航订票系统 软件工程

- Oracle Database 10g - DBA

- S3C2410 linux 移植中文手册

- Java语言编码规范(pdf)

- D语言参考手册,第一版

- Data Mining: Practical Machine Learning Tools and Techniques

- jms规范教程,JMS相当的技术规范

- MPEG数字视音频压缩编码原理及应用

- 2008年网络原理试题

- 图形学实验题目(08年)