0.25μm BiCMOS工艺下的高性能全差分S/H电路设计及仿真

73 浏览量

更新于2024-08-31

1

收藏 266KB PDF 举报

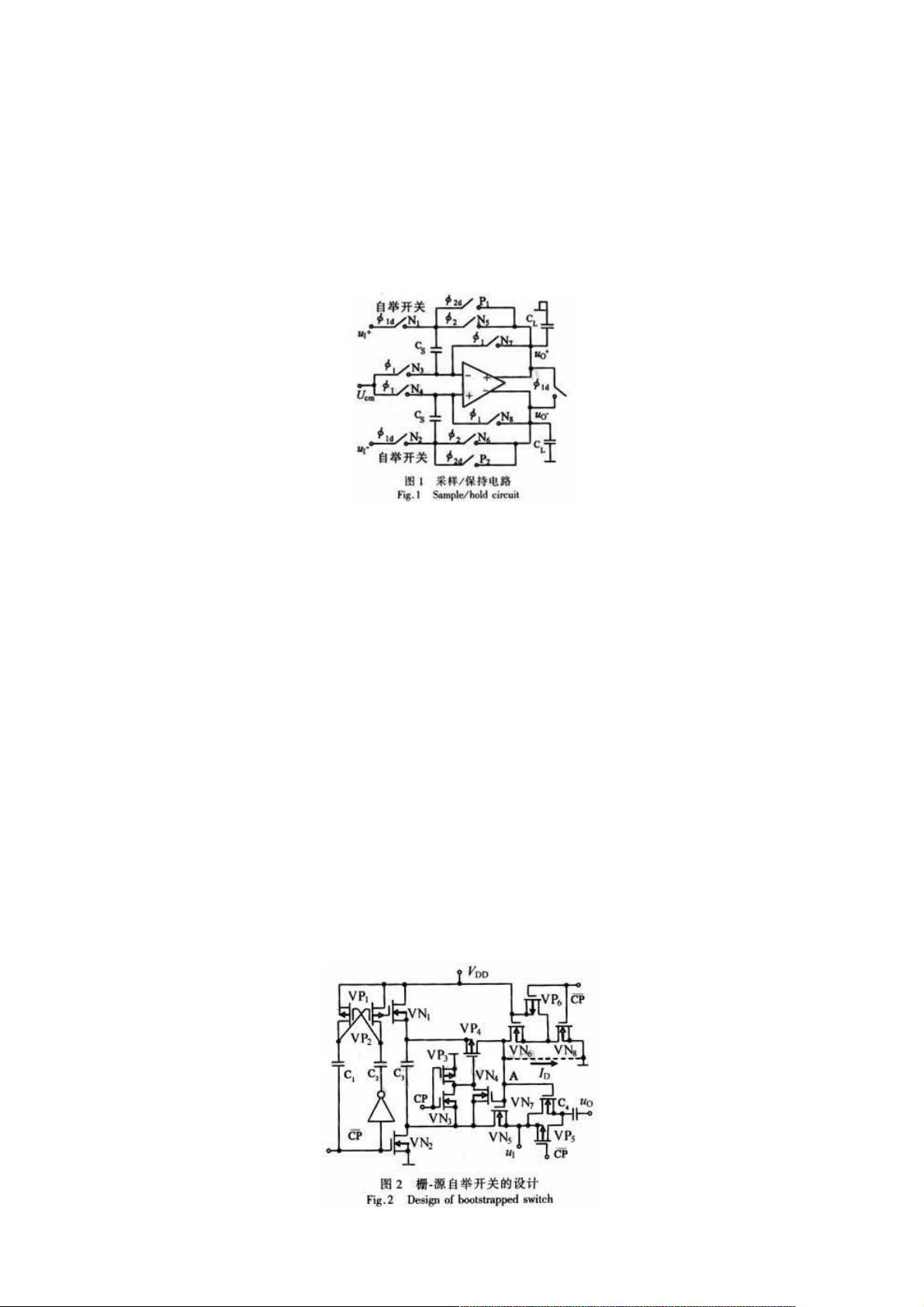

本文主要探讨的是全差分BiCMOS采样保持电路的仿真设计,针对传统模拟/数字转换器(S/H)电路存在的失真问题和静态工作点稳定性不足,作者采用了先进的0.25μm BiCMOS工艺,旨在构建一款高性能的10位全差分电路。设计的关键创新点在于改进型自举开关电路和双通道开关电容共模反馈电路(CMFB)。

在电路结构方面,作者参照了S/H电路的基本架构,通过自举开关N1和N2以及NMOS开关N3~N8来实现采样和保持功能。自举开关设计巧妙地避免了开关动作时对输入信号的干扰,通过调整时钟信号的控制,确保开关在线性区工作,从而减少失真。此外,通过下极板采样技术和合适的时间常数RC的选择,提升了电路的采样速率。

针对输入端的栅-源自举开关,设计者特别注意到了CMOS开关非线性特性可能导致的信号失真和幅度波动。通过设计成自举开关形式,保持栅-源电压在VDD范围内,有效地减小了导通电阻的非线性变化,从而最大限度地降低了失真,提高了电路的连续时间信号采样能力。

双通道开关电容共模反馈电路(CMFB)的作用在于抑制共模噪声,保证输出信号的精度。其创新性体现在它能够通过两个独立的反馈通道,有效地平衡电路的动态性能和稳定性,这对于高性能的ADC来说至关重要。

这篇论文不仅介绍了全差分BiCMOS采样保持电路的理论基础,还详细阐述了关键组件的设计策略和技术优化,为模拟/数字转换器的高性能设计提供了有价值的技术解决方案。通过仿真验证,这种设计有望显著提升电路的性能指标,为电子电路设计与仿真领域带来新的突破。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-01-20 上传

2020-11-07 上传

2020-10-23 上传

2020-10-19 上传

2021-02-03 上传

点击了解资源详情

weixin_38730201

- 粉丝: 5

- 资源: 922

最新资源

- 开源数据结构:全球开源项目中使用的数据结构

- quiron:Modulo QtQuick para cargar en Unik Qml Engine-Modulo deaplicaciónpara Ayuda Memoria de DatosAstrológicos

- accyrding-policy-aloha.zip_TreeView控件_Visual_Basic_

- LogKyrcach

- 算法和数据结构:使用JavaScript实现的常见排序算法,数据结构和其他算法挑战的交互式概述

- led发光管(PE).rar_嵌入式/单片机/硬件编程_C/C++_

- 用于读取和写入图像数据的Python库-Python开发

- 第十三届中国大学生服务外包创新创业大赛-A08基于 FPGA 的铝片表面工业缺陷检测系统

- gdxextras:Libgdx的一些额外工具

- clean-undefined:删除未定义的对象字段

- Women-in-Big-Data-South-Africa:本笔记本介绍了Zindi竞赛(南非大数据中的女性-南非女性为户主的家庭)。 我们将快速浏览数据,展示如何创建模型,估算您在Zindi上获得的得分,准备提交并进入排行榜。 我还提供了一些有关如何获得更高分数的提示-一旦您第一次提交,这些都可能给您一些下一步尝试的想法

- 正方教务通用安卓

- libradio-开源

- 数据结构算法:此存储库包括我在本科期间所做的数据结构程序和算法。 这些是我自己用C ++从头开始编写的功能齐全的算法。 -要求:Microsoft Visual Studio 2019-打开sln文件以打开整个项目

- lilt:Lilt终端模拟器-用于Linux,macOS和其他类似Unix的系统的简单便携式终端模拟器

- siptapi-开源