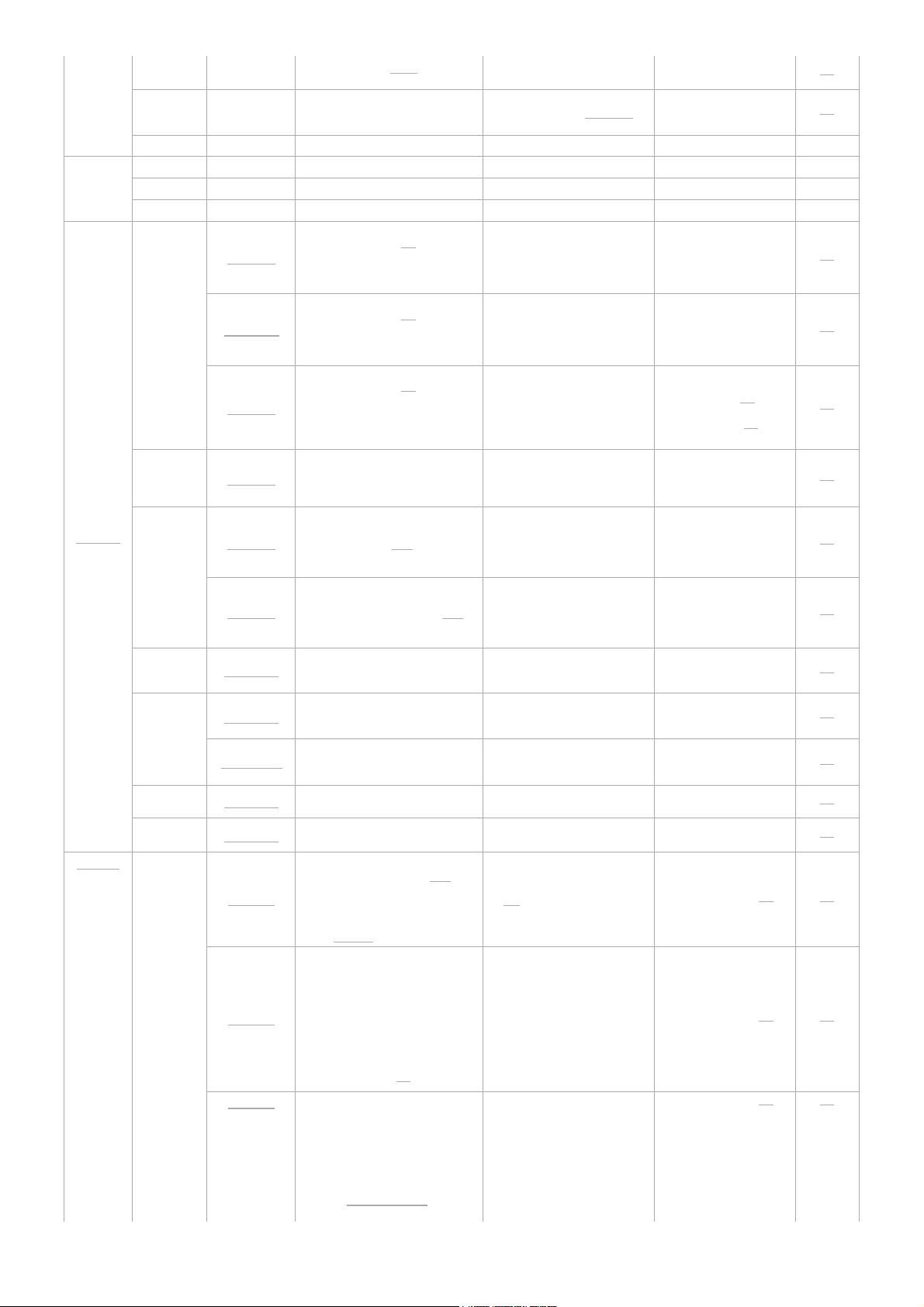

ARMv6T2

ARM1156T2(F)-

S

9-stage pipeline, SIMD, Thumb-2,

(VFP), enhanced DSP instructions

Variable, MPU

[10]

ARMv6Z

ARM1176JZ(F)-

S

As ARM1136EJ(F)-S Variable, MMU + TrustZone

965 DMIPS @ 772 MHz,

up to 2,600 DMIPS with

four processors

[11]

ARMv6K ARM11MPCore As ARM1136EJ(F)-S, 1–4 core SMP Variable, MMU

SecurCore

ARMv6-M SC000 As Cortex-M0 0.9 DMIPS/MHz

ARMv4T SC100 As ARM7TDMI

ARMv7-M SC300 As Cortex-M3 1.25 DMIPS/MHz

Cortex-M

ARMv6-M

Cortex-M0

Microcontroller profile, most Thumb

+ some Thumb-2,

[12]

hardware

multiply instruction (optional small),

optional system timer, optional bit-

banding memory

Optional cache, no TCM, no

MPU

0.84 DMIPS/MHz

[13]

Cortex-M0+

Microcontroller profile, most Thumb

+ some Thumb-2,

[12]

hardware

multiply instruction (optional small),

optional system timer, optional bit-

banding memory

Optional cache, no TCM, optional

MPU with 8 regions

0.93 DMIPS/MHz

[14]

Cortex-M1

Microcontroller profile, most Thumb

+ some Thumb-2,

[12]

hardware

multiply instruction (optional small),

OS option adds SVC / banked stack

pointer, optional system timer, no bit-

banding memory

Optional cache, 0–1024 KB I-

TCM, 0–1024 KB D-TCM, no

MPU

136 DMIPS @

170 MHz,

[15]

(0.8 DMIPS/MHz FPGA-

dependent)

[16]

[17]

ARMv7-M Cortex-M3

Microcontroller profile, Thumb /

Thumb-2, hardware multiply and

divide instructions, optional bit-

banding memory

Optional cache, no TCM, optional

MPU with 8 regions

1.25 DMIPS/MHz

[18]

ARMv7E-M

Cortex-M4

Microcontroller profile, Thumb /

Thumb-2 / DSP / optional VFPv4-SP

single-precision FPU, hardware

multiply and divide instructions,

optional bit-banding memory

Optional cache, no TCM, optional

MPU with 8 regions

1.25 DMIPS/MHz (1.27

w/FPU)

[19]

Cortex-M7

Microcontroller profile, Thumb /

Thumb-2 / DSP / optional VFPv5

single and double precision FPU,

hardware multiply and divide

instructions

0−64 KB I-cache, 0−64 KB D-

cache, 0–16 MB I-TCM, 0–16 MB

D-TCM (all these w/optional

ECC), optional MPU with 8 or 16

regions

2.14 DMIPS/MHz

[20]

ARMv8-M

Baseline

Cortex-M23

Microcontroller profile, Thumb-1

(most), Thumb-2 (some), Divide,

TrustZone

Optional cache, no TCM, optional

MPU with 16 regions

1.03 DMIPS/MHz

[21]

ARMv8-M

Mainline

Cortex-M33

Microcontroller profile, Thumb-1,

Thumb-2, Saturated, DSP, Divide,

FPU (SP), TrustZone, Co-processor

Optional cache, no TCM, optional

MPU with 16 regions

1.50 DMIPS/MHz

[22]

Cortex-M35P

Microcontroller profile, Thumb-1,

Thumb-2, Saturated, DSP, Divide,

FPU (SP), TrustZone, Co-processor

Built-in cache (with option 2–

16 KB), I-cache, no TCM,

optional MPU with 16 regions

1.50 DMIPS/MHz

[23]

ARMv8.1-M

Mainline

Cortex-M55 1.69 DMIPS/MHz

[24]

ARMv8.1-M

Mainline

Cortex-M85 3.13 DMIPS/MHz

[25]

Cortex-R ARMv7-R

Cortex-R4

Real-time profile, Thumb / Thumb-2 /

DSP / optional VFPv3 FPU,

hardware multiply and optional divide

instructions, optional parity & ECC

for internal buses / cache / TCM, 8-

stage pipeline dual-core running

lockstep with fault logic

0–64 KB / 0–64 KB, 0–2 of 0–

8 MB TCM, opt. MPU with 8/12

regions

1.67 DMIPS/MHz

[26] [27]

Cortex-R5

Real-time profile, Thumb / Thumb-2 /

DSP / optional VFPv3 FPU and

precision, hardware multiply and

optional divide instructions, optional

parity & ECC for internal buses /

cache / TCM, 8-stage pipeline dual-

core running lock-step with fault

logic / optional as 2 independent

cores, low-latency peripheral port

(LLPP), accelerator coherency port

(ACP)

[28]

0–64 KB / 0–64 KB, 0–2 of 0–

8 MB TCM, opt. MPU with 12/16

regions

1.67 DMIPS/MHz

[26] [29]

Cortex-R7 Real-time profile, Thumb / Thumb-2 /

DSP / optional VFPv3 FPU and

precision, hardware multiply and

optional divide instructions, optional

parity & ECC for internal buses /

cache / TCM, 11-stage pipeline dual-

core running lock-step with fault

logic / out-of-order execution /

dynamic register renaming / optional

0–64 KB / 0–64 KB, ? of 0–

128 KB TCM, opt. MPU with 16

regions

2.50 DMIPS/MHz

[26] [30]