基于EDA的模可变计数器设计与数码管显示

"该资源是一份关于模可变计数器设计的实验教程,主要涉及EDA技术、Quartus II软件使用以及PH-1V型实验装置操作。实验目标是通过设计不同模值的计数器(模23和模109),并利用静态数码管显示结果,学习多层次设计方法。实验设计分为计数部分、功能选择和数码管显示三个阶段。关键步骤是将二进制计数结果转换为十进制BCD码以供数码管显示,可以使用IEEE库中的conv_std_logic_vector函数进行转换。实验程序中定义了实体CNTM1,包含输入时钟、复位、使能、功能选择位和输出数码显示。在架构中,根据M信号选择不同的计数模式,并通过进程处理时钟上升沿触发的计数更新。"

在电子设计自动化(EDA)领域,模可变计数器是一种灵活的计数设备,其计数值可以根据输入的控制信号进行改变。本实验以模23和模109为例,通过VHDL语言实现,这是一种硬件描述语言,用于描述数字系统的逻辑功能。实验要求学生熟悉Quartus II,这是Altera公司的一款综合开发软件,广泛用于FPGA(现场可编程门阵列)设计。

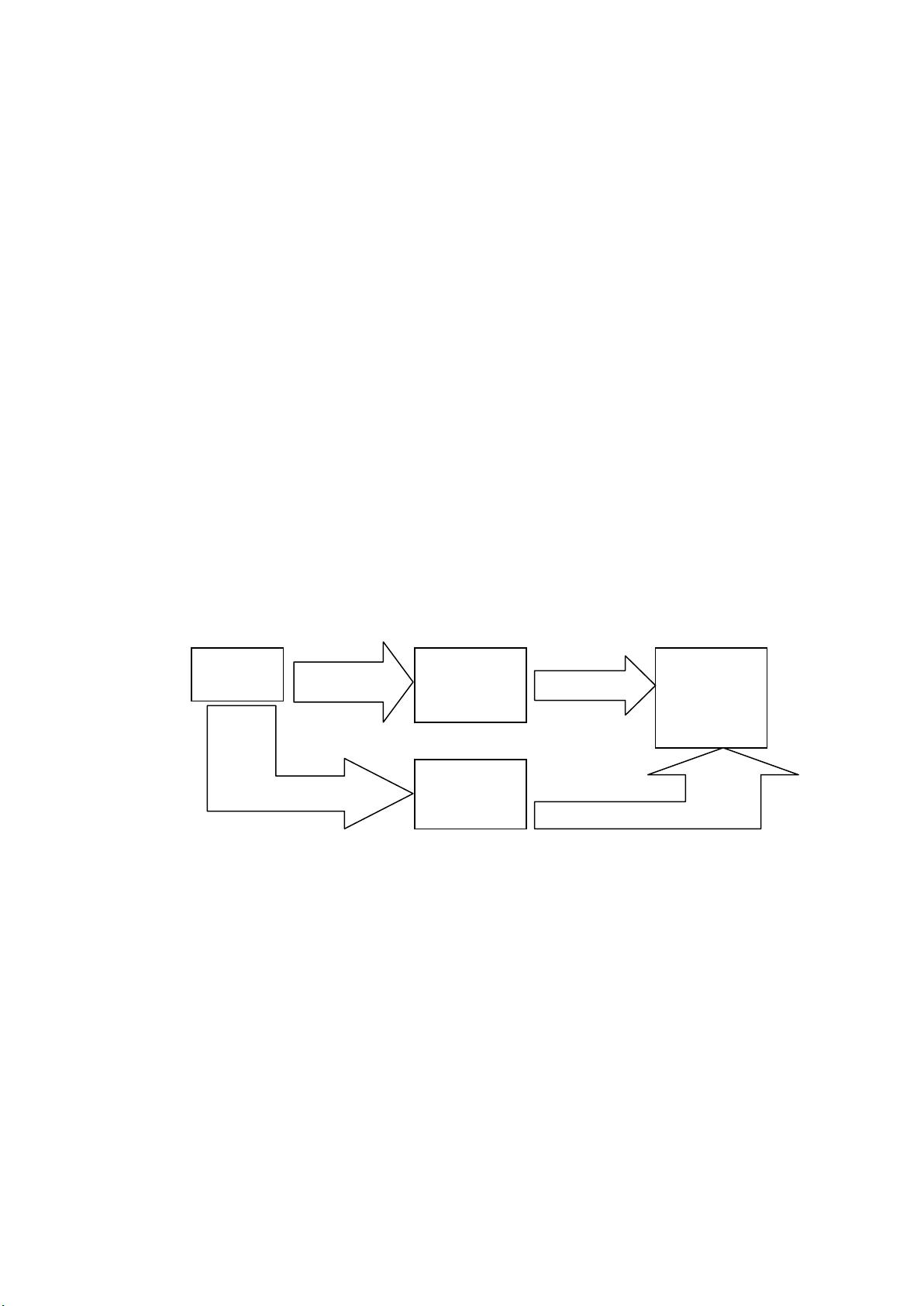

实验设计中,首先需要设计两个独立的计数器,一个用于模23计数,另一个用于模109计数。这些计数器可能使用加法器和移位寄存器等基本逻辑单元构建,通过累加或移位操作达到指定的模值。当控制信号M为0时,计数器执行模23计数,当M为1时,则执行模109计数。

数码管显示部分需要将计数器的二进制输出转换为十进制的BCD码。通常,数码管显示单元只能接受特定的BCD码格式输入,因此需要进行译码。在VHDL中,可以使用conv_std_logic_vector函数将整数转换为对应的位矢量,便于驱动数码管。实验程序中的PROCESS结构用于处理时钟边沿触发的计数逻辑,变量N用来存储当前计数值,并根据M的值选择执行相应的计数路径。

这个实验不仅涵盖了硬件设计的基本概念,还涉及到高级设计技巧,如多层次设计和条件分支,对于提升学生的数字系统设计能力和实践技能具有重要意义。通过这样的实践,学生能够深入理解硬件描述语言的运用,以及如何在实际项目中应用EDA工具。

相关推荐

146 浏览量

366 浏览量

1691 浏览量

131 浏览量

2025-04-03 上传

2025-04-03 上传

chewbee88

- 粉丝: 0

最新资源

- VisualSVN Server 4.1:高效SVN服务端解决方案

- 航海主题卧室3D模型设计指南

- LPF壁纸小精灵:易语言实现自动更换壁纸工具

- MAZeroingWeakRef:Objective-C零引用弱引用处理库

- 可编辑PPT柱形图模板下载

- 掌握物流采购核心:高效库存预测方法

- Unity3D 8-Bit风格特效粒子系统教程

- 探索Malina_Chat开源聊天系统的源代码

- 基于周立功CAN示例的USBCAN简易DEMO教程

- 易语言LOGO海龟画图v0_8简易教程与工具下载

- 易语言实现查找指定颜色的自动化移动鼠标例程

- 探索Atom编辑器中ProS开发插件的核心优势

- 现代物流管理基础模拟试卷参考指南

- 彩色圆形层级关系PPT模板-创意视觉展示

- Unity3D平台高效粒子特效制作神器

- 书房3D模型设计:实现完美书房模拟