FPGA实现的PLL频率合成器:整数/半整数频率源

80 浏览量

更新于2024-09-01

收藏 245KB PDF 举报

"基于FPGA的PLL频率合成器设计,实现了1 kHz至999.5 kHz的输出,步进精度0.5 kHz,适用于教学实验和频率源用途。使用了FPGA、PLL技术和CD4046锁相环芯片。系统通过FPGA控制分频并接收键盘输入设定分频系数,实现频率合成。"

本文介绍了一种基于FPGA(Field-Programmable Gate Array)的PLL(Phase-Locked Loop)频率合成器设计,特别适合教学实验环境。PLL频率合成技术是电子系统中不可或缺的部分,它允许通过基础频率生成精确且稳定的任意频率。与传统实验设备相比,该系统在性能和用户友好性上有所提升,不仅可作为教学工具,还能作为频率源或频率计使用。

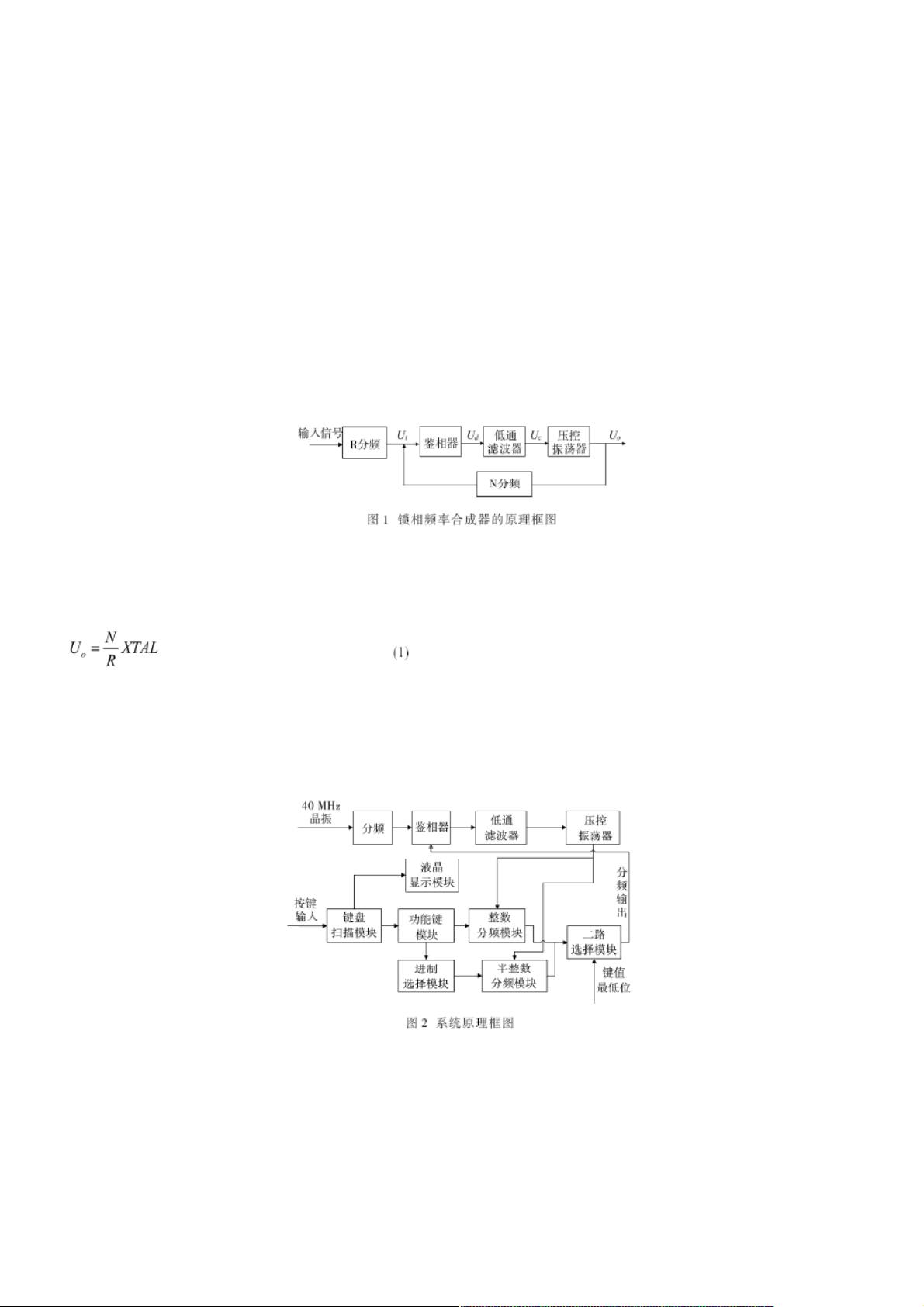

PLL频率合成器主要由鉴相器、环路滤波器和压控振荡器(VCO)等组件构成。鉴相器比较输入参考频率与VCO输出频率之间的相位差,产生的误差信号通过环路滤波器处理后调整VCO的控制电压,从而使VCO输出频率锁定在输入参考频率的整数或半整数倍。文章中采用了集成锁相环芯片CD4046,配合FPGA实现这一功能。

设计中,FPGA EPF10K10LC84-4扮演了核心角色,控制40MHz有源晶振的分频,产生1kHz基准信号供CD4046使用。同时,FPGA还接收来自键盘的输入,这些键值作为分频系数,用于整数和半整数分频模块,从而实现所需的输出频率。系统原理图显示,VCO输出信号直接进入这两个分频模块,以生成所需频率。

该系统的优势在于其灵活性和可编程性,使得频率合成可以根据实验需求进行定制。通过键盘输入,学生可以直观地理解频率合成的过程,并进行不同频率的设置,这对于理解和掌握PLL工作原理以及FPGA的应用具有极大的教学价值。此外,由于输出频率范围宽、步进精度高,该系统在实际工程应用中也具有一定的实用性。

基于FPGA的PLL频率合成器设计结合了现代数字技术与传统的锁相环技术,为教育和研究提供了强大而灵活的工具,同时也展现了FPGA在频率合成领域的潜力和应用前景。

163 浏览量

161 浏览量

2010-03-30 上传

462 浏览量

161 浏览量

163 浏览量

2021-07-13 上传

2010-03-23 上传

115 浏览量

weixin_38719643

- 粉丝: 7

- 资源: 941

最新资源

- waterGame

- angular-trianglify-animate:Angular Trianglify Animate 是一个很小的 (2kb) 插件,用于为您的页面添加对图像 SVG 动画的支持

- malg-cheong:부산대

- CSE316

- 2ALIENTEK 产品资料.rar

- 艾蒙坎

- 2020policebrutality:2020年警察暴行数据的Web界面

- 高端的婚纱摄影前端网页模板.zip

- idea-prado-plugin:PRADO框架对IntelliJ IDEAPHPStorm的支持

- RF++-开源

- show-action-sheet.zip

- 词法分析 编译原理实验/课程设计(C++实现)

- 影刀RPA系列公开课6:内容简介.rar

- 零基础入门CV数据集-数据集

- elec-market:电力批发市场的典范

- demo_spring_security.zip