单周期MIPS处理器设计与实现

需积分: 0 163 浏览量

更新于2024-06-30

收藏 1.37MB DOCX 举报

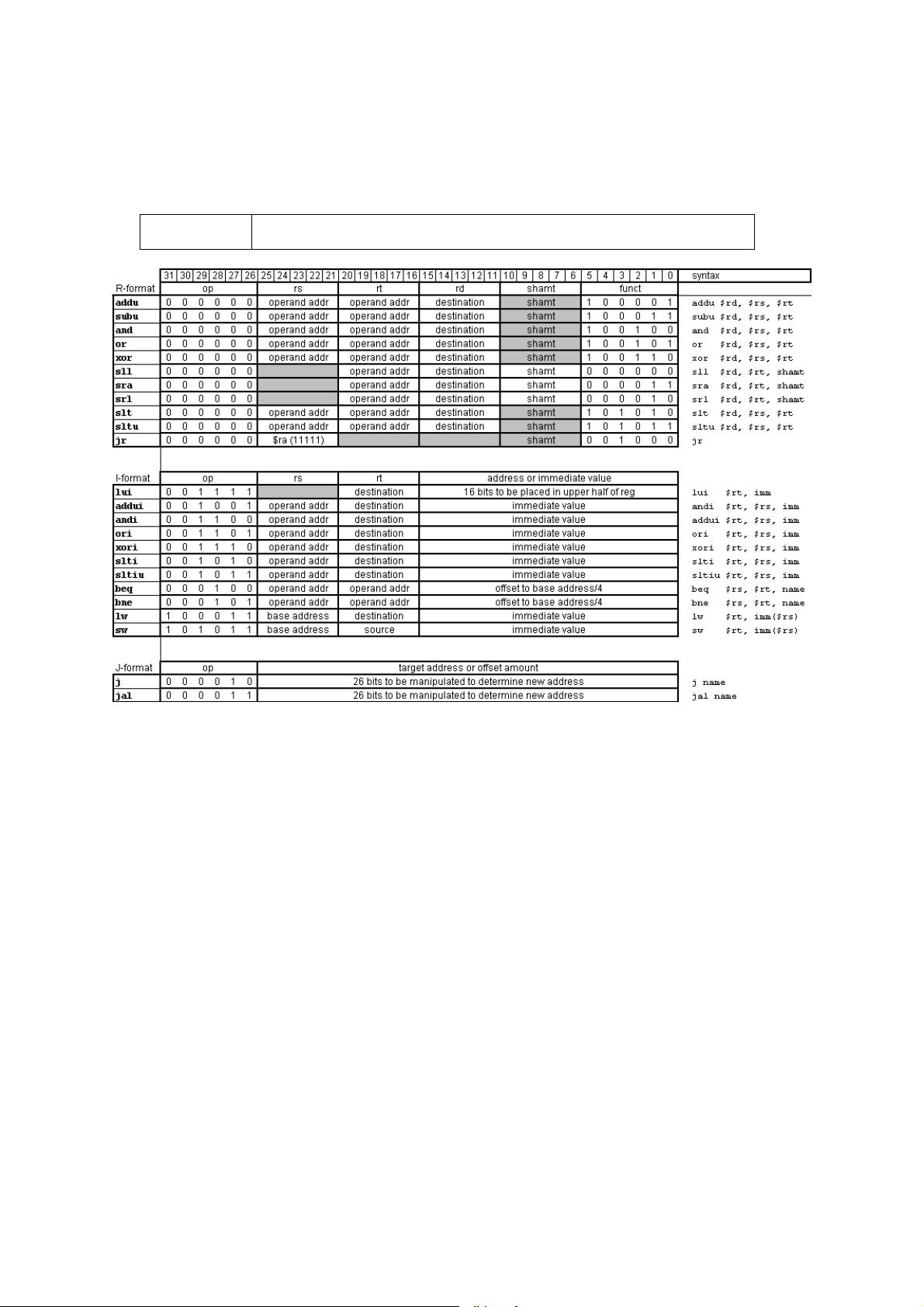

"本次实验是关于单周期MIPS处理器的设计与实现,由任野坤完成,指导教师为邢建国。实验旨在让学生理解并掌握单周期MIPS处理器的工作原理、实现方式以及指令与处理器的关联,并学会如何测试处理器的正确性。实验内容包括设计一个能够执行特定指令集的单周期MIPSCPU,这些指令涵盖算术运算、逻辑运算、移位和比较,以及存储器读写和分支操作。"

在单周期MIPS处理器的设计中,数据流图(Datapath)是一个关键部分,它描述了处理器内部各个组件如寄存器、算术逻辑单元(ALU)、控制单元等之间的数据流动和操作顺序。实验者需要理解和构建这样一个数据流图,以确保处理器能够按照预定步骤执行指令。

实验的焦点在于代码实现,即用硬件描述语言(HDL)如VHDL或Verilog来模拟和实现单周期MIPS处理器。例如,指令译码阶段(ID),在这个阶段,处理器会解析指令并决定接下来要执行的操作。在给出的指令集中,`addrd, rs, rt`指令用于将寄存器`rs`和`rt`的值相加,结果存入`rd`寄存器。`addirt, rs, immediate`则是将`rs`与立即数扩展后的`immediate`相加,结果存入`rt`。`subrd, rs, rt`指令执行减法操作,`orirt, rs, immediate`、`andrd, rs, rt`和`orrd, rs, rt`分别执行逻辑或、逻辑与和逻辑或操作。移位指令如`sllrd, rt, sa`将`rt`左移`sa`位,而`sltrd, rs, rt`进行带符号的比较,如果`rs`小于`rt`则`rd`设为1,否则设为0。

存储器读/写指令`swrt, immediate(rs)`和`lwrt, immediate(rs)`涉及到内存访问。前者将`rt`寄存器的值存储到地址为`rs + (sign-extend)immediate`的地方,后者从该地址读取数据并放入`rt`寄存器。分支指令`beqrs, rt, Immediate`实现条件跳转,当`rs`等于`rt`时,程序计数器(PC)会根据`Immediate`更新,实现分支。

测试单周期MIPS处理器的方法通常包括编写测试程序,该程序包含各种类型的指令,通过检查处理器执行后寄存器和内存的状态来验证其正确性。此外,还可以使用仿真工具对设计进行模拟运行,观察其行为是否符合预期。

这个实验不仅锻炼了学生在硬件层面理解和实现处理器的能力,也加深了他们对计算机体系结构中指令集和处理器之间关系的理解。通过这样的实践,学生能够更好地掌握计算机系统的基础工作原理。

2025-03-12 上传

2025-03-12 上传

ask_ai_app

- 粉丝: 24

最新资源

- 《ASP.NET 4.5 高级编程第8版》深度解读与教程

- 探究MSCOMM控件在单文档中的兼容性问题

- 数值计算方法在复合材料影响分析中的应用

- Elm插件支持Snowpack项目:热模块重载功能

- C++实现跨平台静态网页服务器

- C#开发的ProgaWeatherHW气象信息处理软件

- Memory Analyzer工具:深入分析内存溢出问题

- C#实现文件批量递归修改后缀名工具

- Matlab模拟退火实现经济调度问题解决方案

- Qetch工具:无比例画布绘制时间序列数据查询

- 数据分析技术与应用:Dataanalys-master深入解析

- HyperV高级管理与优化使用手册

- MTK6513/6575智能机主板下载平台

- GooUploader:基于SpringMVC和Servlet的批量上传解决方案

- 掌握log4j.jar包的使用与授权指南

- 基础电脑维修知识全解析