Rev. 1.3 17

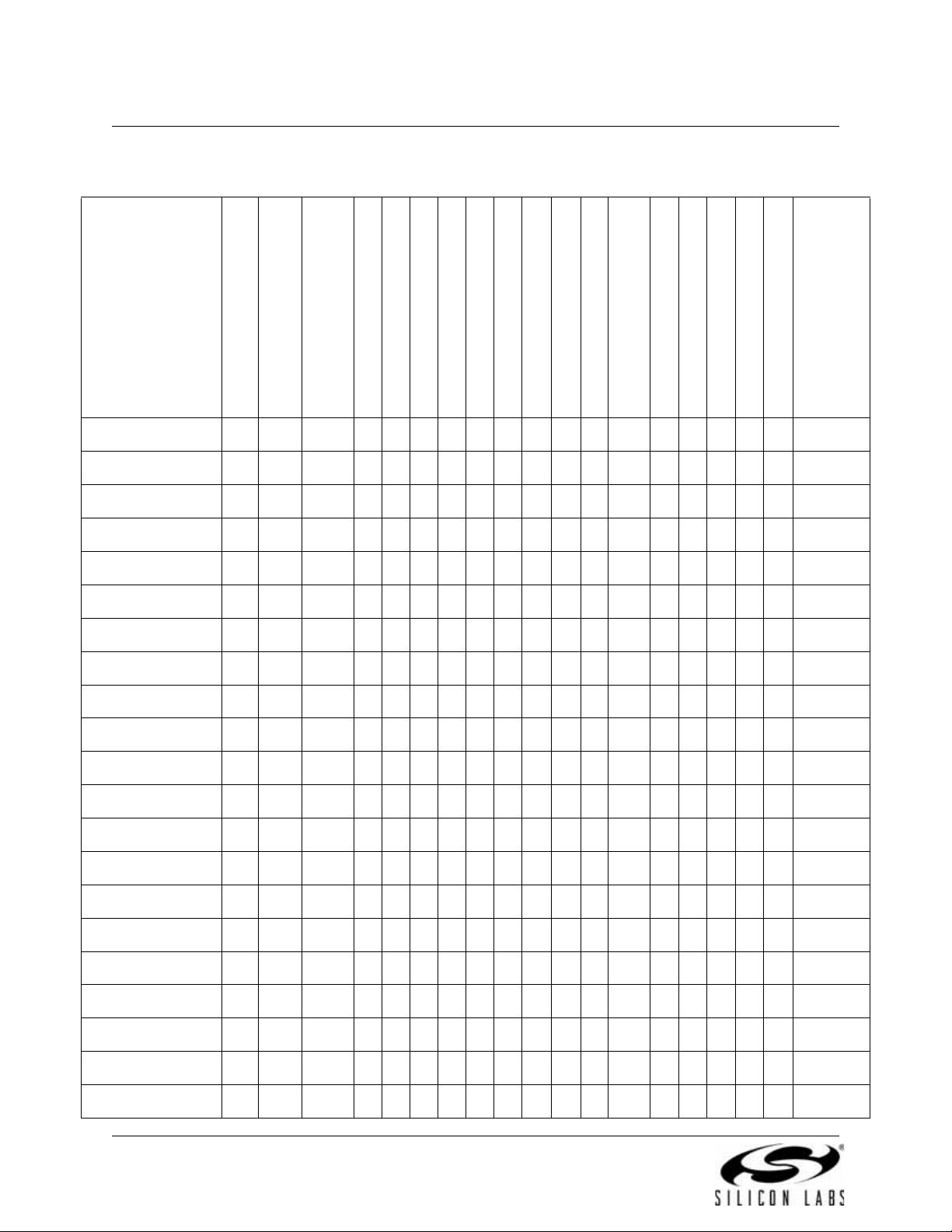

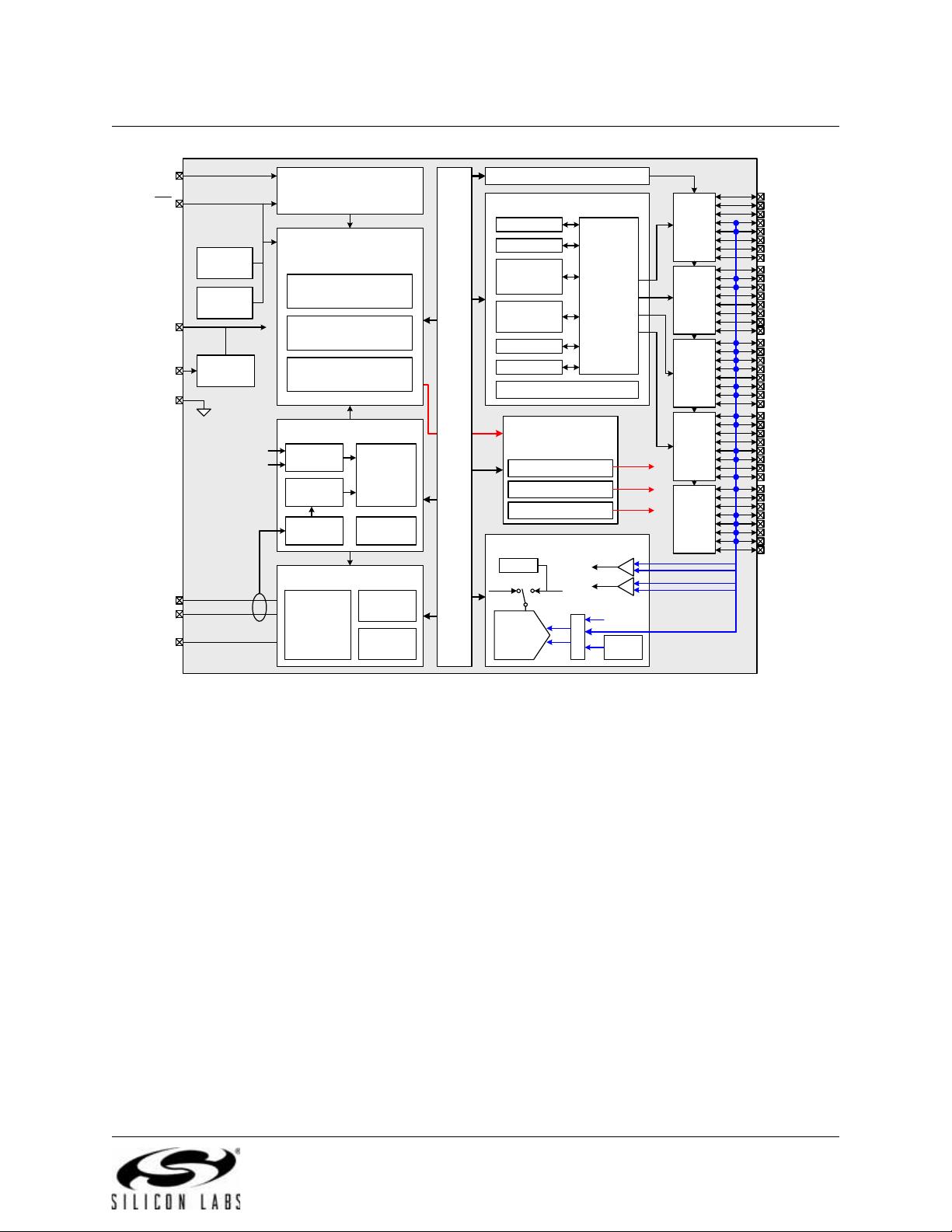

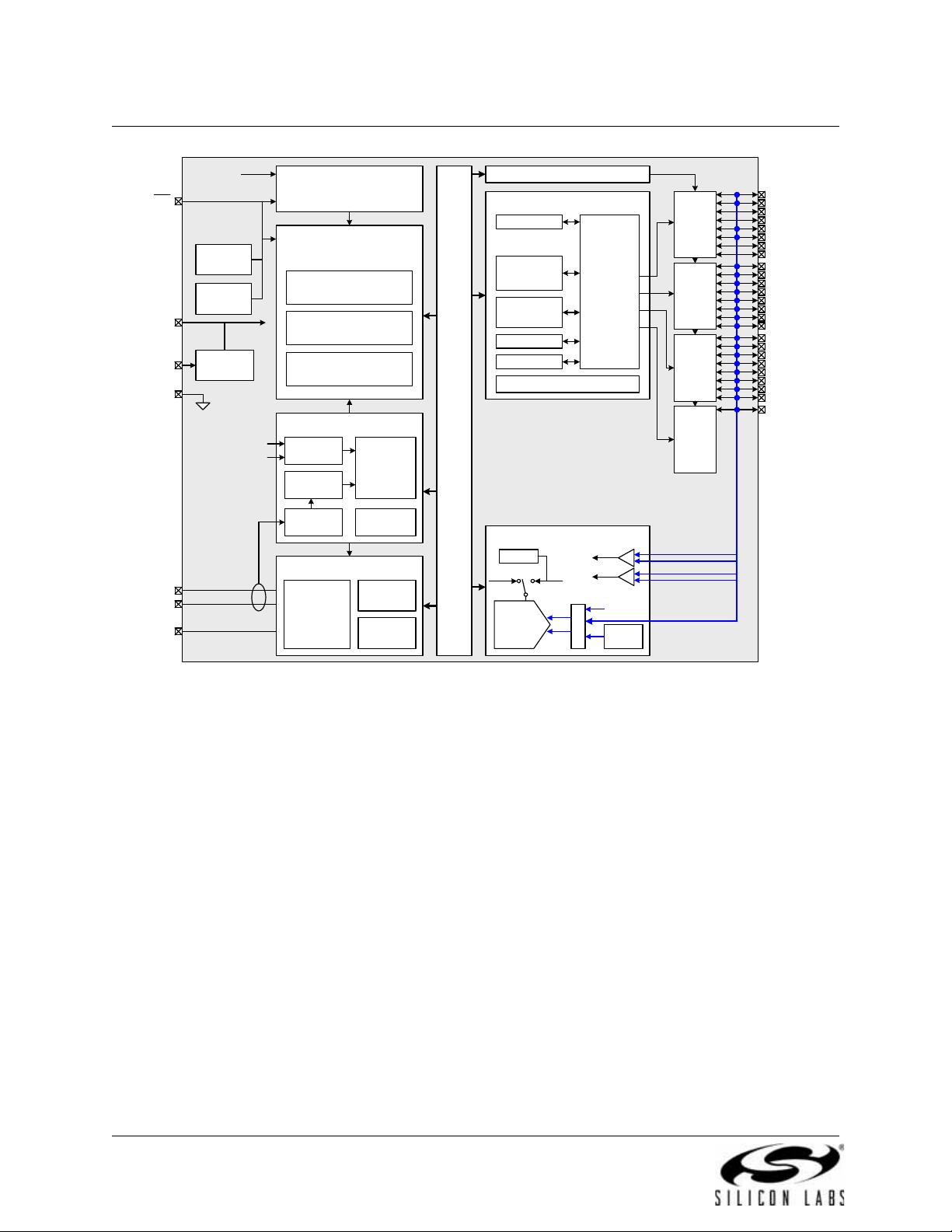

C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D

1. System Overview

C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D devices are fully integrated mixed-signal System-on-a-Chip MCUs.

Highlighted features are listed below. Refer to Table 1.1 for specific product feature selection.

• High-speed pipelined 8051-compatible microcontroller core (up to 48 MIPS)

• In-system, full-speed, non-intrusive debug interface (on-chip)

• Universal Serial Bus (USB) Function Controller with eigh

t flexible endpoint pipes, integrated trans-

ceiver, and 1 kB FIFO RAM

• Supply Voltage Regulator

• True 10-bit 200 ksps differential / single-ended AD

C with analog multiplexer

• On-chip Voltage Reference and Temperature Sensor

• On-chip Voltage Comparators (2)

• Precision internal calibrated 12 MHz internal oscillator and 4x clock multiplier

• Internal low-frequency oscillator for additional pow

er savings

• Up to 64 kB of on-chip Flash memory

• Up to 4352 Bytes of on-chip RAM (256 + 4 kB)

• External Memory Interface (EMIF) available on 48-pin versions.

• SMBus/I2C, up to 2 UARTs, and Enhanced SPI ser

ial interfaces implemented in hardware

• Four general-purpose 16-bit timers

• Programmable Counter/Timer Array (PCA) with five capture/compare modules and Watchdog Timer

func

tion

• On-chip Power-On Reset, V

DD

Monitor, and Missing Clock Detector

• Up to 40 Port I/O (5 V tolerant)

With on-chip Power-On Reset,

V

DD

monitor, Voltage Regulator, Watchdog Timer, and clock oscillator,

C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D devices are truly stand-alone System-on-a-Chip solutions. The

Flash memory can be reprogrammed in-circuit, providing non-volatile data storage, and also allowing field

upgrades of the 8051 firmware. User software has complete control of all peripherals, and may individually

shut down any or all peripherals for power savings.

The on-chip Silicon Labs 2-Wire (C2) D

evelopment Interface allows non-intrusive (uses no on-chip

resources), full speed, in-circuit debugging using the production MCU installed in the final application. This

debug logic supports inspection and modification of memory and registers, setting breakpoints, single

stepping, run and halt commands. All analog and digital peripherals are fully functional while debugging

using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging with-

out occupying package pins.

Each device is specified for 2.7–5.25 V operation over the industrial temperature range (–40 to +85 °C).

F

or voltages above 3.6 V, the on-chip Voltage Regulator must be used. A minimum of 3.0 V is required for

USB com

munication. The Port I/O and

RST pins are tolerant of input signals up to 5 V. C8051F340/1/2/3/

4/5/6/7/8/9/A/B/C/D devices are available in 48-pin TQFP, 32-pin LQFP, or 32-pin QFN packages. See

Table 1.1, “Product Selection Guide,” on page 18 for feature and package choices.