组合逻辑电路分析与设计:从输入输出到最小化

版权申诉

133 浏览量

更新于2024-07-08

收藏 880KB PPTX 举报

"组合电路分析与最少化设计课件.pptx"

组合逻辑电路是数字电路中的重要组成部分,主要处理即时的输入信号并产生相应的输出,而不保留任何历史输入信息。这种电路的特点在于其输出完全取决于当前的输入状态,且电路内部不包含任何具有存储能力的元件,比如触发器或寄存器,因此没有反馈路径。这意味着输入信号经过电路处理后不会留下任何痕迹,即不存在记忆效应。

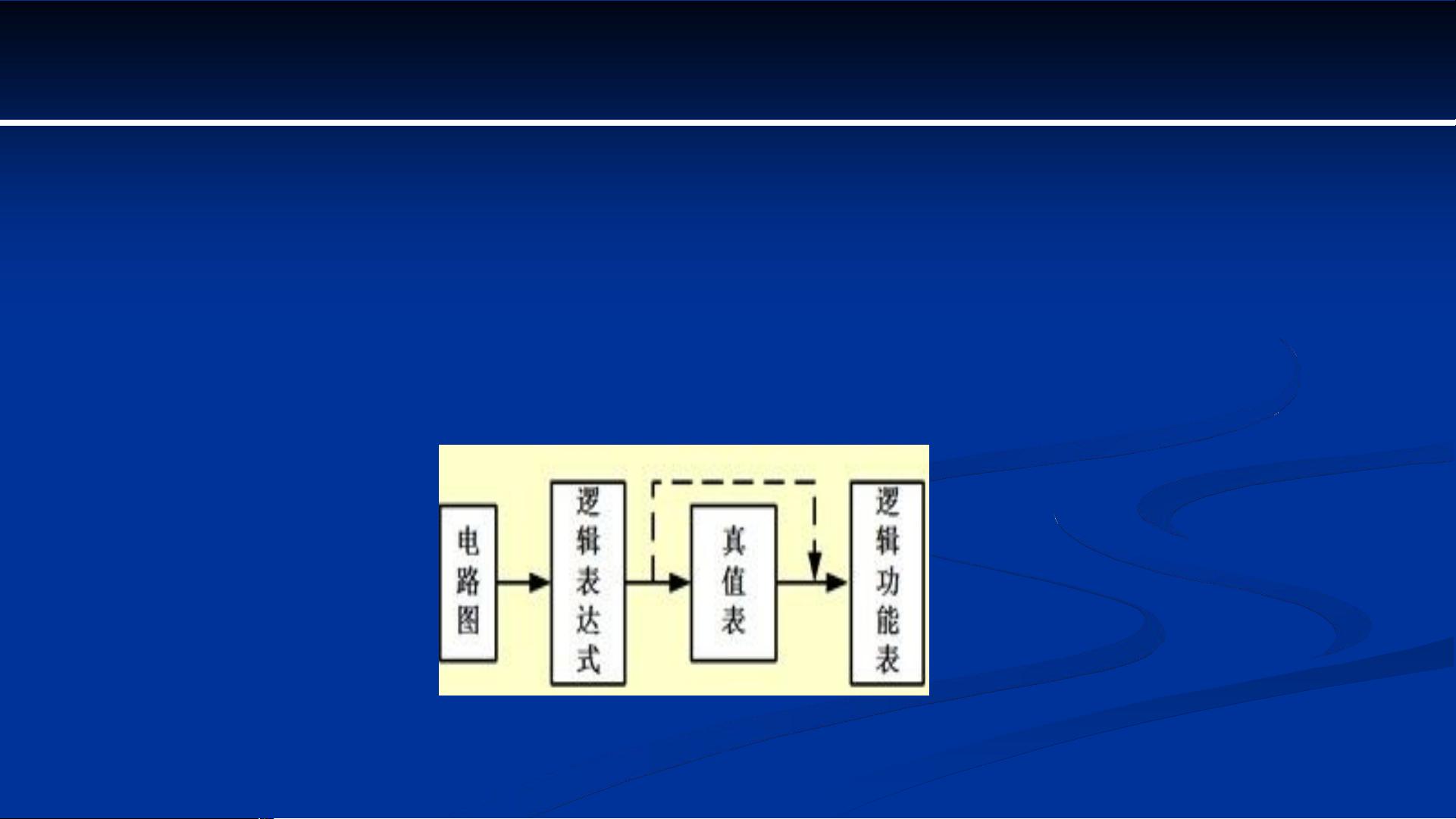

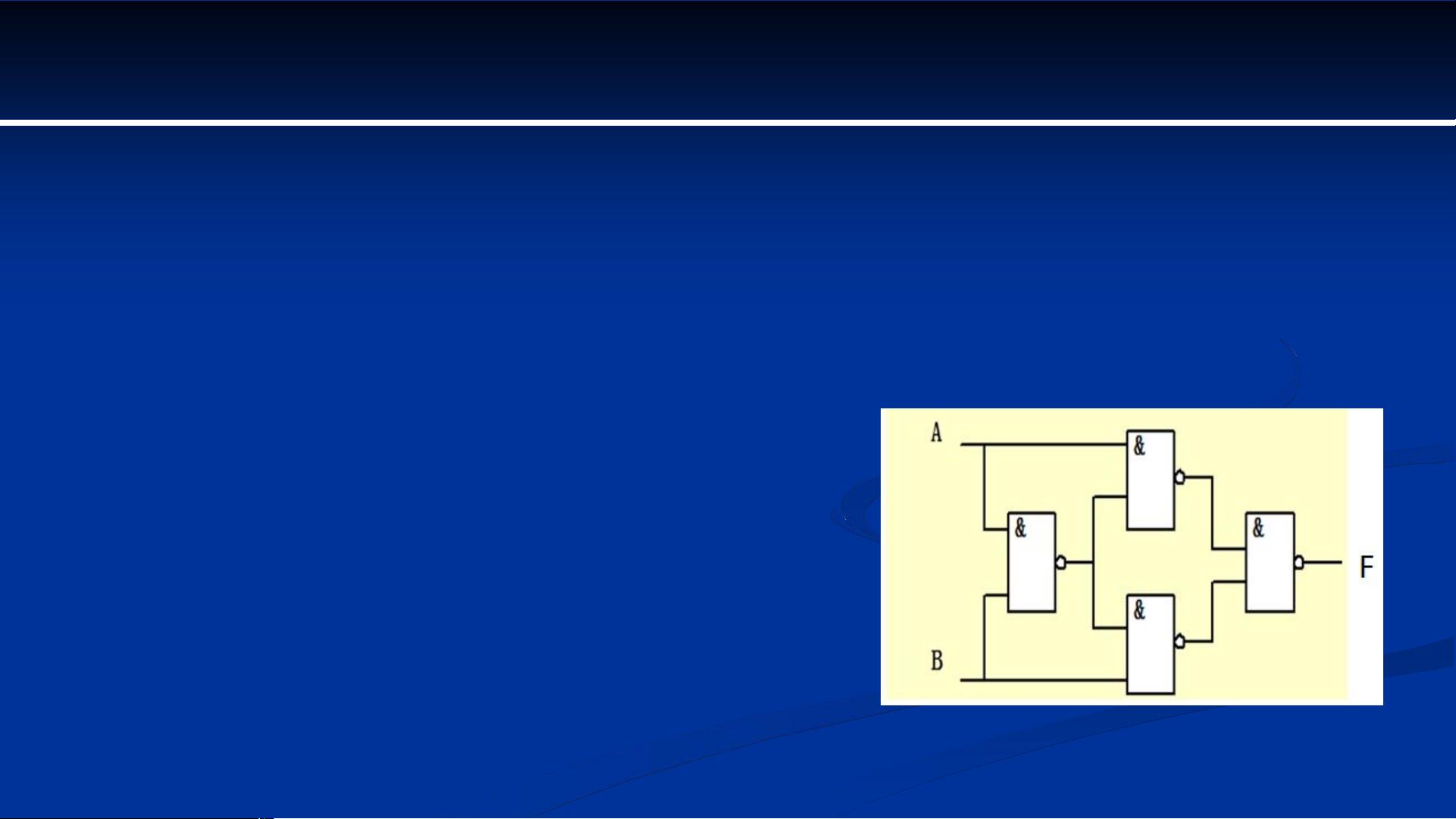

在分析组合逻辑电路时,主要目标是确定输入与输出之间的逻辑关系,以理解电路的功能。这可以通过多种描述方法来实现,包括逻辑函数表达式、真值表、卡诺图、逻辑图以及输入输出波形图。首先,可以在逻辑图上标出各节点的逻辑函数,逐步推导出整个电路的逻辑函数表达式,从而获得输出与输入的数学关系。此外,也可以直接通过逻辑图建立真值表,对所有可能的输入组合求出对应的输出,直观地揭示电路的功能。

例如,在分析一个电路时,如果电路由基本逻辑门(如与非门)组成,没有反馈回路和存储元素,那么我们可以确认这是一个组合逻辑电路。然后,我们可以通过给输入端分配不同的逻辑值(0或1),计算出对应的输出,形成真值表。以一个简单的异或门电路为例,当输入A和B分别为0和1时,输出为1;反之,如果A和B相同,则输出为0。通过这种方式,我们可以确定电路执行的是异或操作。

组合逻辑电路的最小化设计是另一个关键概念,其目的是简化逻辑函数,减少使用的门数量,降低功耗,同时保持电路原有的逻辑功能。常见的最小化方法包括代数法(如代数公式简化)、卡诺图法(Karnaugh Maps)和布尔代数优化。卡诺图是一种直观的图形化工具,可以帮助我们合并相邻的1格,简化逻辑表达式,从而达到电路的最小化。

在实际设计过程中,工程师会使用各种逻辑优化工具,如Quine-McCluskey算法或 Espresso 等专业软件,它们能够自动进行逻辑综合,找到最简化的门级表示。这些工具不仅可以简化逻辑设计,还可以考虑物理实现的约束,如延迟、面积和功耗,从而优化整个数字系统的性能。

组合逻辑电路的分析与最少化设计是数字电子技术中的基础内容,对于理解和设计复杂的数字系统至关重要。理解其特点、分析方法以及最小化策略,有助于提高电路效率,降低硬件成本,为现代计算机、通信设备和其他数字系统的设计提供了坚实的基础。

点击了解资源详情

点击了解资源详情

点击了解资源详情

念广隶

- 粉丝: 5w+

- 资源: 6万+

最新资源

- Angular实现MarcHayek简历展示应用教程

- Crossbow Spot最新更新 - 获取Chrome扩展新闻

- 量子管道网络优化与Python实现

- Debian系统中APT缓存维护工具的使用方法与实践

- Python模块AccessControl的Windows64位安装文件介绍

- 掌握最新*** Fisher资讯,使用Google Chrome扩展

- Ember应用程序开发流程与环境配置指南

- EZPCOpenSDK_v5.1.2_build***版本更新详情

- Postcode-Finder:利用JavaScript和Google Geocode API实现

- AWS商业交易监控器:航线行为分析与营销策略制定

- AccessControl-4.0b6压缩包详细使用教程

- Python编程实践与技巧汇总

- 使用Sikuli和Python打造颜色求解器项目

- .Net基础视频教程:掌握GDI绘图技术

- 深入理解数据结构与JavaScript实践项目

- 双子座在线裁判系统:提高编程竞赛效率