FPGA实现雷达脉冲预分选器:关联比较器设计

20 浏览量

更新于2024-08-28

收藏 439KB PDF 举报

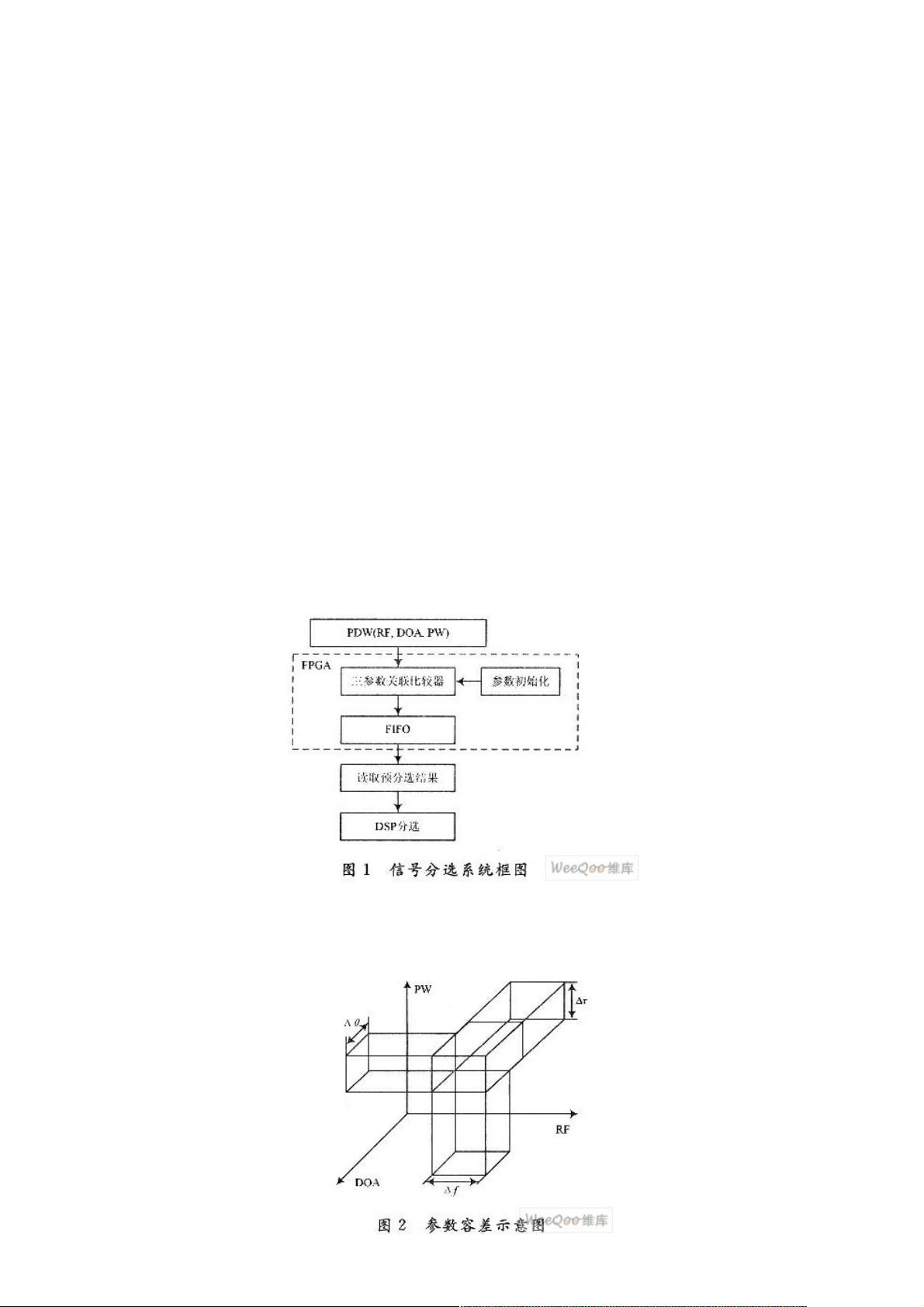

"基于FPGA的雷达脉冲预分选器设计通过采用高速FPGA器件,构建三参数关联比较器,实现对复杂电子战环境下雷达信号的高效预分选。预分选主要依赖于RF、PW和DOA这三个稳定的信号参数,以提高信号处理的实时性和准确性。"

在现代电子战环境中,信号的复杂性和密度显著增加,新体制雷达的出现使得信号参数呈现出多样化的变化。这对电子战信号处理系统提出了严峻挑战,特别是实时信号分选的需求日益增长。为了应对这一挑战,设计一个高效的预分选器显得至关重要。预分选是电子支援措施(ESM)系统中的关键步骤,它旨在快速识别和分离出感兴趣的信号,减轻后续主处理器的负担。

传统的预分选技术往往依赖于辐射源参数匹配,而现代设计则倾向于利用高速、可重构的硬件平台,如现场可编程门阵列(FPGA)。FPGA因其灵活性、高性能和高集成度,成为实现预分选器的理想选择。在本设计中,FPGA被用来构建三参数关联比较器,这比使用中小规模集成芯片更有效。

关联比较器的核心在于对雷达信号的五个主要参数进行匹配:载频(RF)、脉宽(PW)、到达方位(DOA)、到达时间(TOA)和脉幅(PA)。在预分选阶段,RF、PW和DOA通常被视为最稳定的参数,因为它们的变化范围相对较小且聚敛性较好。RF的离散性使得其在侦察中具有重要价值;DOA在相对静止或缓慢变化的情况下,提供了关于雷达位置的信息;而PW的稳定性使得它成为可靠的分选依据。相比之下,PA的波动较大,可信度较低,通常不作为预分选的依据;TOA虽然重要,但通常由主处理器处理,不在预分选阶段考虑。

预分选器通过关联比较器对输入的雷达脉冲进行快速比较,依据RF、PW和DOA的匹配程度进行分类。这种方法能够快速筛选出匹配特定参数范围的信号,有效地减少需要进一步处理的信号数量,从而提高了整个系统的处理速度和效率。

基于FPGA的雷达脉冲预分选器设计是现代电子战信号处理的一个重要创新,它利用FPGA的优势实现了对复杂信号环境的快速响应和高效处理。这种设计不仅可以满足实时性的需求,还为硬件结构的优化和升级提供了可能,适应了电子战系统对灵活性和性能的不断提高的要求。

2021-07-13 上传

114 浏览量

116 浏览量

点击了解资源详情

135 浏览量

2021-07-13 上传

120 浏览量

151 浏览量

2021-09-30 上传

weixin_38735899

- 粉丝: 2

最新资源

- LCD1602显示程序完整注释解析

- 电子书制作:学习工具与方法汇总

- 清爽绿色多边形风格工作总结PPT模板下载

- 陈灯2.3版:桌面代码管理器的智能升级

- BBC研发VideoContext: JavaScript视频合成库

- Xtreme.Toolkit.Pro:Windows平台下的GUI库介绍

- Linux平台实现NTFS格式读写功能的ntfs-3g软件介绍

- 微信企业号开发必备:JDK7.0的JCE补丁包介绍

- 步进电机扩展板:电路图与C++代码驱动指南

- 哈尔滨工业大学电子课件精选:电路分析与放大技术

- 蓝色渐变圆点背景的个人述职报告PPT模板介绍

- Android树形视图——高性能与功能丰富的界面展现

- SubNetMaskCalc V4.0:ABC网段子网划分与掩码计算工具

- GSM系统掉话原因分析与优化策略

- 掌握图像几何变换:Matlab程序应用指南

- Vue项目:Nerfles死女巫在暗黑破坏神2上的实现与构建