"TI LMK04000系列低噪声时钟抖动整形器与串联PLL结构"

需积分: 5 191 浏览量

更新于2024-04-13

4

收藏 1.71MB PDF 举报

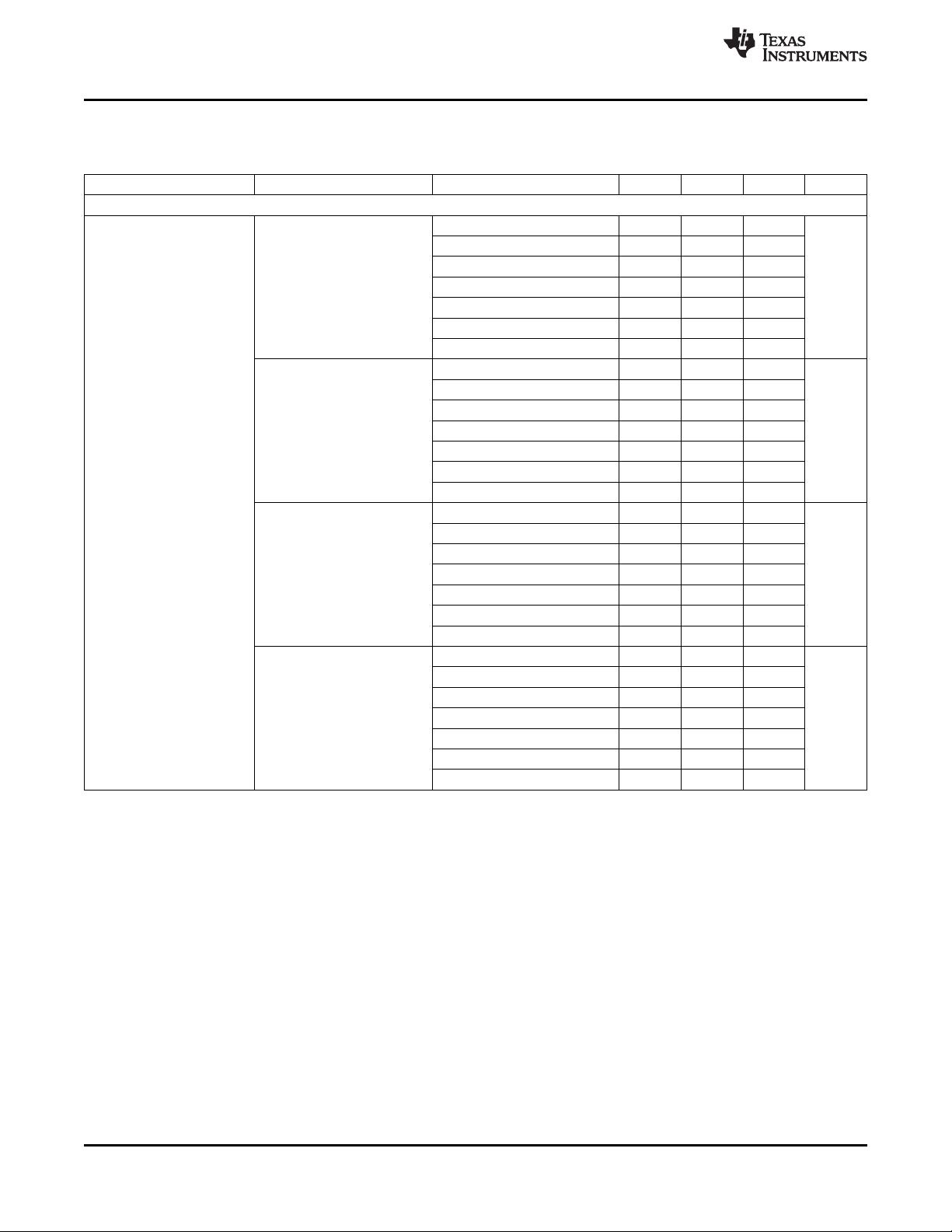

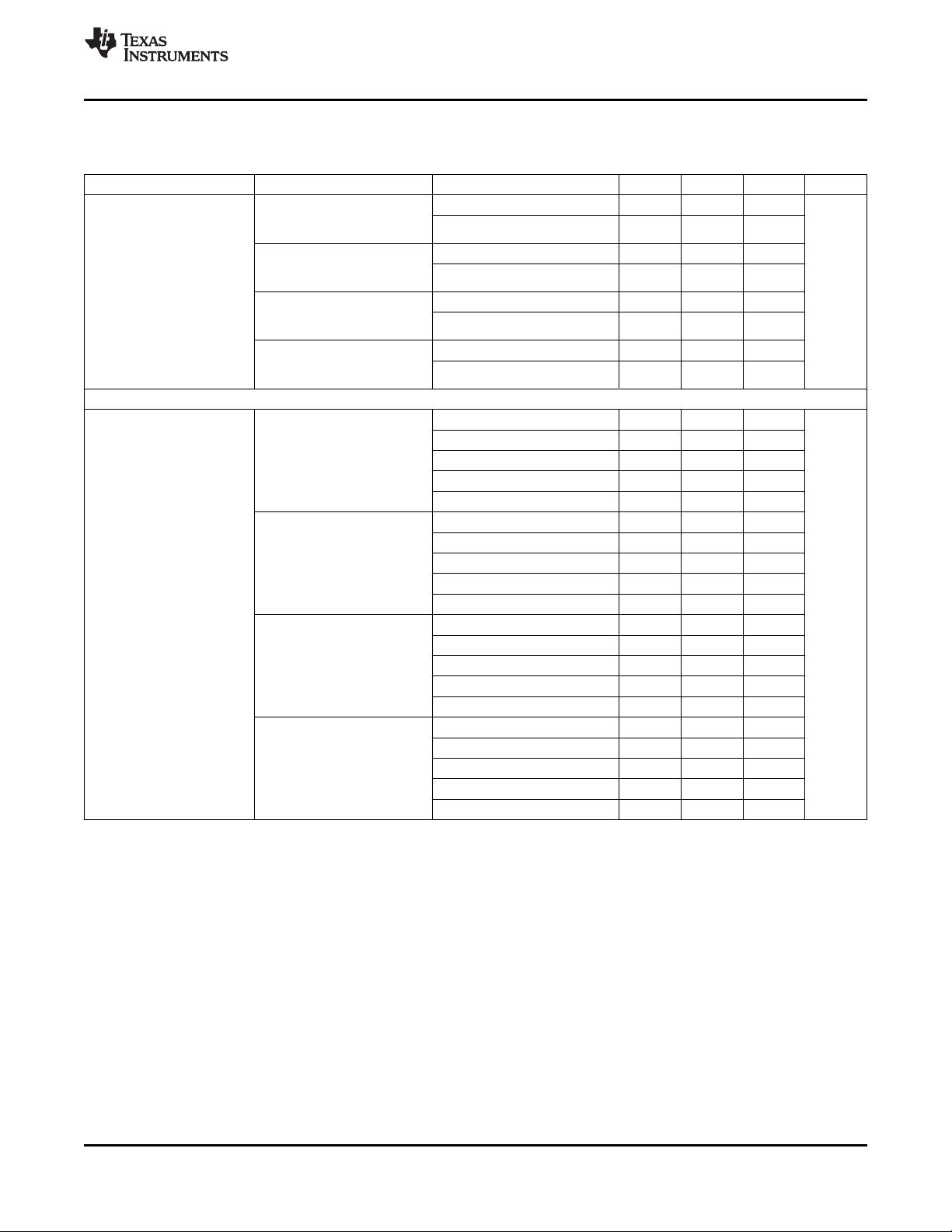

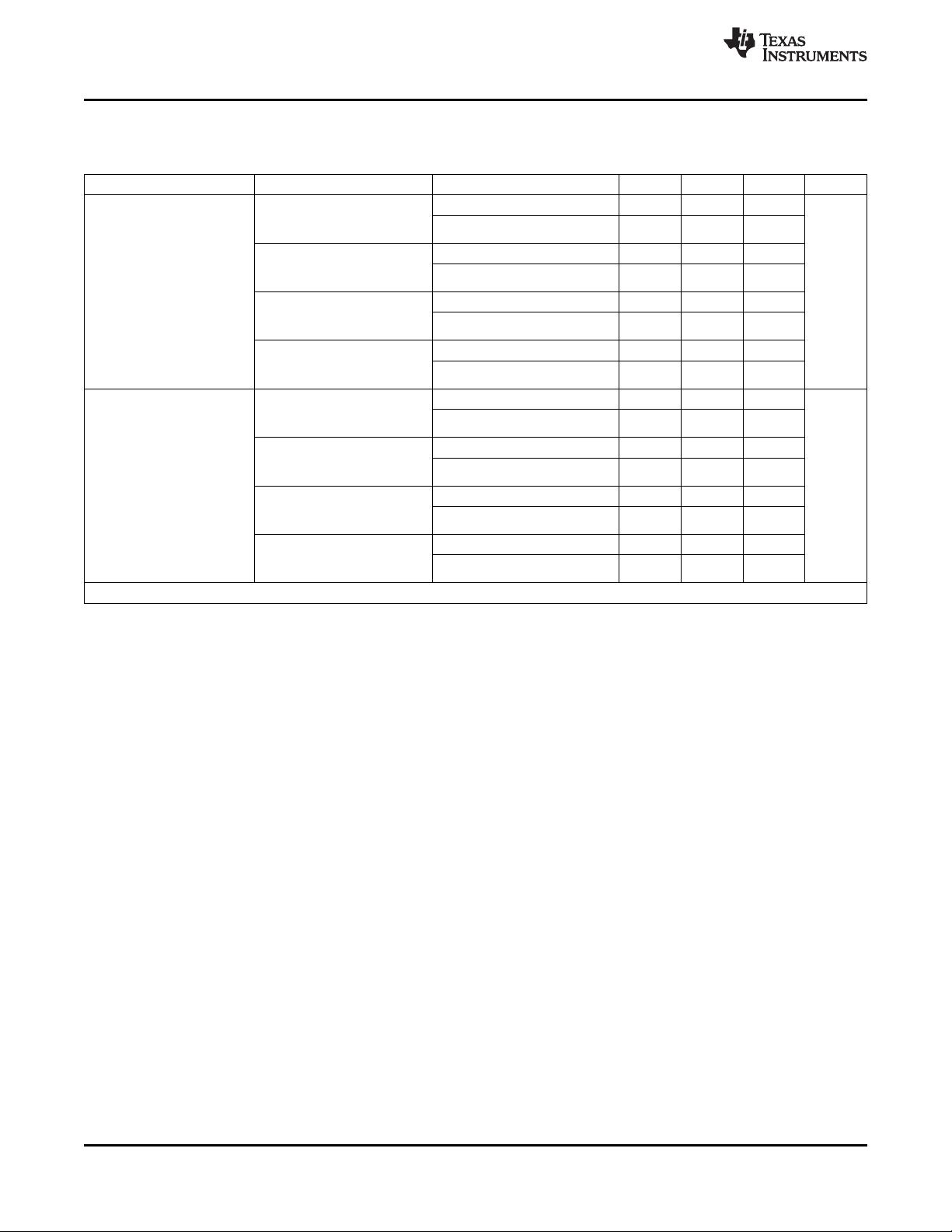

The TI LMK04000 family is a series of low-noise clock jitter cleaners with cascaded PLLs, offering high performance and flexibility for a wide range of applications. With its innovative Cascaded PLLatinum™ PLL architecture, these devices can support clock rates up to 1080 MHz, making them suitable for demanding systems that require precise timing synchronization.

One of the key features of the LMK04000 family is its default clock output (CLKout2) at power-up, ensuring that the device is ready to operate immediately without any additional configuration. The phase detector rate of up to 40 MHz allows for accurate phase detection and synchronization, further enhancing the performance of the clock cleaner.

Furthermore, the LMK04000 family comes equipped with five dedicated channel divider and delay blocks, providing users with flexibility in dividing and adjusting the timing of clock signals. This integrated feature simplifies the design process and allows for customization to meet specific system requirements.

Overall, the LMK04000 family combines advanced technology with user-friendly features to deliver a high-performance solution for applications requiring low-noise clock jitter cleaning. Whether it's in telecommunications, data communications, or industrial automation, these devices offer reliability and precision to ensure optimal system performance. With the LMK04000 family, users can trust in the quality and versatility of TI's clock cleaner technology to meet their timing synchronization needs.

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-11-30 上传

2022-11-30 上传

2022-11-30 上传

2022-11-30 上传

2022-11-30 上传

2022-11-30 上传

不觉明了

- 粉丝: 6797

- 资源: 5764