FPGA入门指南:数字电路设计与开发流程详解

需积分: 17 27 浏览量

更新于2024-07-28

收藏 672KB PDF 举报

FPGA入门教程深入讲解了数字电路设计的基本概念和FPGA的相关技术,对于想要进入IT行业特别是硬件开发领域的人来说,是一份不可或缺的指南。首先,课程从数字电路设计入门开始,强调逻辑设计的重要性,以二进制的'1'和'0'来表示模拟电压或电流的离散状态,以及各种常见的电平标准如TTL、CMOS等,这些电平标准对于理解和设计电路有着至关重要的作用。

在FPGA开发流程中,主要涉及以下几个步骤:

1. RTL设计 ( Register-Transfer Level Design): 这是FPGA设计的核心阶段,涉及到硬件描述语言(HDL),如 VHDL 或 Verilog,用于描述电路的逻辑功能。RTL设计者用这些高级语言编写电路的抽象模型,表达电路的逻辑关系,包括组合逻辑电路(仅依赖于当前输入的电路)和时序逻辑电路(不仅考虑当前输入,还需考虑之前的状态)。

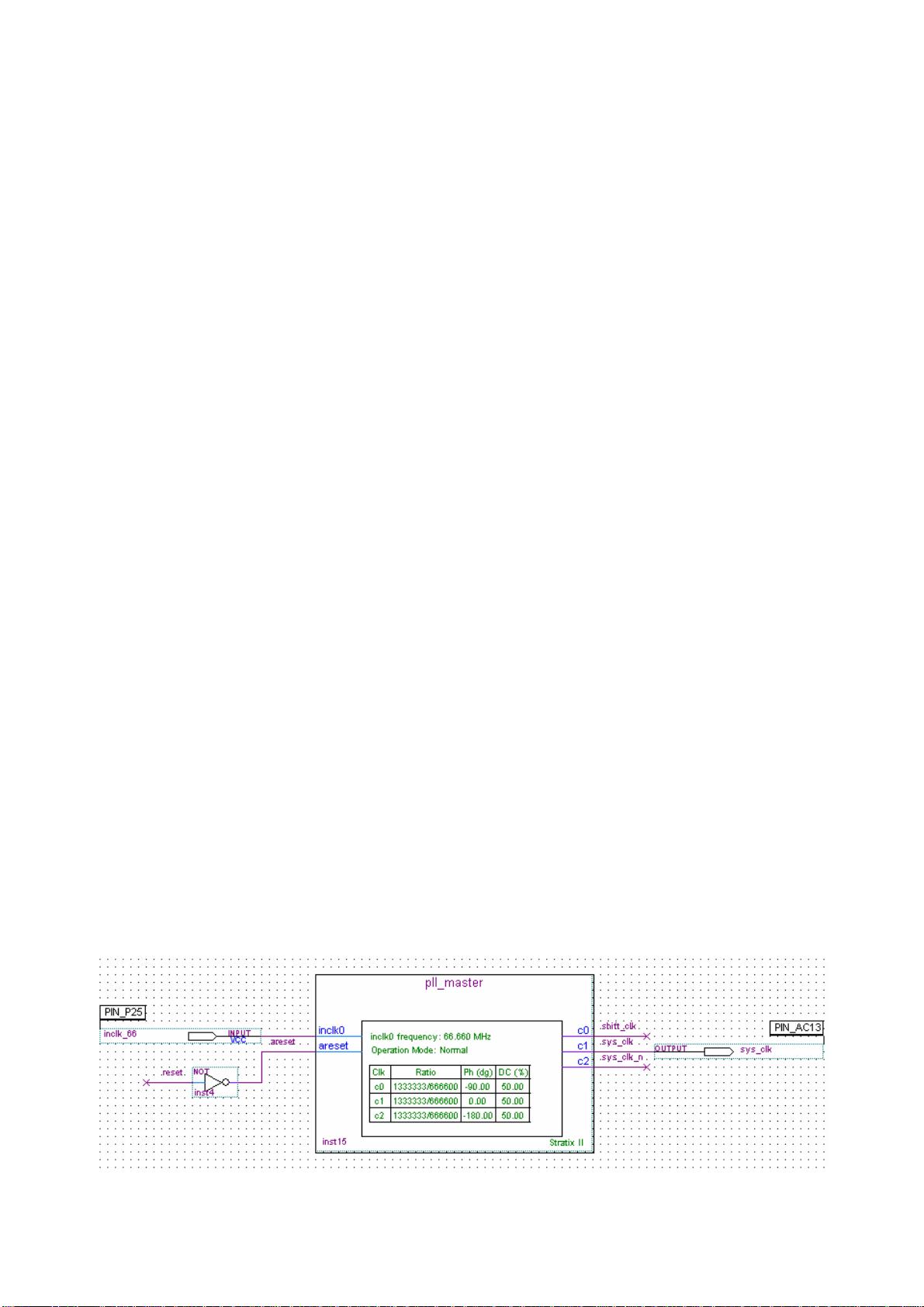

2. Quartus II设计实例: Intel Quartus II 是一款流行的FPGA设计工具,它提供了一个直观的界面来实现RTL设计到实际硬件的转换。用户通过图形化编辑器或文本编辑器创建设计,然后进行综合、布局和布线,最后生成可编程的FPGA配置文件。

3. ModelSim和Testbench: ModelSim是一款常用的模拟器,用于验证设计的正确性。它允许开发者在实际编程FPGA之前,先在虚拟平台上运行电路模型,检查时序行为和逻辑功能是否符合预期。Testbench则是用来编写测试用例的模块,帮助调试和确认设计的性能。

组合逻辑电路部分详细介绍了基本逻辑门如与门、或门、非门等,以及它们如何构成更复杂的电路。时序逻辑电路则重点讲解了触发器(如D触发器和JK触发器)的工作原理,包括建立时间、保持时间和输出延迟等关键参数,这些都是确保电路准确无误地执行时序操作的基础。

此外,教程还提到了一个简单的时序逻辑电路实例——时钟分频电路,这是FPGA在时序控制方面的一个常见应用,用于调整系统的时钟频率,满足不同系统需求。

这个FPGA入门教程为初学者提供了一个全面的入门路径,从基本的数字电路概念到实际的FPGA开发工具和实践,都是为了帮助学习者更好地理解和掌握这一关键技术。

2009-01-09 上传

2024-06-19 上传

2009-01-13 上传

点击了解资源详情

2024-11-01 上传

xuetianshichonglou

- 粉丝: 0

- 资源: 2

最新资源

- Haskell编写的C-Minus编译器针对TM架构实现

- 水电模拟工具HydroElectric开发使用Matlab

- Vue与antd结合的后台管理系统分模块打包技术解析

- 微信小游戏开发新框架:SFramework_LayaAir

- AFO算法与GA/PSO在多式联运路径优化中的应用研究

- MapleLeaflet:Ruby中构建Leaflet.js地图的简易工具

- FontForge安装包下载指南

- 个人博客系统开发:设计、安全与管理功能解析

- SmartWiki-AmazeUI风格:自定义Markdown Wiki系统

- USB虚拟串口驱动助力刻字机高效运行

- 加拿大早期种子投资通用条款清单详解

- SSM与Layui结合的汽车租赁系统

- 探索混沌与精英引导结合的鲸鱼优化算法

- Scala教程详解:代码实例与实践操作指南

- Rails 4.0+ 资产管道集成 Handlebars.js 实例解析

- Python实现Spark计算矩阵向量的余弦相似度