四人智力竞赛抢答器设计与实现

下载需积分: 9 | DOC格式 | 747KB |

更新于2024-07-25

| 148 浏览量 | 举报

"四人智力竞赛抢答器的课程设计报告,涉及数字电子技术,包括抢答电路、主持人电路、定时器及显示功能的设计。"

四人智力竞赛抢答器是一种常见的数字电子课程设计项目,旨在锻炼学生的电路设计和数字逻辑理解能力。这个设计主要分为两大部分:抢答电路和主持人控制电路。

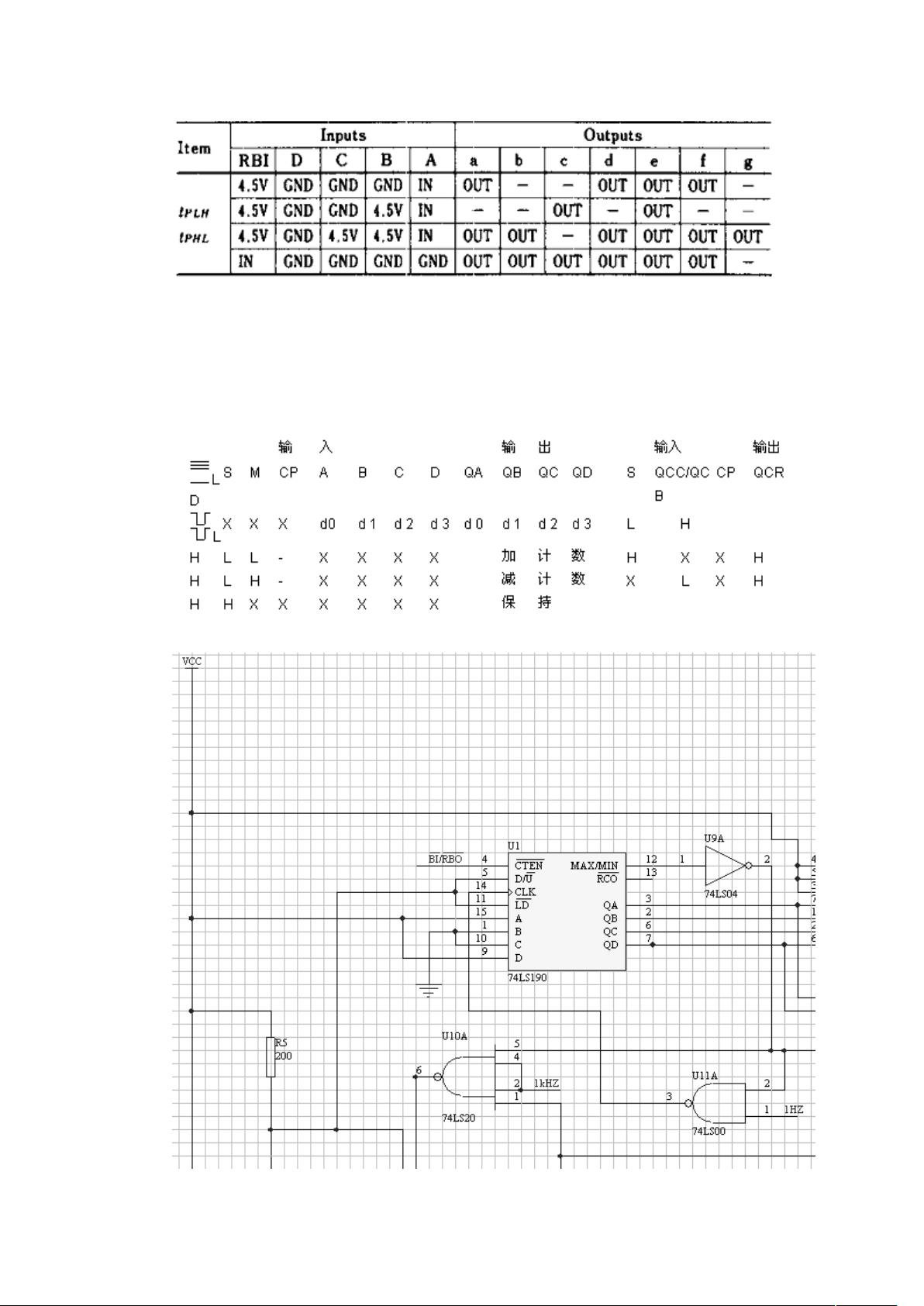

抢答电路的核心是利用74ls175作为锁存电路,它的作用是在有选手按下抢答按钮时,立即锁定当前的抢答状态,防止其他选手的后续操作。74ls175的输出信号可以阻止时钟脉冲,确保一旦有选手抢答,其他选手无法再进行操作。同时,74ls148作为编码器,将输入的选手编号转化为4位的BCD码,供共阴数码管显示。当抢答发生时,蜂鸣器鸣叫1秒,表示抢答有效。如果在9秒内无人抢答,系统会通过蜂鸣器报警,显示抢答无效。

主持人电路则利用74ls190作为计数器,用于倒计时功能。主持人启动抢答后,计数器从9开始倒计时,数码管清零并开始显示倒计时。74ls48编码器负责将当前的倒计时时间转化为7段码,显示在数码管上。如果在9秒内有选手抢答,计数器停止,显示抢答者的编号,并封锁输入编码电路,防止超时抢答。

设计中还提到,可以用石英晶体振荡器或555定时器来产生1Hz的脉冲信号,作为定时计数器的时钟脉冲(CP)源。这种低频信号确保了抢答过程中的精确计时。

整个设计综合运用了数字逻辑器件,如锁存器、编码器和计数器,实现了抢答、显示、定时和控制等功能,充分体现了数字电子技术的基本原理和应用。这样的课程设计有助于学生深入理解和掌握数字电路设计的基础知识,提升实践操作技能。

相关推荐

708 浏览量

1028854215

- 粉丝: 0

最新资源

- IMS:IP多媒体子系统详解与应用

- Hibernate: O/R Mapping框架详解与实践

- 程序员视角:深度剖析计算机系统工作机制

- Linux下GCC中文手册:详解C/C++编译器与选项

- Java Web框架Wicket深度解析

- 侯捷解读:系统重构的艺术与风险

- Directshow流媒体客户端FilterGraph动态重构技术研究

- 精通C# 2008中的LINQ:语言集成查询

- 编程规范与最佳实践指南

- Panorama系统程序开发规范详解

- 软件编程规范:排版与代码整洁

- 预测PI控制系统根轨迹分析及其稳定性

- 阎石《数字电子技术》第四版习题详解:二进制与十六进制转换及逻辑函数简化

- VC6.0计算器程序源代码示例

- Linux嵌入式系统移植:从u-boot到 BusyBox

- 链接与加载器详解:Linux论坛译作