DC概论:时序分析与约束管理

需积分: 5 43 浏览量

更新于2024-06-23

1

收藏 2.98MB PDF 举报

"左左右右DC概论.pdf"

DC(Design Compiler)是Synopsys公司推出的一款先进的集成电路设计自动化工具,主要用于IC设计中的逻辑综合过程。它通过优化逻辑电路,满足时序、面积、功耗等设计约束,帮助设计师实现高质量的数字电路设计。本资源是对DC工具的概论性总结,涵盖了多个关键概念和使用技巧。

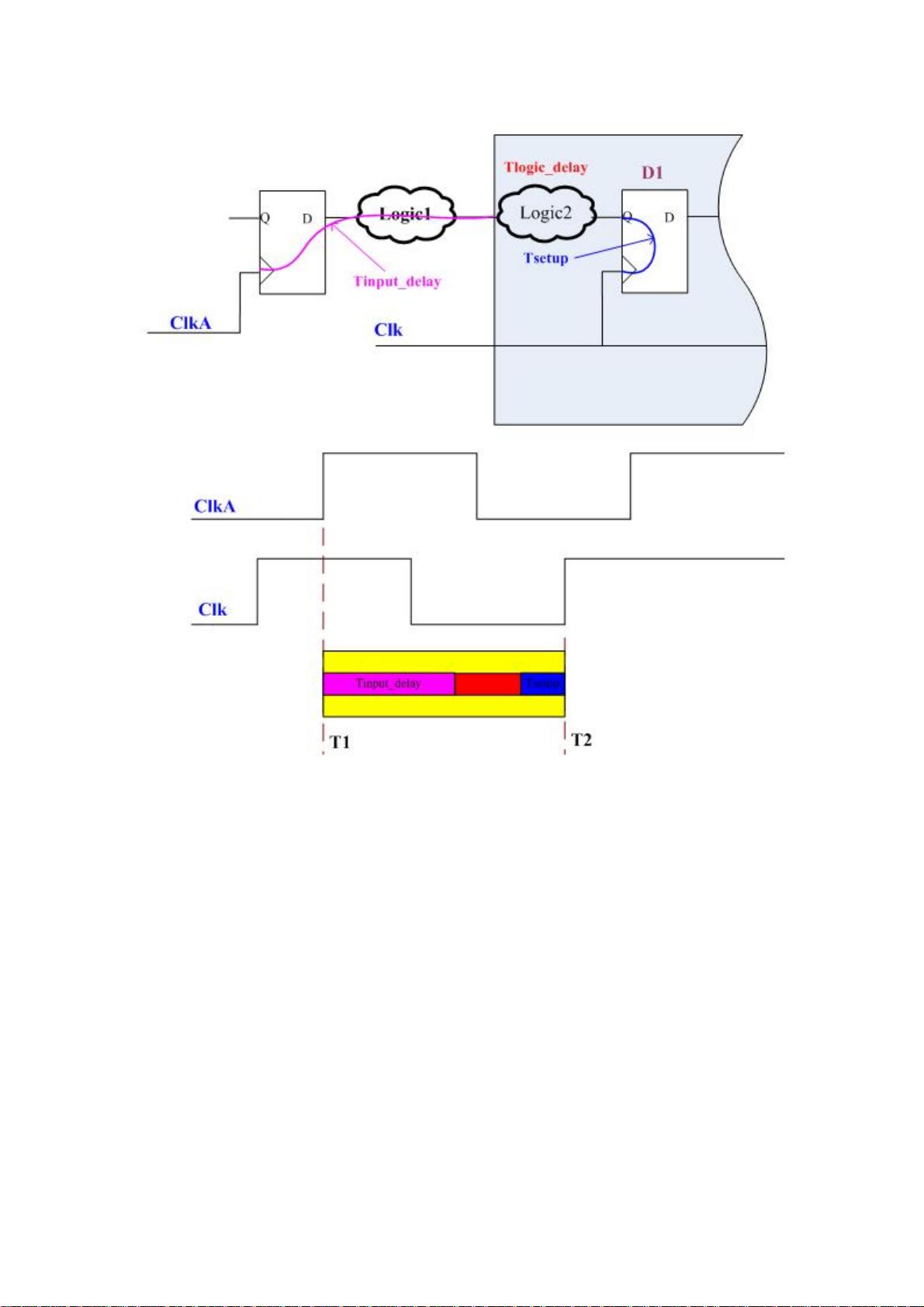

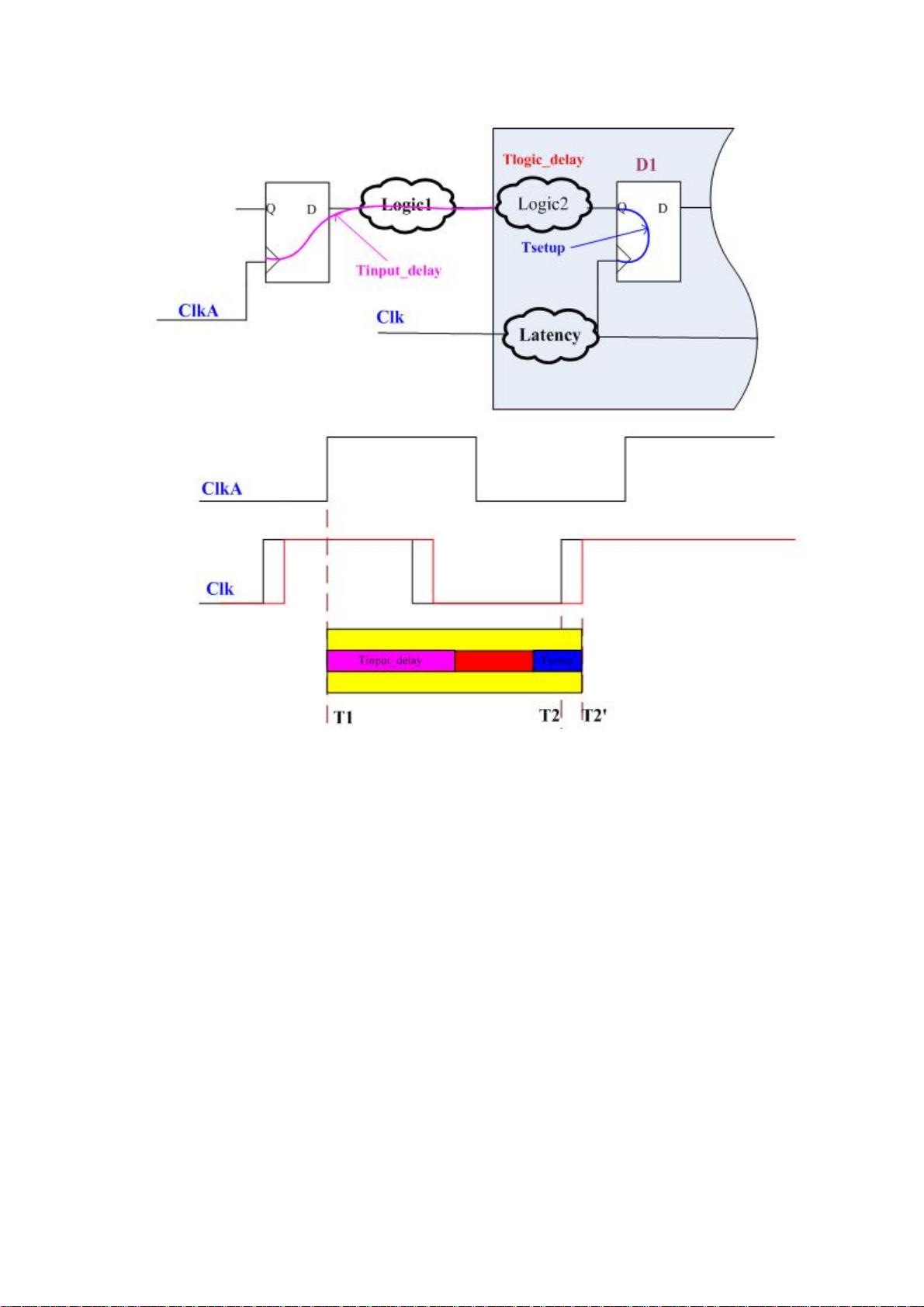

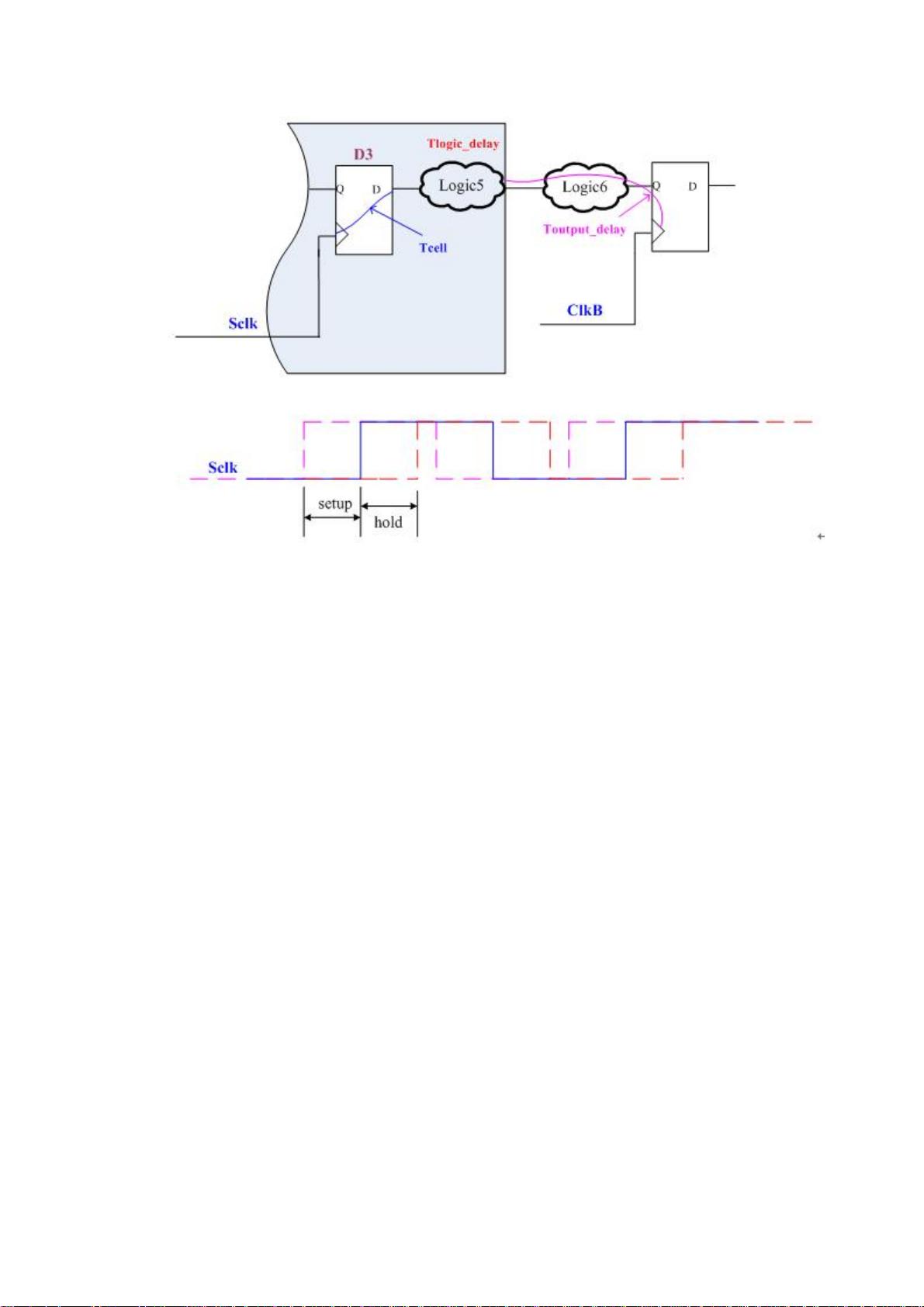

一、Setuptime与Holdtime

建立时间(Setuptime)和保持时间(Holdtime)是数字电路时序分析的核心概念。建立时间是指数据必须在时钟信号上升沿之前稳定的时间,确保在时钟触发器捕获数据时,数据已经稳定在正确状态。而保持时间则是在时钟上升沿之后,数据必须保持稳定的时间,以防止在时钟边沿后发生错误变化。

二、Fanout与Skew

Fanout指的是单一门电路输出驱动其他门电路的数量。高扇出可能导致信号延迟增加,因为驱动多个负载会消耗更多能量,从而影响时序。Skew则是指时钟信号在不同路径上的传播延迟差异,这可能导致不同位置的触发器在同一时钟边沿下工作不一致,对系统时序产生负面影响。

三、Multicycle Path

多周期路径(Multicycle Path)是一种特殊路径处理方式,允许某些路径的时序要求比其他路径宽松。在这些路径上,时钟周期可以被拉长,以提高设计的灵活性和性能。

四、Gated Clock

门控时钟(Gated Clock)是通过门电路控制时钟信号,只在需要时才激活时钟,以此减少未使用的时钟分支的功耗。但这也可能引入额外的延迟和时序复杂性。

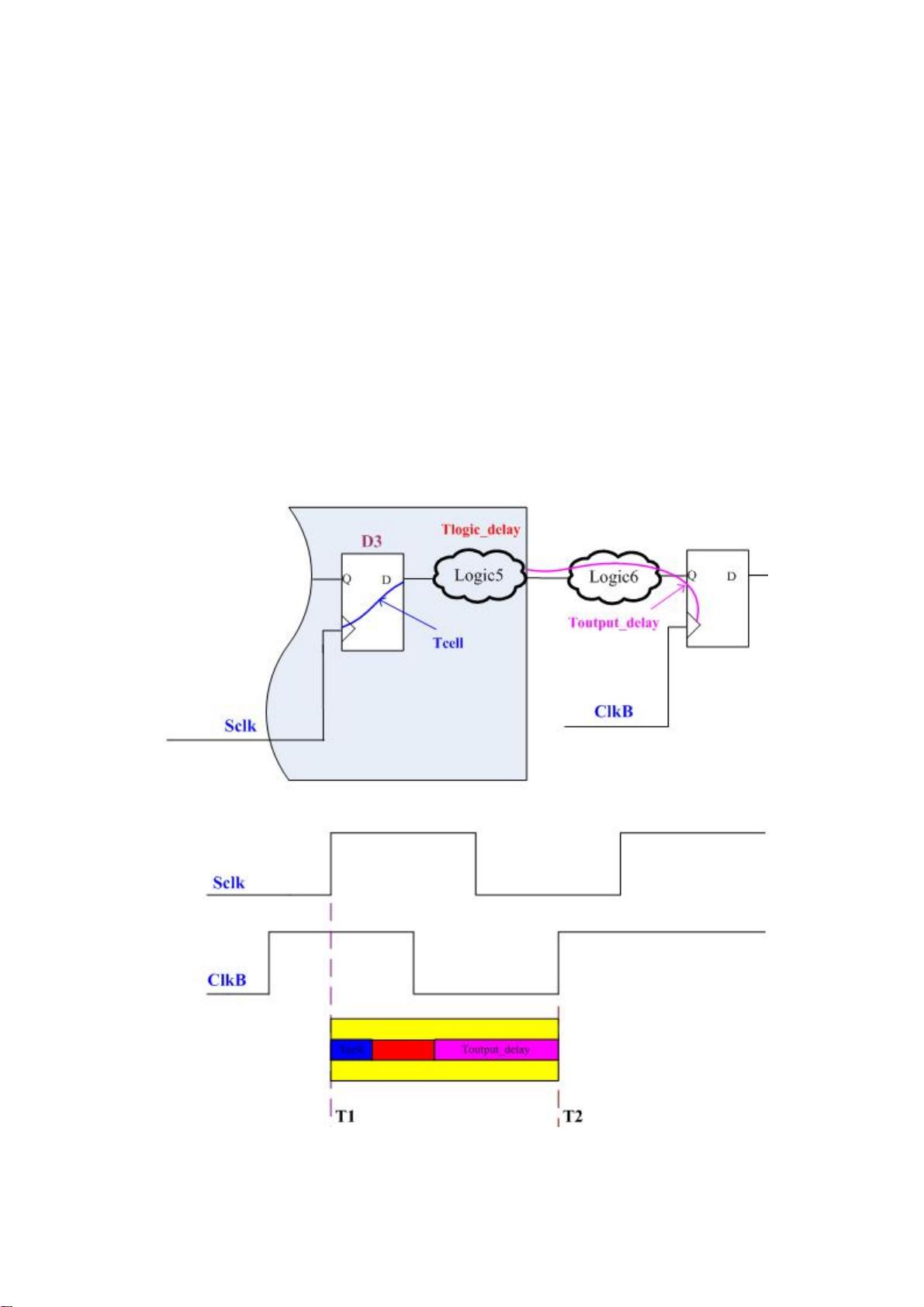

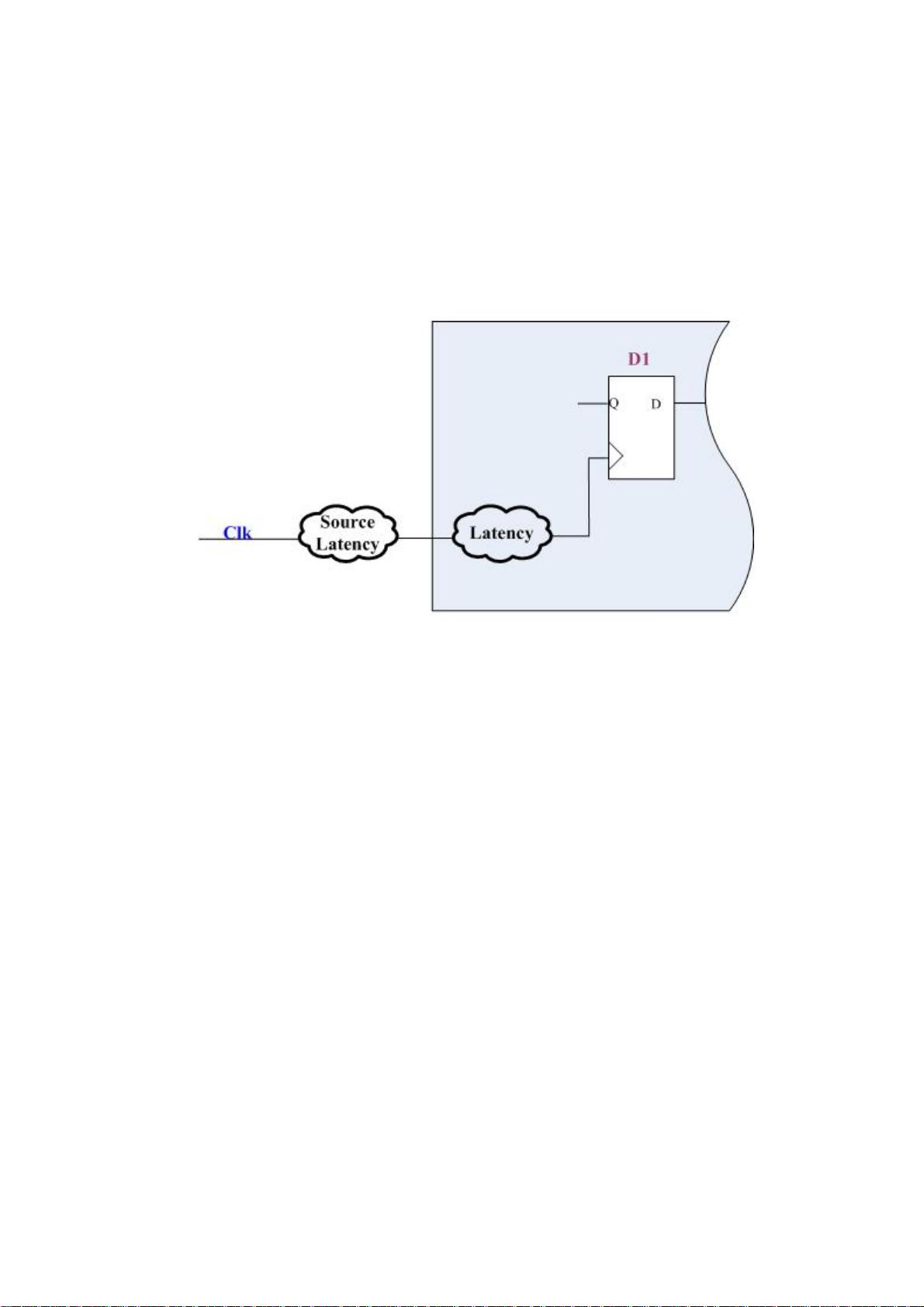

五、IO约束

IO约束涉及输入/输出接口的时序和电气特性,包括IO标准选择、驱动电流设定、输入延迟和输出负载等。正确的IO约束设置对于确保芯片与外部电路的正确通信至关重要。

六、DC优化约束

在使用DC进行综合时,设计师需要提供各种优化约束,如最大时钟周期、最小门延迟、功耗限制等。这些约束指导DC进行逻辑优化,以满足预设的目标。

DC概论覆盖了数字电路设计中至关重要的时序分析、路径类型、优化策略和约束设置,是理解并有效使用DC工具进行设计的关键。通过深入学习和实践,设计师能够更好地控制和优化设计的时序性能,实现更高效、可靠的集成电路设计。

2020-03-15 上传

2021-09-24 上传

2018-10-08 上传

滕杰

- 粉丝: 8

- 资源: 191

最新资源

- 正整数数组验证库:确保值符合正整数规则

- 系统移植工具集:镜像、工具链及其他必备软件包

- 掌握JavaScript加密技术:客户端加密核心要点

- AWS环境下Java应用的构建与优化指南

- Grav插件动态调整上传图像大小提高性能

- InversifyJS示例应用:演示OOP与依赖注入

- Laravel与Workerman构建PHP WebSocket即时通讯解决方案

- 前端开发利器:SPRjs快速粘合JavaScript文件脚本

- Windows平台RNNoise演示及编译方法说明

- GitHub Action实现站点自动化部署到网格环境

- Delphi实现磁盘容量检测与柱状图展示

- 亲测可用的简易微信抽奖小程序源码分享

- 如何利用JD抢单助手提升秒杀成功率

- 快速部署WordPress:使用Docker和generator-docker-wordpress

- 探索多功能计算器:日志记录与数据转换能力

- WearableSensing: 使用Java连接Zephyr Bioharness数据到服务器