Xilinx A7 FPGA DDR3 IP核配置与初始化指南

需积分: 46 84 浏览量

更新于2024-09-03

收藏 1.74MB DOCX 举报

"该文档详细介绍了在Xilinx A7系列FPGA中如何创建和初始化DDR3内存控制器的IP核,包括PLL的配置、IP核的实例化以及与DDR3接口的连接。"

在Xilinx的A7系列FPGA设计中,实现DDR3内存接口是一个重要的步骤,它涉及到高速数据传输和系统的时钟管理。DDR3内存因其高带宽和低功耗特性,广泛应用于现代数字系统中。以下是对创建和初始化DDR3 IP核过程的详细说明:

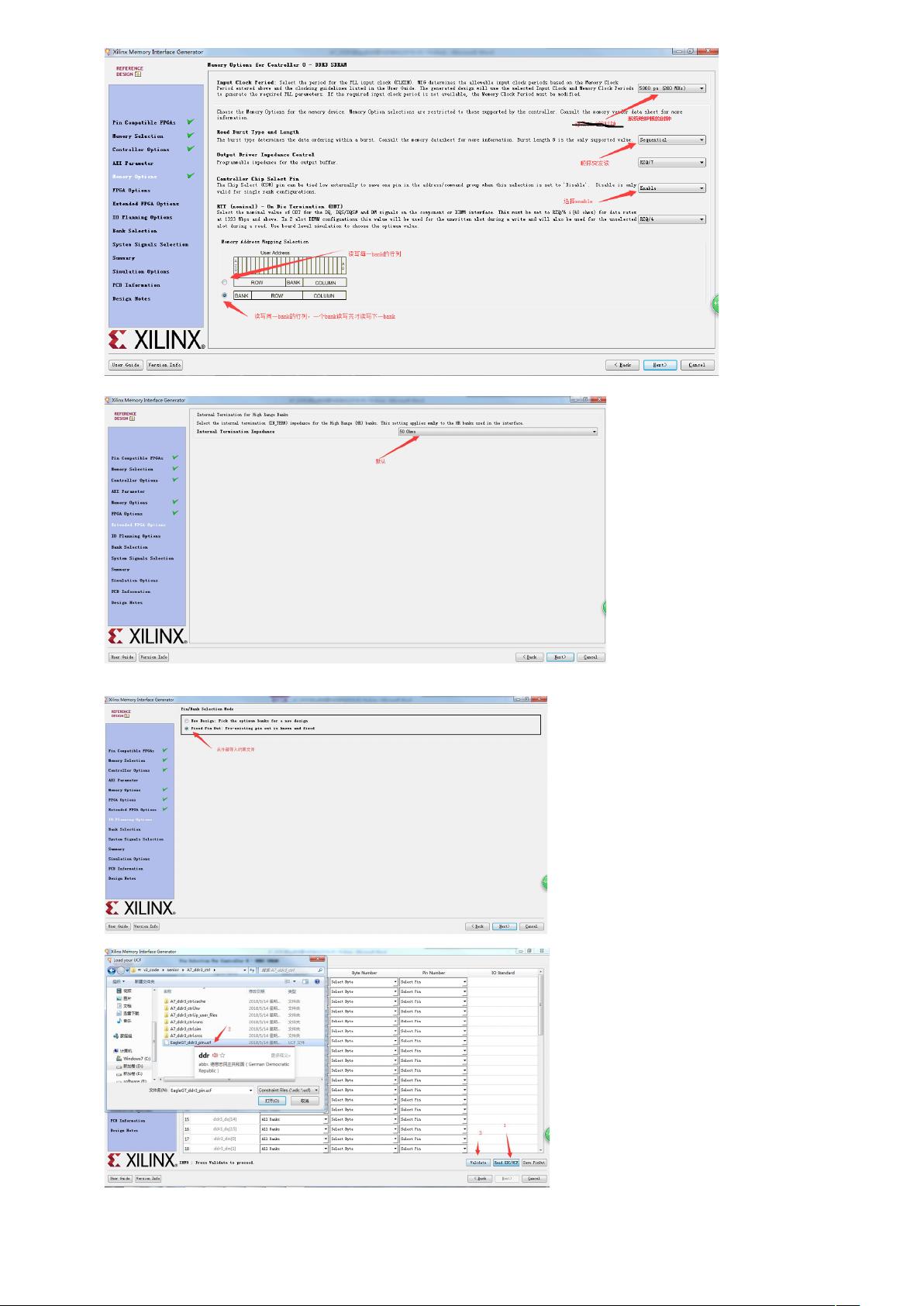

1. **创建DDR3 IP核**:

- 首先,开发者需要通过Xilinx的Vivado工具启动IP核创建流程,选择相应的DDR3控制器IP,即mig_7series_0。在这个过程中,需要设置一系列参数,如内存类型、内存大小、数据宽度、时钟频率等,以满足具体应用需求。

- 在设置完成后,点击“Next”按钮,继续配置IP核的各个选项,如时钟管理、功耗优化、错误检测等。最后,点击“Generate”,完成IP核的生成。

2. **创建PLL(Phase-Locked Loop)**:

- PLL是FPGA设计中的关键组件,用于生成所需的时钟信号。在本案例中,创建一个名为clk_wiz_0的PLL,目的是生成200MHz的时钟信号,这个时钟频率通常用于驱动DDR3内存。

- PLL的配置包括输入时钟频率(例如50MHz)、输出时钟频率(200MHz)以及其他时钟参数。配置完成后,实例化PLL模块,将输入时钟连接到PLL的输入端,然后连接PLL的输出时钟到DDR3 IP核和其他需要200MHz时钟的模块。

3. **实例化DDR3 IP核**:

- DDR3 IP核的实例化涉及到将IP核的内部接口与外部DDR3内存芯片的物理引脚相连。这一步骤通常需要参照提供的例化模板进行,确保正确连接所有必要的地址、命令、数据和控制信号。

- 例如,`mig_7series_0_inst`是DDR3 IP核的实例名称,其输入输出端口包括ddr3_addr、ddr3_ba、ddr3_cas_n等,这些都是与DDR3内存交互的关键信号。

4. **应用接口**:

- DDR3 IP核还提供了与应用逻辑(或称为上层模块)交互的接口,如`app_addr`、`app_cmd`、`app_en`等。这些接口用于控制内存访问,包括读写地址、命令序列和数据传输。

5. **初始化和配置**:

- DDR3 IP核的初始化通常涉及对内存的预配置,包括时序参数、内存模式等。这些参数可以通过IP配置界面设定,并在系统启动时自动执行初始化过程,确保DDR3内存能正常工作。

- `init_calib_complete`是一个信号,表明DDR3内存初始化和校准已完成,可以安全地进行数据传输。

创建和初始化A7_DDR3 IP核涉及了时钟管理、IP核配置、实例化、信号连接和系统级的接口设计。在实际工程中,这些步骤需要精确执行,以确保DDR3内存的稳定、高效运行。同时,理解并掌握这些知识点对于进行高性能FPGA设计至关重要。

1173 浏览量

202 浏览量

2022-06-21 上传

576 浏览量

weixin_41407051

- 粉丝: 0

最新资源

- C++实现的Excel与音频文件高效操作工具

- 掌握eq、get、find函数的实现技巧

- JSP个人博客案例分享与教程

- C++程序设计第二版教程与习题源码解析

- note-taker:Express.js 主力文件解析与应用

- DAEMON虚拟光驱软件介绍与应用

- 三维人脸识别在移动支付领域的应用研究

- Android触摸控制实现代码示例解析

- SSH框架系统源码与数据库设计开发完整指南

- 探索.NET ORM框架:实战教程与VS2010示例

- EditPlus v4.1.868 双语版简体汉化介绍

- 邱关源电子教案:考研电路复习资料详解

- PHP学习资源:精选源码供初学者参考

- 轻松实现Activity/Fragment/VGroup多种状态显示的PageStateLayout

- Unix网络编程卷1源码解析与学习

- 飞鱼在线编辑器后台管理功能与文件架构解析