Lattice DDR3 SDRAM Controller IP Core用户指南概述

需积分: 24 92 浏览量

更新于2024-07-17

收藏 4.79MB PDF 举报

本资源是Lattice半导体公司发布的"Double Data Rate (DDR3) SDRAM Controller IP Core用户指南"(IPUG80 Version 1.9,发布日期:2016年10月)。该指南详细阐述了针对DDR3 SDRAM控制器IP Core的使用方法和技术特性,旨在帮助设计者充分利用这款高性能的内存接口控制器。

1. **简介**(Chapter 1):快速概述了IP Core的主要特点,包括适用于DDR3标准的高速数据传输能力、高效能和低功耗设计。它旨在简化系统集成,并确保与各种DDR3 SDRAM模块兼容。

2. **功能描述**(Chapter 2):

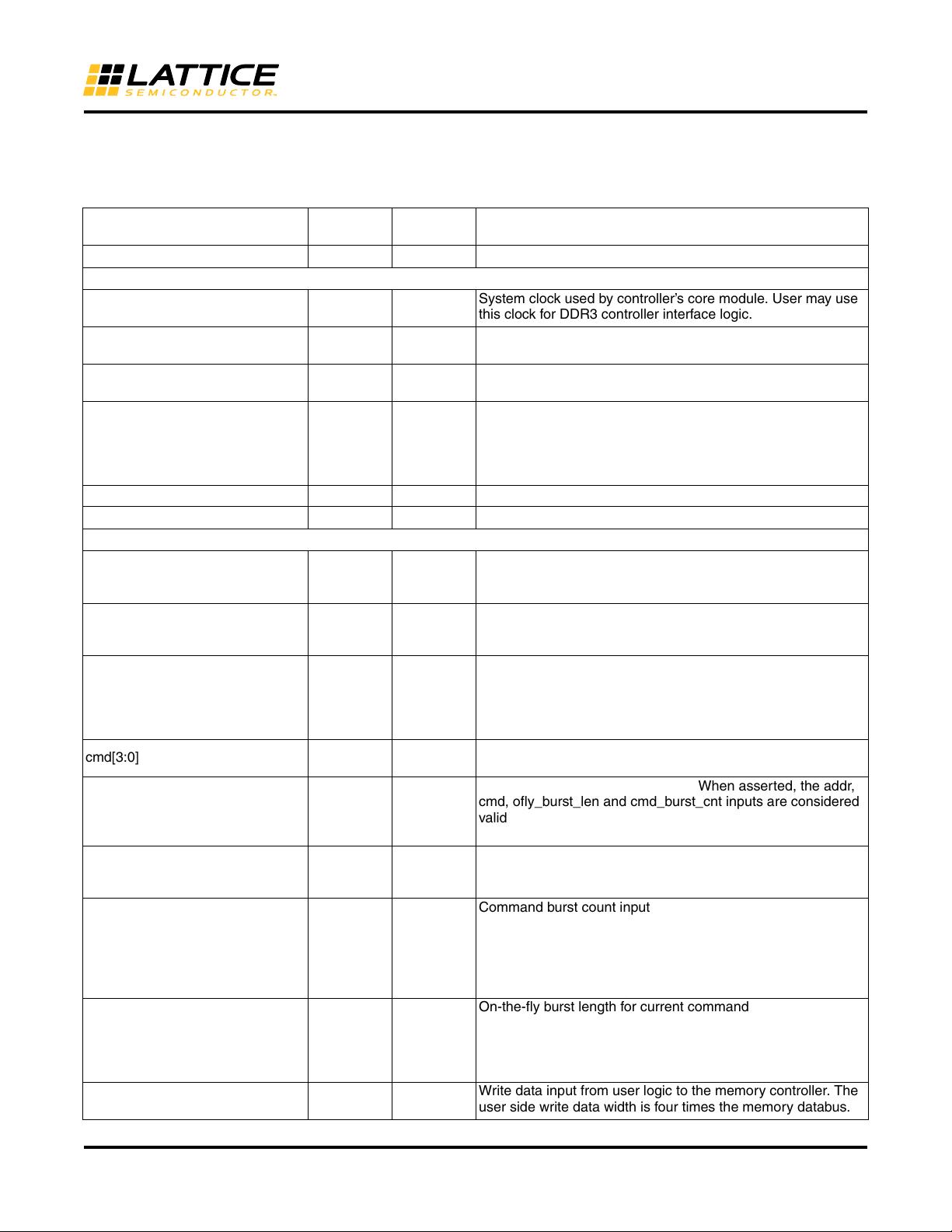

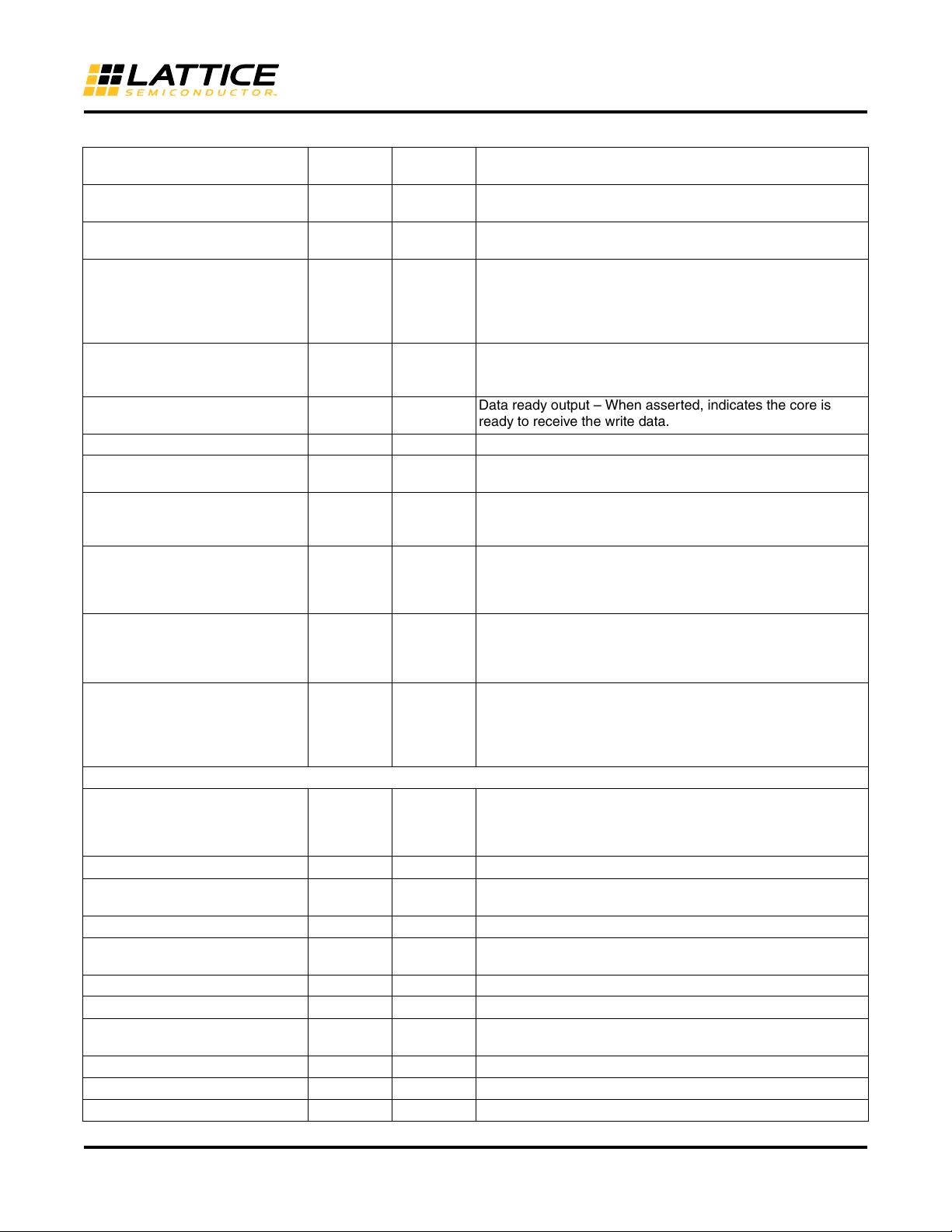

- **DDR3 MC Module**:这部分解释了控制器如何与内存模块(MC)交互,包括命令解码逻辑,用于处理不同类型的内存操作指令。

- **命令应用逻辑**:详细说明了IP Core如何解析接收到的命令信号,并执行相应的内存操作,如写入、读取和刷新操作。

- **On-Die Termination**:介绍了控制器内置的终端匹配电路,用于优化信号完整性,确保数据在不同引脚上的正确接收。

- **DDR3 PHY Module**:描述了物理层模块,负责与内存模块的物理连接,包括信号时钟同步和信号质量监控。

- **初始化模块**:说明了控制器的初始化过程,确保在启动时正确设置工作模式和配置参数。

- **Write Leveling** 和 **Read Training**:针对特定型号的设备(ECP5和Lattice ECP3),提供了写入平滑技术和读取训练的使用指导。

- **Data Path Logic**:阐述了数据传输路径的实现,确保数据在控制器和内存之间的高效交换。

- **信号描述**:给出了接口中涉及的关键信号定义,帮助设计者理解信号的电气特性和时序规范。

3. **本地用户接口**:用户可以通过这个接口控制IP Core的工作模式、配置和错误检测,增强了可编程灵活性。

4. **模式寄存器编程**:强调了如何通过设置不同的寄存器来调整控制器的工作模式,以适应不同应用场景的需求。

5. **其他**:指南还涵盖了用户命令的具体使用,如WRITE、WRITEA、READ和READA操作,以及REFRESH支持等关键功能。

这份用户指南为设计者提供了一个全面的指南,让他们能够充分理解和利用Lattice的DDR3 SDRAM控制器IP Core,实现高性能内存系统的构建。在实际应用中,设计者需要遵循指南中的指导,确保正确配置和操作IP Core,以达到最佳性能和稳定性。

2017-08-22 上传

2011-03-07 上传

2021-10-01 上传

2021-10-01 上传

2022-09-21 上传

2022-09-19 上传

121 浏览量

2022-09-22 上传

2023-08-08 上传

tbzj_2000

- 粉丝: 343

- 资源: 10

最新资源

- WebRTC:适用于 iOSmacOS 的通用 WebRTC XCFramework

- Feature-Detection-and-Matching

- 尖端生长的植物细胞形态发生的各向异性粘塑性模型matlab代码.zip

- [聊天留言]简单·留言本 v1.1_simplegbook11.rar

- Unity古风场景资源

- 基于深度学习方法的车辆上牌量预测_深度学习_

- LibContainer:容器框架

- YelpCamp:Colt Steele在线Web开发人员Bootcamp的YelpCamp项目

- ruTS:从俄语文本中提取统计数据的库

- phpBB-Auto-Database-Backup:phpBB 3.1的扩展,它将使用phpBB 3.1 Cron自动备份您的数据库

- MyJavaStudy:Java算法实践

- VDatum 空间变化的不确定性matlab代码.zip

- 2022最新版HTML只言片语网站导航模板

- go语言编写的兼容redis协议的kv存储

- 数学建模竞赛及备赛用的源代码.zip

- lyceum:Lyceum是用Go编写的开源电子书管理系统