Verilog HDL入门:模块与语法解析

需积分: 7 197 浏览量

更新于2024-07-18

收藏 622KB PPTX 举报

"FPGA入门教程,主要讲解Verilog HDL语言及FPGA开发流程"

在电子设计领域,FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,允许用户根据需求自定义硬件逻辑。对于初学者,了解FPGA开发首先需要掌握Verilog HDL(Hardware Description Language),这是一种广泛使用的硬件描述语言,用于描述数字系统的设计。

1. Verilog HDL模块基础

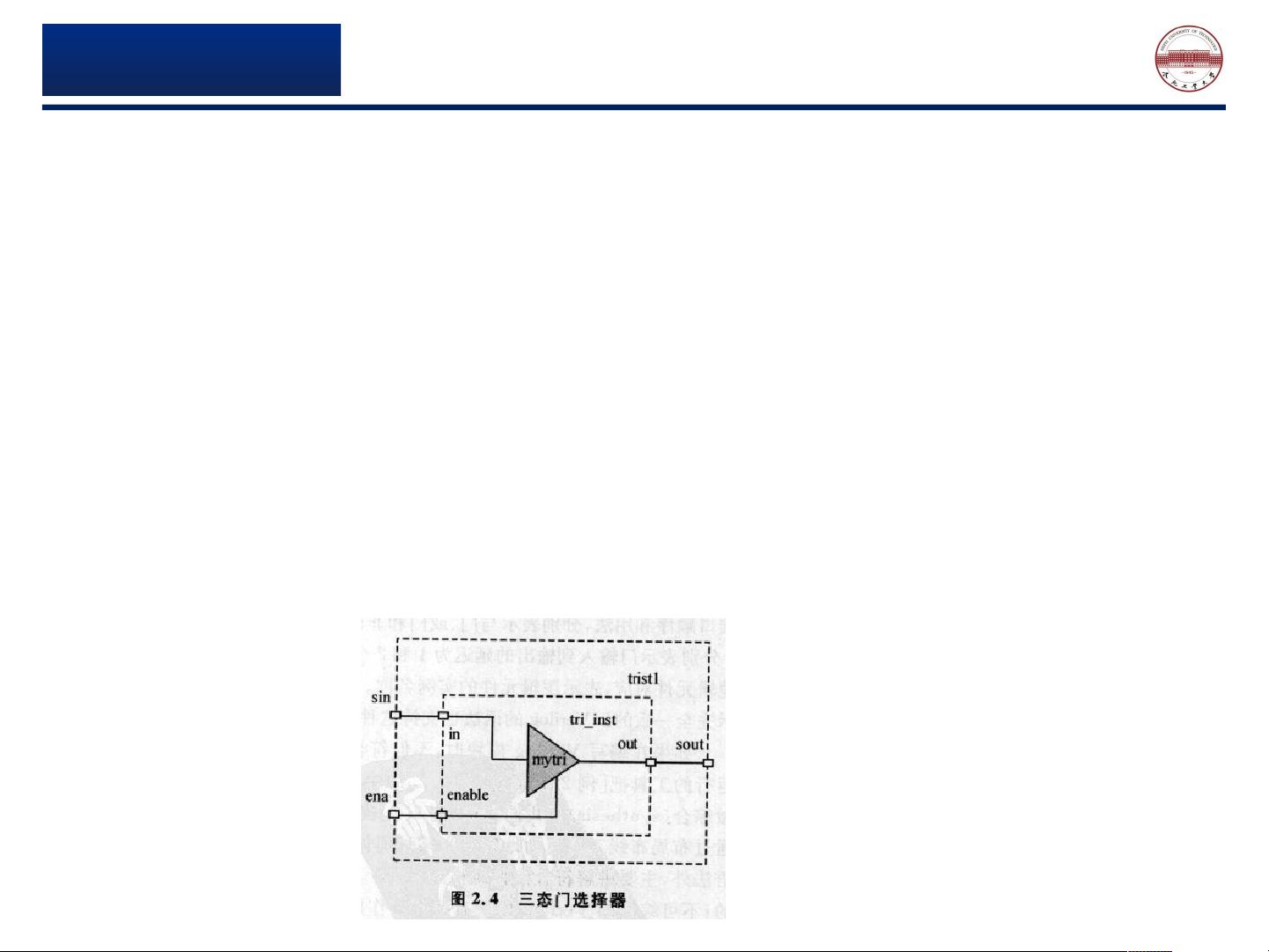

- 模块是Verilog HDL的基本单位,它代表一个独立的硬件实体,可以是一个逻辑门、触发器、计数器,甚至是整个系统。模块通过输入、输出接口与其他模块相互连接,构建复杂的电路。

- 模块可以包含输入、输出、双向端口,以及内部的寄存器和逻辑电路。

- 测试平台(testbench)是Verilog HDL中用于验证模块功能的重要部分,它模拟模块外部的输入信号和预期的输出,以检查设计的正确性。

2. Verilog HDL行为描述

- 行为描述语言允许设计者以数据流和控制流的方式描述硬件,包括顺序执行和并行执行的结构。

- 延迟和事件控制:可以指定操作的时间顺序,例如用`#delay`表示延迟,用`@`事件驱动语句来响应特定事件。

- 条件分支(if-else)、选择结构(case)、循环结构等程序控制语句,与C语言类似,使得设计更具可读性和可维护性。

- 任务(task)和函数(function)提供更高级的抽象,任务可以有参数和非零执行时间,函数则用于定义新的操作。

- 丰富的运算符支持算术、逻辑和位操作,帮助构建各种复杂的数字逻辑。

3. Verilog HDL的信号模型

- Verilog HDL提供了精确的信号建模,包括信号延迟和输出强度的概念,可以处理不确定性条件和信号的模糊值。

- 对于熟悉C语言的人来说,Verilog HDL的语法相对易懂,比如if和case语句,但需要理解硬件描述语言特有的特性,如事件驱动和并行执行。

4. Verilog模块示例

- 例2.1展示了一个简单的多路选择器(muxtwo)模块,它根据选择信号(sl)将输入a或b路由到输出out。`always @(a or b or sl)`是一个敏感列表,当这些信号变化时,`if`语句会重新计算out的值。

通过学习上述内容,初学者可以逐步了解并掌握Verilog HDL的基本语法和FPGA设计的基本流程。随着深入,还将涉及综合、仿真、布局布线等步骤,以实现完整的FPGA项目。在实践中,不断编写和验证模块,结合实际的硬件知识,将有助于提高FPGA设计技能。

2009-01-09 上传

2024-06-19 上传

2011-10-31 上传

2009-01-13 上传

点击了解资源详情

2024-12-22 上传

2024-12-22 上传

yang961001

- 粉丝: 0

- 资源: 2

最新资源

- HYActivityView(iPhone源代码)

- Nacos oracle专用

- rjmco-tfc-gcp-experiments:Terraform Cloud w GCP集成实验

- fontpath-renderer:字体路径字形的通用渲染器

- drl-trainers:深度强化模型训练师

- 手机APP控制,蓝牙LED彩灯制作+ARDUINO源码-电路方案

- Shoply-App-React-Redux

- JoliTypo:Web微型打字机修复程序

- FitnessTracker

- Android文字动画效果源代码

- GLSL-live-editor:基于 Codemirror 的 GLSL 实时编辑器

- 电子功用-大功率中频电源电子平波电抗器

- 基于AT89S52单片机的电子万年历(原理图+汇编程序)-电路方案

- SpeechMatics:简称语音自动识别(ASR),是一种技术,它可以使人们使用自己的声音通过计算机界面以一种最复杂的方式类似于普通人类对话的方式来讲话

- IVEngine(iPhone源代码)

- MATLAB神经网络优化算法.zip