ModelSim 中文使用教程:从入门到时序仿真实战

需积分: 50 70 浏览量

更新于2024-07-25

收藏 883KB PDF 举报

"modelsim使用目录 - MIPS代码示例及PLD设计流程"

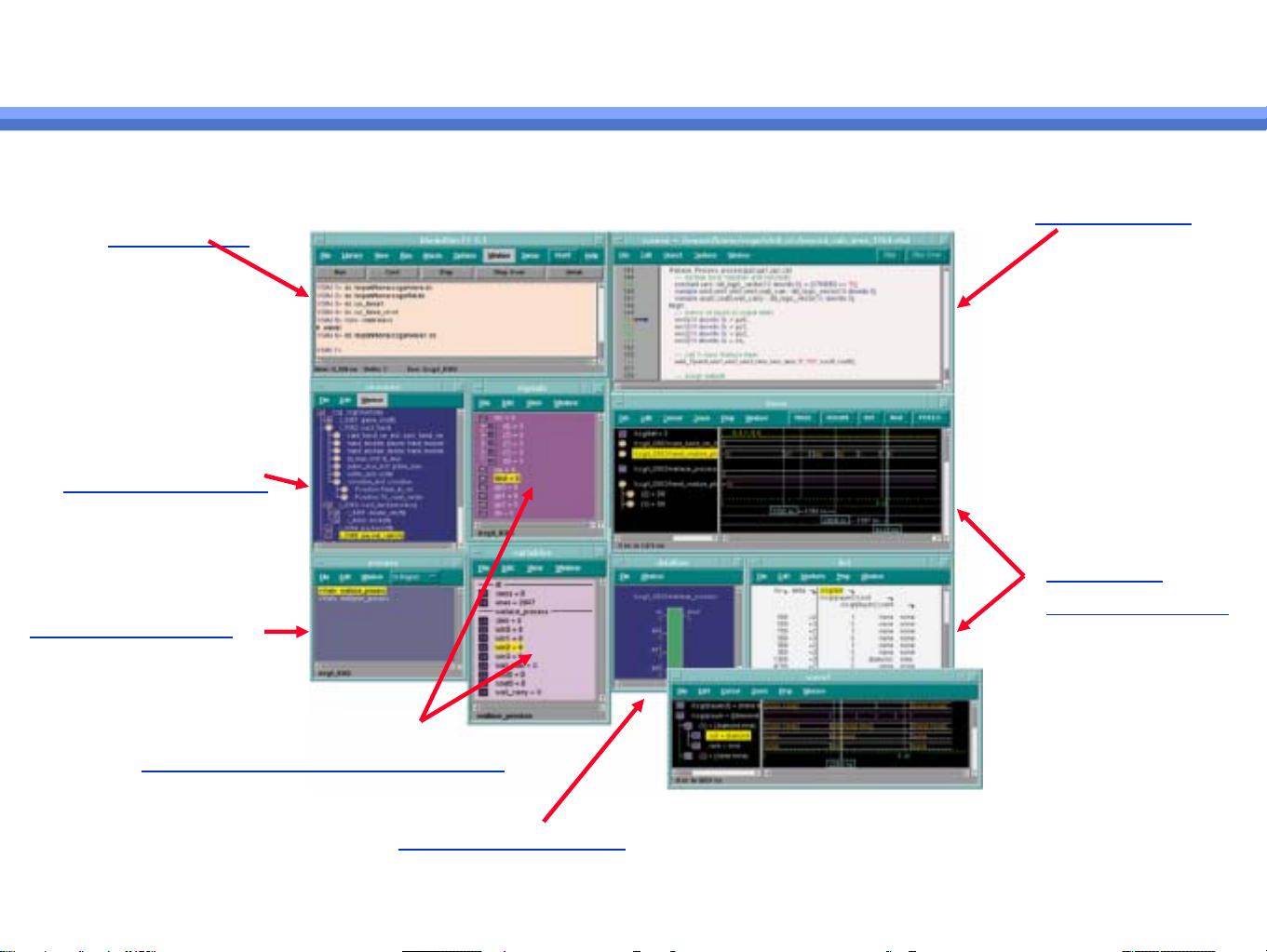

在电子设计自动化(EDA)领域,ModelSim是一款广泛使用的仿真工具,尤其在FPGA和ASIC设计中扮演着重要角色。该工具由Model Technology公司开发,现已被 Mentor Graphics 收购。ModelSim支持多种硬件描述语言,包括Verilog和VHDL,使得它成为工业界最通用的仿真器之一。

1. **PLD设计流程**

- 设计输入:这是设计的起点,涉及编写行为或结构描述,可以是Verilog或VHDL代码。

- RTL(寄存器传输级)仿真:使用ModelSim进行功能仿真,检查逻辑模型的功能正确性,但不考虑时间延迟。

- 综合:将RTL代码转换为目标工艺的门级表示,并进行优化以满足面积和性能要求。

- 布局和布线:映射设计到FPGA或ASIC的具体物理位置,分配布线资源。

- 门级仿真:在ModelSim中进行时序仿真,验证设计在实际工艺中的运行情况。

- 时序分析:评估设计是否满足速度和时序约束,可能需要对设计进行调整。

- 系统上验证:最终在实际硬件上进行测试和验证。

2. **ModelSim特性**

- 支持标准:ModelSim提供了对'87VHDL、'93VHDL、IEEE1364-95 Verilog、SDF 1.0-3.0、VITAL2.2b和VITAL '95等标准的支持。

- 用户友好的界面:提供通用平台,方便用户操作。

- 多版本:如ModelSim/VHDL、ModelSim/Verilog、ModelSim/LNL、ModelSim/PLUS和ModelSim/SE,满足不同用户需求。

- ModelSim/SE:作为主要版本,包含PLUS的所有功能并增加了额外特性。

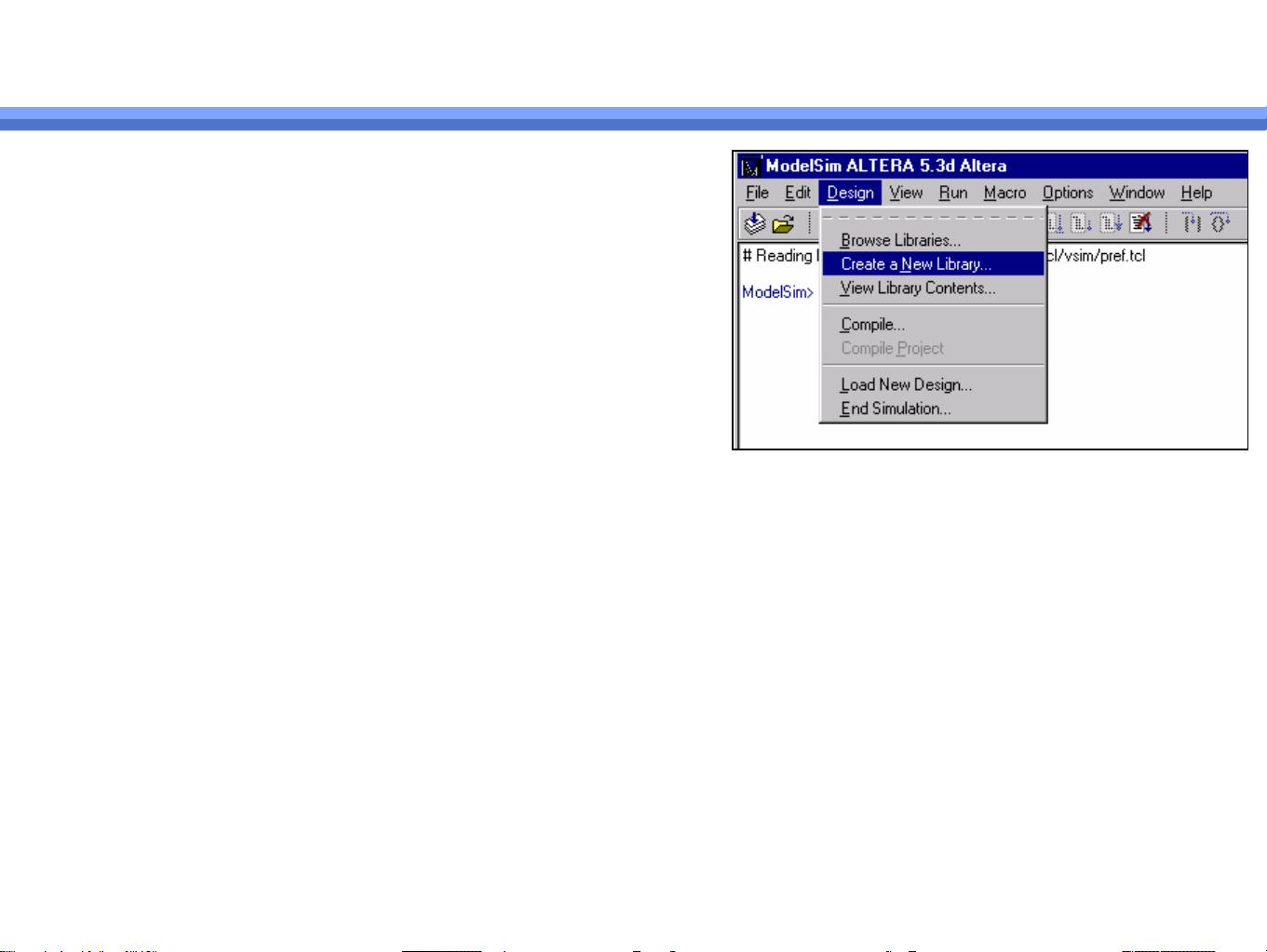

3. **ModelSim使用**

- 基本仿真步骤:这通常包括编译设计库、编译设计源码、创建仿真激励、运行仿真以及查看和分析结果。

- 用户界面:用户可以通过图形化界面进行各种操作,如设置仿真参数、查看波形图等。

- 功能仿真:用于验证设计在理想条件下的行为,不考虑实际时序。

- Quartus输出仿真文件:Quartus是Altera(现Intel FPGA)的综合工具,可以生成ModelSim所需的仿真网表和时序信息。

- 时序仿真:在更接近实际环境的条件下验证设计,考虑了时序和延迟,确保设计能够在目标硬件上正确运行。

4. **MIPS代码示例**

MIPS是一种常见的RISC指令集架构,经常用于教育和嵌入式系统设计。在ModelSim中,可以通过模拟MIPS处理器来验证和调试MIPS汇编代码或基于MIPS的硬件设计。这有助于理解处理器如何处理指令以及在硬件级别如何实现这些指令。

通过学习和掌握ModelSim的使用,设计师能够高效地验证和优化他们的数字电路设计,确保在实际硬件上实现预期的功能和性能。对于初学者和专业人士来说,了解并熟练运用ModelSim都是提高设计效率和质量的关键步骤。

2009-02-08 上传

2015-07-06 上传

2012-09-27 上传

2011-09-18 上传

2013-03-07 上传

2010-02-09 上传

kingzts

- 粉丝: 0

- 资源: 1

最新资源

- 火炬连体网络在MNIST的2D嵌入实现示例

- Angular插件增强Application Insights JavaScript SDK功能

- 实时三维重建:InfiniTAM的ros驱动应用

- Spring与Mybatis整合的配置与实践

- Vozy前端技术测试深入体验与模板参考

- React应用实现语音转文字功能介绍

- PHPMailer-6.6.4: PHP邮件收发类库的详细介绍

- Felineboard:为猫主人设计的交互式仪表板

- PGRFileManager:功能强大的开源Ajax文件管理器

- Pytest-Html定制测试报告与源代码封装教程

- Angular开发与部署指南:从创建到测试

- BASIC-BINARY-IPC系统:进程间通信的非阻塞接口

- LTK3D: Common Lisp中的基础3D图形实现

- Timer-Counter-Lister:官方源代码及更新发布

- Galaxia REST API:面向地球问题的解决方案

- Node.js模块:随机动物实例教程与源码解析