Cadence仿真教程:源同步时序电路分析

"Cadence中文教程提供了完整的Cadence仿真操作指导,特别关注时序计算和仿真结果的应用,适合电子设计自动化(EDA)领域的学习者和从业者。教程深入解析如何利用Cadence工具进行有效的时序分析,确保电路设计满足严格的时序约束。"

在Cadence仿真中,时序计算和分析是至关重要的,它涉及到电路性能和可靠性。时序计算的目标是确定数据信号与时钟信号之间的关系,以确保在接收端能够满足建立时间(Tsetup)和保持时间(Thold)的要求。建立时间是指数据必须在时钟边缘之前稳定的时间,而保持时间是指数据必须在时钟边缘之后保持稳定的时间。

时序计算通常包括以下关键参数:

1. 时钟到数据输出有效时间(Tco):这是指时钟信号作用于器件后,数据输出达到稳定状态所需的时间。

2. 信号传输时间(Tflytime):信号从一个位置传输到另一个位置所需的时间,要考虑PCB布线的影响。

3. 时钟抖动(Tjitter):时钟信号的随机偏差,可能影响时序的精确性。

4. 共同时钟的相位偏移(Tskew):在分布式系统中,时钟信号到达不同组件的时间差。

5. 负载效应:数据信号驱动的负载对信号延迟的影响。

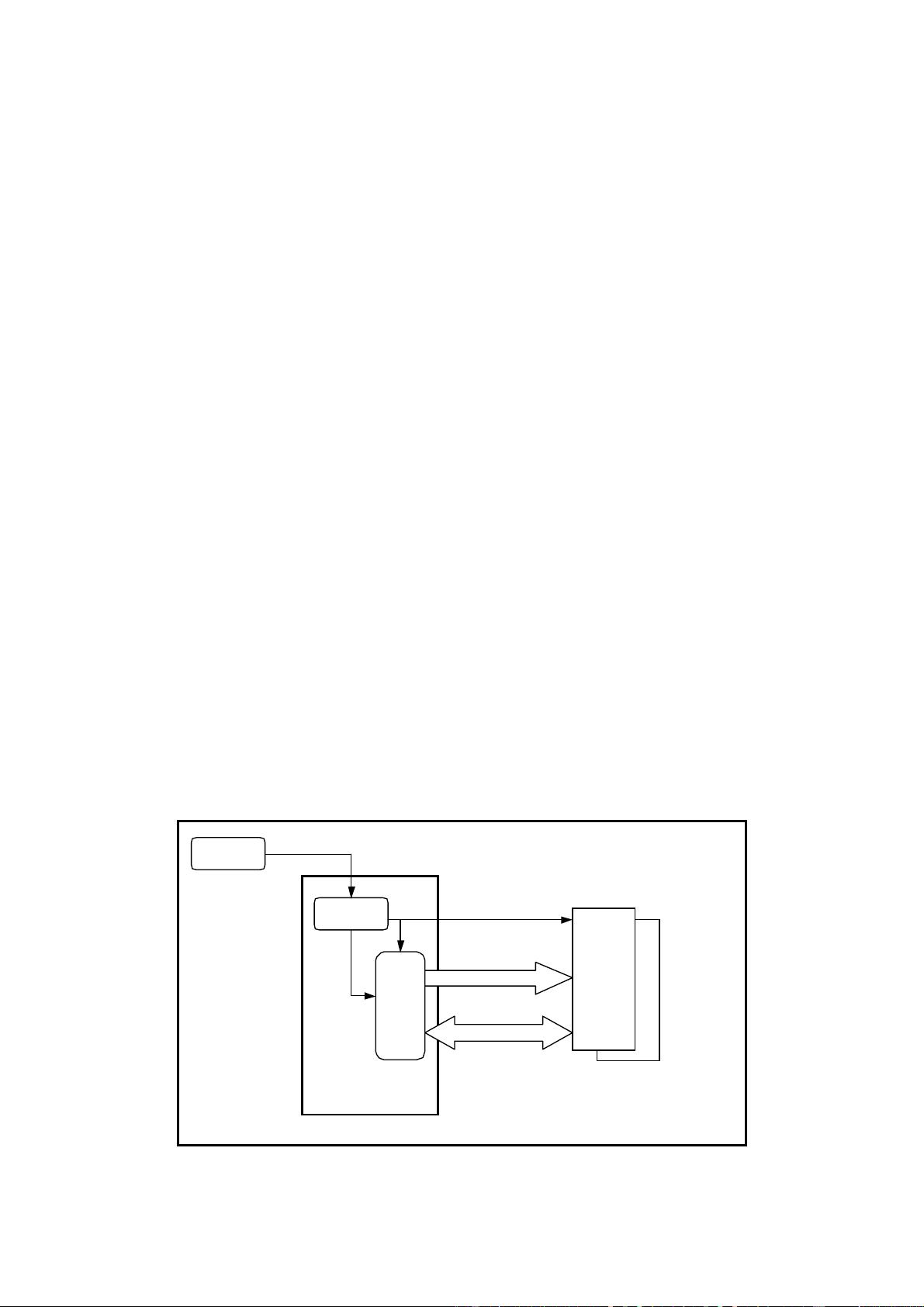

时序电路有两种主要类型:源同步时序电路和共同时钟同步电路。源同步时序电路中,时钟和数据由同一源头提供,如图1所示的CPU驱动到SDRAM的时钟。这种情况下,时序分析更复杂,因为时钟和数据可能同时经历传输延迟。

图2展示了数据和时钟同步传输的情况,其中标记了多个关键时间参数,例如Tsetup'和Thold'分别代表SDRAM的输入建立时间和保持时间,Tco_min和Tco_max表示数据输出的最小和最大时间,Tft_clk和Tft_data是时钟和数据的传输延迟,而Tcycle是时钟周期。

Cadence仿真工具,如SPECCTRAQuest,能够帮助设计师进行这些复杂的时序计算和分析。通过这些工具,设计师可以提取仿真结果,理解每个参数的实际意义,并将这些结果应用到时序计算公式中,以验证设计是否符合性能要求。

在进行时序仿真时,需要正确解读仿真结果,包括但不限于信号延迟、时钟抖动分析、时钟偏移以及数据保持时间的检查。只有全面理解这些结果,才能有效地优化设计,避免潜在的时序问题,确保电路的稳定运行。因此,掌握Cadence仿真工具的使用是成功进行数字集成电路设计的关键步骤。

1588 浏览量

5170 浏览量

385 浏览量

344 浏览量

2010-01-27 上传

234 浏览量

259 浏览量

点击了解资源详情

210 浏览量

whusjtu2013

- 粉丝: 0

- 资源: 2

最新资源

- 为什么选择网站:为什么要回购

- country-details

- Cuaderno de Bitácora:因为成为一名优秀的化学家从来都不是一件容易的事......-开源

- python-pure-cdb:纯Python CDB读写器

- socketio-boilerplate:超级简单的socket.io服务器模板

- ueditor-demo-master.zip

- 人事培训主管岗位说明书

- TODOs-list:TODO列表网站

- PayACoffeeWordPress:重新定义互联网捐赠。 加入以简单方式发送捐款的新标准

- node-typescript-mongodb-rest-api骨架

- res.github.io

- 小区保安员培训大全

- ShoeShop:Java和SQL

- market-management

- 小程序猫眼电影含node后端

- Lab5_exception