Verilog Lab01:数字VLSI设计全流程详解与实验步骤

需积分: 15 182 浏览量

更新于2024-09-07

收藏 1.32MB DOCX 举报

Verilog数字VLSI设计教程Lab01详细流程提供了一个全面的指南,旨在帮助学习者理解并实践Verilog语言在数字集成电路(VLSI)设计中的应用。本教程涵盖了从基本设置到实际设计过程的各个环节。

首先,教程开始于对Extras.inc文件的处理。有两种方法来管理这个文件:一是创建一个名为VCS的子目录并在其下放置Extras.inc,然后在TestBench.v文件中通过`include`指令引用;另一种方法是直接将Extras.inc包含到需要的地方,简化了文件结构。

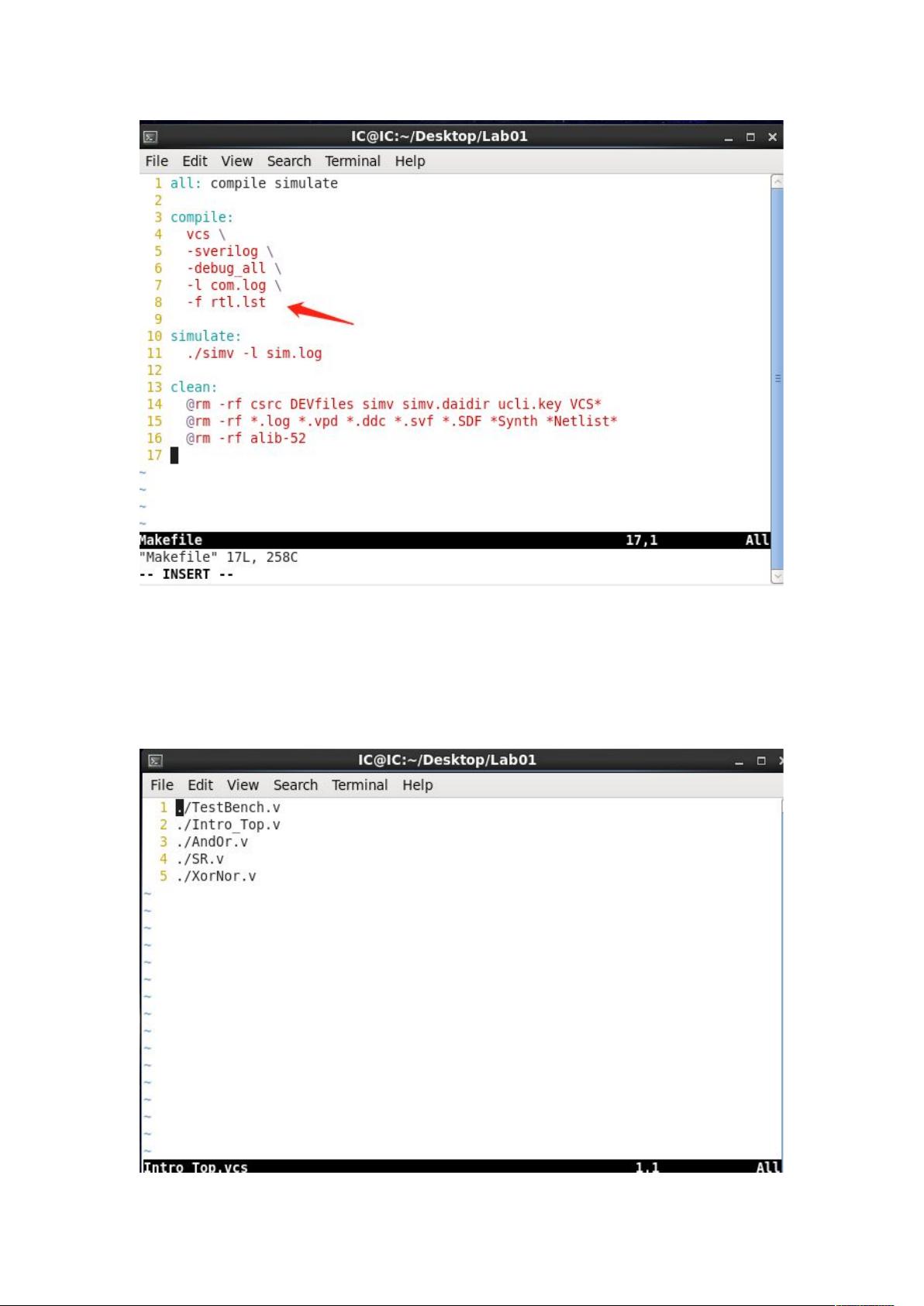

接下来是编写Makefile,这是一个自动化构建工具,用于协调编译、链接和运行过程,确保所有依赖项正确编译并整合到一起。Makefile通常根据源文件的依赖关系自动生成,便于管理和维护项目。

`rtl.lst`(Intro_Top.vcs)文件在这里起到了配置的作用,它可能是一个包含了Verilog模块实例化列表的文件,用于VCS工具进行仿真时指定需要编译的模块。

执行`make`命令后,会触发编译和模拟过程,这将生成一系列文件,包括波形文件(如.vcd),这些文件用于调试和验证设计的正确性。通过DVE(Design Vision Environment)工具,用户可以打开这些波形文件,进行细致的时序分析。

在Lab01目录的同级创建library文件夹,其中包含各种库文件,如typical.db、typical.lib等,这些库文件定义了标准的电路元件模型和设计规范,对于复用和标准化设计至关重要。典型的电路模块如And、Or、SR和XORNot也被分别定义和测试。

编写`Intro_Top.tcl`文件(源自Intro_Top.src),这是一个脚本文件,用于与VCS工具交互,进行设计验证。在这个阶段,用户可能执行设计视图(design_vision)并加载电路网络列表(Intro_TopNetlist.v),接着分析电路并加入And、Or、SR和XORNot等子模块进行测试。

最后,通过运行`dc_shell-t-fIntro_Top.tcl`命令启动设计环境的命令行界面,用户可以执行设计分析脚本,确认设计功能是否符合预期。整个流程强调了从头到尾的实际操作步骤,帮助学习者掌握Verilog语言在数字VLSI设计中的实践应用。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-07-14 上传

2022-06-20 上传

2020-03-09 上传

2019-10-11 上传

2023-02-20 上传

2011-11-28 上传

lezai160

- 粉丝: 1

- 资源: 5

最新资源

- 数据-行业数据-天立教育:2020年度报告.rar

- 硬件记录

- Pytorch 快速入门实战之 Fashionmnist

- 程序等待-易语言

- zabbix-html-email-template:可自定义的Zabbix HTML电子邮件模板-ProblemRecovery

- set-compose-tags

- DotinPolygonAlgorithm:DotinPolygon算法

- 行业分类-设备装置-可记录媒体的分离装置.zip

- WindowsFormsApplication1.rar

- 仿QQ登录界面-易语言

- IBM应用数据科学Capstone

- Python库 | outlier_akashjindal347-0.0.1-py3-none-any.whl

- TheWorldBetweenUs:豆瓣评论分析

- bgpvis:bgpdump数据分析

- plasmid_mapR:用于在整个基因组序列数据集中进行质量计算和可视化参考质粒覆盖范围的软件包

- 行业分类-设备装置-叶片平台的冷却.zip