Xilinx FPGA设计优化技巧详解

需积分: 9 113 浏览量

更新于2024-07-26

收藏 2.94MB PDF 举报

"FPGA设计高级技巧Xilinx篇"

本文档是关于FPGA设计高级技巧的专著,聚焦于Xilinx公司的产品。这份资料由深圳市华为技术有限公司的研究管理部文档中心编撰,旨在深入探讨FPGA设计中的优化策略,提高设计效率和性能。以下是文档中涉及的一些关键知识点:

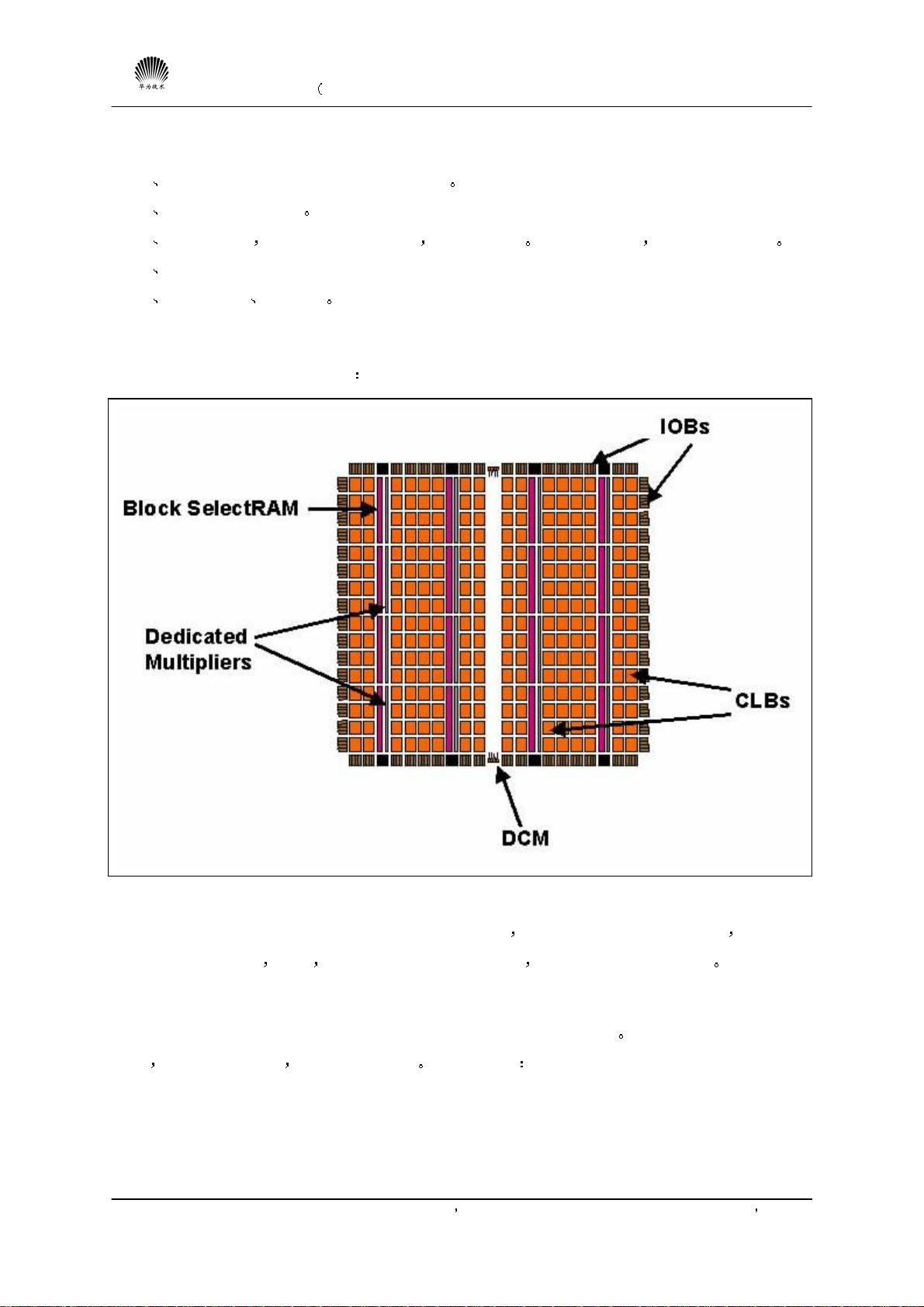

1. **FPGA结构**:

- FPGA的结构分为CLB(Configurable Logic Block)、Slice、LUT(查找表)、Shift Register LUT (SRL)、MUXFX、CarryLogic和ArithmeticLogicGates、FFX/FFY(Flip-Flops)等基本单元。

- CLB是FPGA的基本逻辑构建块,可以被配置为各种组合逻辑或时序逻辑功能。

- Slice包含LUT,用于实现用户定义的逻辑函数,而SRL用于存储数据并进行移位操作。

- MUXFX和CarryLogic组件用于实现多路复用和算术运算。

2. **内存资源**:

- 分布式RAM (Distributed RAM) 和BlockRAM是FPGA中的存储资源,适用于不同的应用需求。

- BlockRAM通常用于实现大容量存储,而Distributed RAM则更适用于分布式存储和高速访问。

3. **I/O资源**:

- IOB(Input/Output Blocks)是FPGA的外部接口,包含多种配置选项如CLKMUX、DCI、SelectI/O,以适应不同速度和信号质量要求。

4. **时钟资源**:

- Global Clock、CLKMUX和DCM(Differential Clock Multiplier)是FPGA中的重要时钟管理单元,用于时钟分发和频率转换,以优化系统时钟性能。

5. **设计技巧**:

- 合理选择加法电路,包括串行进位和超前进位,可以影响逻辑级数和速度。

- 使用圆括号处理多个加法器可以减少逻辑级数,从而提高速度。

- IF语句和Case语句在FPGA设计中的使用策略会影响设计的速度和面积。

- BlockSelectRAM的内部结构分析有助于更有效地利用存储资源。

6. **速度与面积关系**:

- 通过优化逻辑级数和资源使用,可以在不显著增加门数的情况下提高速度,同时减少资源占用。

7. **DCM**:

- DCM用于频率倍增、分频和相位平移,是FPGA中的重要时钟管理技术。

这些知识点详细阐述了FPGA设计的关键技术和优化方法,对于理解Xilinx FPGA的内部工作原理以及如何进行高效设计具有指导价值。通过对这些技巧的学习和实践,设计者可以更好地优化其FPGA设计,实现高性能和低功耗的目标。

676 浏览量

152 浏览量

155 浏览量

126 浏览量

197 浏览量

181 浏览量

224 浏览量

aidongmingweizai

- 粉丝: 0

- 资源: 31

最新资源

- Pokemon-App

- 变焦级镜考勤

- English to Bengali Dictionary | BDWord-crx插件

- ACAM_Demo:工作演员条件注意地图的实时动作检测演示。 此回购包括用于人员检测的完整管道,用于实时跟踪和分析其行为

- FE内容付费系统响应式 带手机版 v5.42

- matlab的slam代码-16-833:机器人定位和地图绘制-2019年Spring[CMU]

- 快乐的地方

- payment-integration-project:作为Sparks Foundation的GRIP实习的一部分,完成了Payment Gateway集成项目

- 一款简单的潜艇大战游戏

- 智睿政务问卷调查系统 v10.9.0

- olive-dolphin-prophecy

- 2019国赛C题资源(1).zip

- ElvishElvis.github.io

- grape-oink:Grape 的中间件,允许使用 Oink

- buyers-remorse-app:一个基于React的Web应用程序,以提高个人对购买选择的认识

- TinyPNG For Photoshop