高速示波器:160 GS/s等效采样系统设计及性能优化

3 浏览量

更新于2024-09-01

收藏 446KB PDF 举报

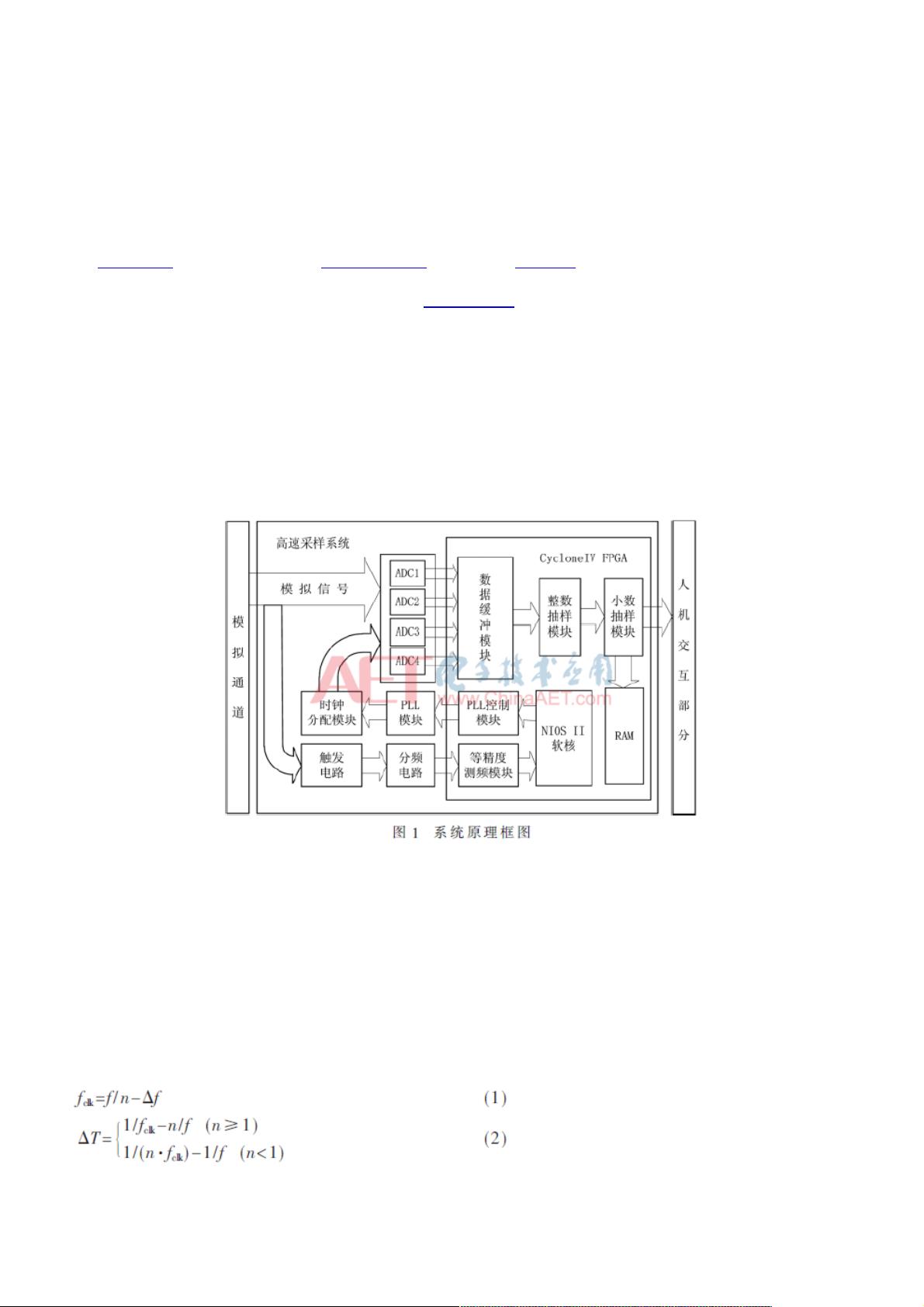

高速示波器等效采样系统设计的关键在于采用了小数分频锁相环技术,以ADF4351芯片作为核心组件。这种锁相环技术的优势在于能够根据被测信号频率的变化动态调整采样率,从而在处理高频信号时展现出优越的性能。系统利用FPGA进行精确的频率测量和控制,确保等效采样过程的准确性。

系统的核心设计包括以下几个步骤:首先,触发电路和分频电路生成测频用的方波,接着,测频模块测量输入信号的频率,然后通过嵌入式NIOSII软核中的程序计算出适应的采样时钟频率,驱动锁相环模块生成稳定的采样时钟。ADC在这一时钟的驱动下进行采样,采集的数据经过数据缓冲、整数抽样和小数抽样模块处理,以消除冗余点并修正误差,确保等效采样率的准确。

为了实现更高的实时采样率,系统采用了时间交替采样策略。通过时钟分配器和数字延迟线,将锁相环产生的时钟分为四路,每一路延迟不同比例的时钟周期,形成90度相位差的交替采样时钟。这样,即使使用四个最高250 MS/s的8 bit ADC(如AD9481),也能通过这种方式组合,达到1 GS/s的总采样速率,从而适应不同信号类型的捕获需求。

小数分频锁相环技术的优点在于它能提供低抖动的时钟源,这在宽广的设计带宽(DC到500 MHz)内确保了系统良好的噪声性能,信噪比明显优于基于DDS技术的传统方案。这使得该系统在高速示波器应用中表现出优异的稳定性和有效性。

总结来说,这个设计通过创新的锁相环技术和时间交替采样方法,不仅提升了等效采样的速度,还优化了信号质量,使得高速示波器在处理复杂频率范围内的信号时表现出色。这对于科研和工程应用来说,是一个重要的技术创新。

2022-08-04 上传

163 浏览量

161 浏览量

2024-04-15 上传

116 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

weixin_38689477

- 粉丝: 2

最新资源

- 易二维码签到系统:会议活动签到解决方案

- Ceres库与SDK集成指南:C++环境配置及测试程序

- 深入理解Servlet与JSP技术应用与源码分析

- 初学者指南:掌握VC摄像头抓图源代码实现

- Java实现头像剪裁与上传的camera.swf组件

- FileTime 2013汉化版:单文件修改文件时间的利器

- 波斯语话语项目:实现discourse-persian配置指南

- MP4视频文件数据恢复工具介绍

- 微信与支付宝支付功能封装工具类介绍

- 深入浅出HOOK编程技术与应用

- Jettison 1.0.1源码与Jar包免费下载

- JavaCSV.jar: 解析CSV文档的Java必备工具

- Django音乐网站项目开发指南

- 功能全面的FTP客户端软件FlashFXP_3.6.0.1240_SC发布

- 利用卷积神经网络在Torch 7中实现声学事件检测研究

- 精选网站设计公司官网模板推荐