i.MX6SoloLite CPU Datasheet: Low-Power Multimedia Processor for ...

需积分: 1 140 浏览量

更新于2024-07-16

收藏 1MB PDF 举报

本文档是Freescale半导体提供的MCIMX6LxDVN10xx CPU的数据手册,针对的是Kindle等电子墨水阅读器使用的低功耗处理器。该处理器采用了先进的ARM Cortex-A9 MPCore架构,最高运行速度可达1GHz,集成了2D图形处理器,以及高度优化的电源管理功能。这款单核处理器在保证高性能的同时,着重于节省能源,非常适合对功耗有极高要求的应用场景。

i.MX6SoloLite处理器的特点包括:

1. 性能与效率:基于ARM Cortex-A9架构,它提供了一个高效能的核心,可以处理多任务,同时保持低功耗。这对于电子阅读设备至关重要,因为长时间使用而不会迅速消耗电池。

2. 多媒体支持:内置2D图形处理器,使得处理图像和视频显示更为流畅,对于电子书中的插图和文字渲染能力强大。

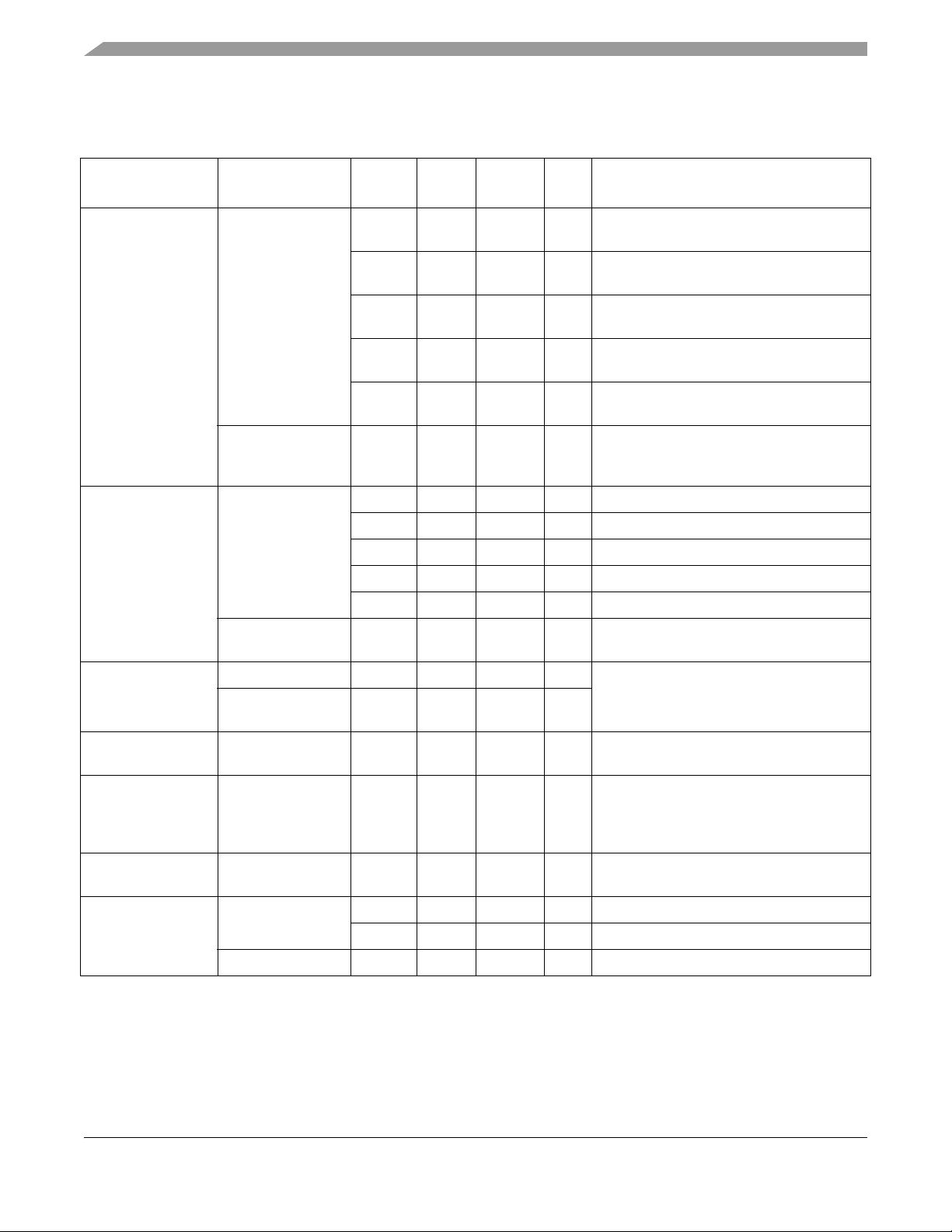

3. 内存接口:支持32位DDR3-800内存接口,这确保了数据传输的高速和稳定,提高了系统的响应速度。

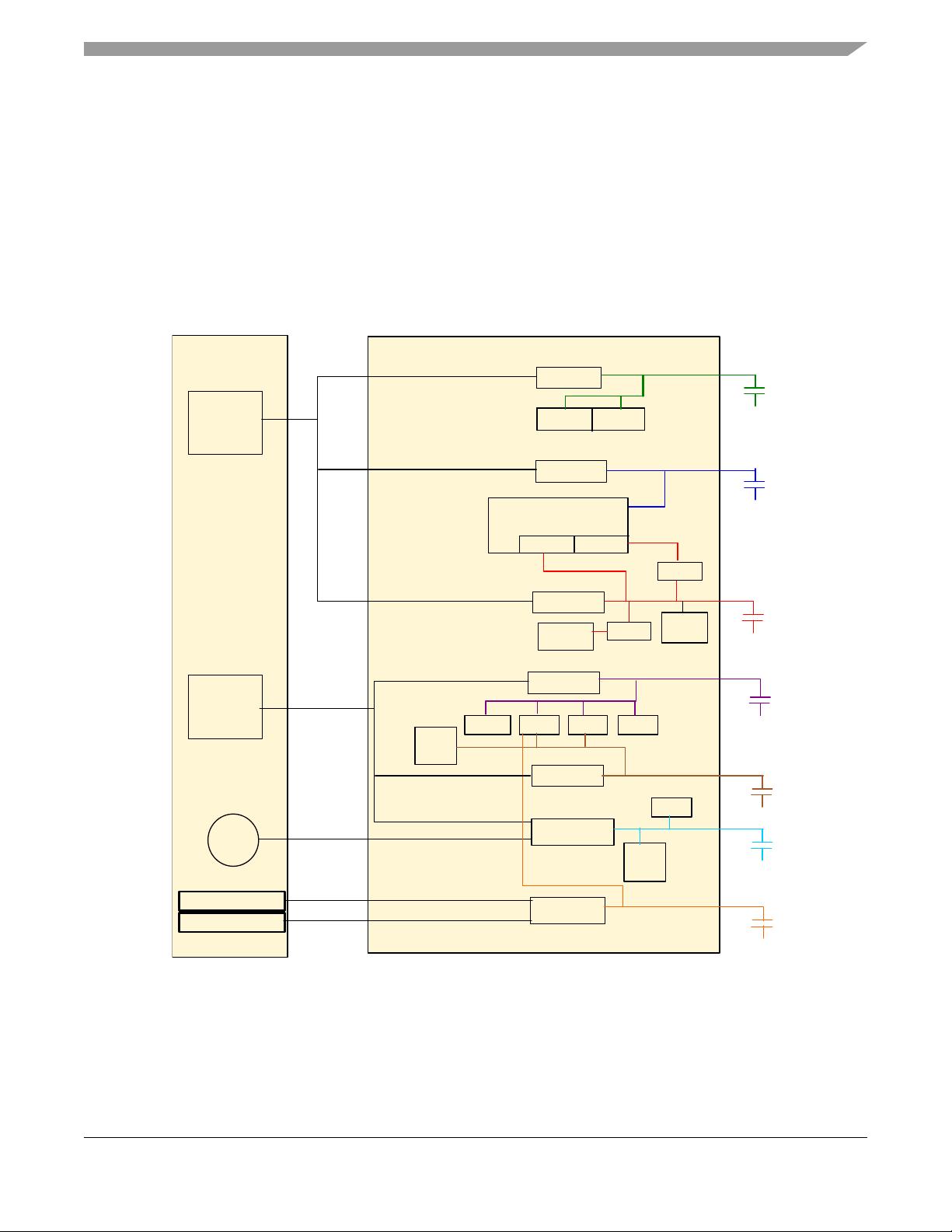

4. 丰富的外设连接:处理器内置了多种接口,如WLAN、蓝牙、GPS、硬盘接口、显示接口以及摄像头传感器接口,为外部设备提供了广泛的连接选项,方便与其他硬件组件集成。

5. 应用领域:由于其低功耗特性,MCIMX6LxDVN10xx特别适用于需要长时间待机且对能耗敏感的设备,如电子阅读器、智能手表、物联网设备等。

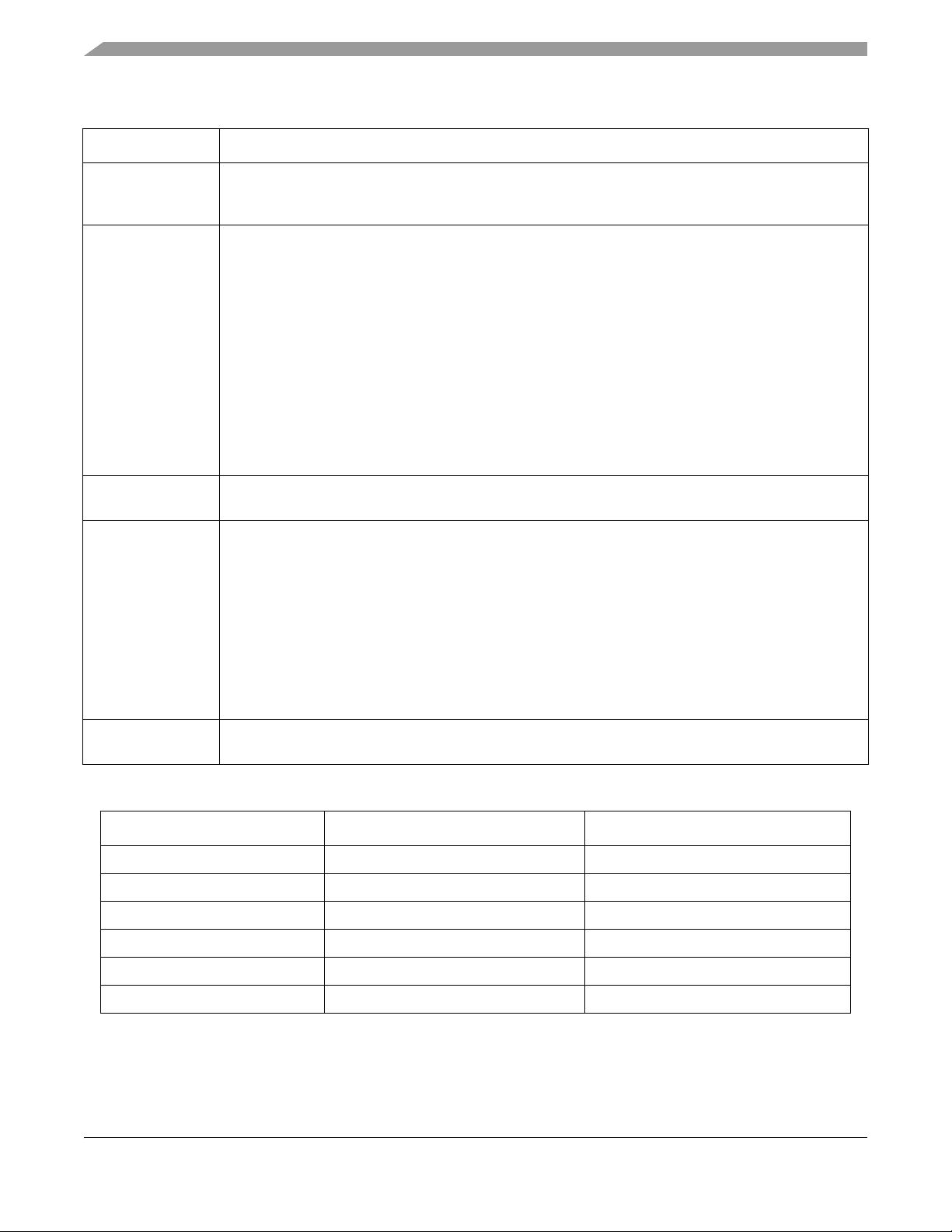

6. 文档结构:文档提供了详细的订单信息(见第3页表1),说明了产品的订购方式和规格参数,便于工程师在设计和选择硬件时参考。

总结来说,MCIMX6LxDVN10xx是一款专为多媒体应用而设计的高性能低功耗处理器,通过集成的先进技术,实现了在电子墨水设备中的高效能和长续航。对于了解和使用这款CPU的开发者和系统设计师来说,这份数据手册提供了关键的技术细节和配置信息。

259 浏览量

225 浏览量

131 浏览量

2021-07-05 上传

467 浏览量

mark304188

- 粉丝: 16

- 资源: 16

最新资源

- Potlatch_Server:看一场你无法独享的日落; 一幅让你叹为观止的风景,一幅触动你个人的画面? 然后拍摄一张照片,添加一些文字或诗歌来传达您的想法,然后使用 Potlatch 将其提供给其他人。 你的想法和图像能触动世界各地的人们吗? 谁是最伟大的礼物赠送者? 用 Potlatch 找出答案。 (potlatch这个词来自奇努克的行话,意思是“赠送”或“礼物”,是加拿大和美国太平洋西北海岸原住民举行的送礼盛宴)

- 可爱小老虎图标下载

- 虚拟舞蹈委员会

- applifecycle-backend-e2e:应用程序生命周期后端的e2e测试库

- AP-Elektronica-ICT:AP Hogeschool Antwerp的电子信息通信技术课程的公共GitHub页面

- USBWriter-1.3的源码

- AdBlockID-Plus_realodix:AdBlockID Plus测试

- 初级java笔试题-english-dictionary:英语词典

- vue-height-tween-transition:补间过渡项目的父项的高度

- 搞怪松鼠图标下载

- minimal-app:最小的Phonegap应用

- libmp3lame.a(3.100).zip

- 多彩变色龙图标下载

- 实现可以扫描生成二维码的功能

- LittleProjects:Coursera的Little Projects

- SingleInstanceApp:WPF单实例应用程序