篮球竞赛30s定时器电路设计详解与40161应用

需积分: 14 115 浏览量

更新于2024-07-25

收藏 391KB PPT 举报

本资源主要介绍了一个关于24s篮球竞赛定时器的电子电路设计实验,适用于学习者深入了解篮球比赛计时系统的工作原理。设计目标包括一个30s计时功能,具备外部操作开关控制的清零、启动和暂停/连续功能,并且计时器采用递减模式,每秒递减一次,直到计时到零时会触发光电报警并保持数码显示器亮灯。

设计过程分为几个关键部分:

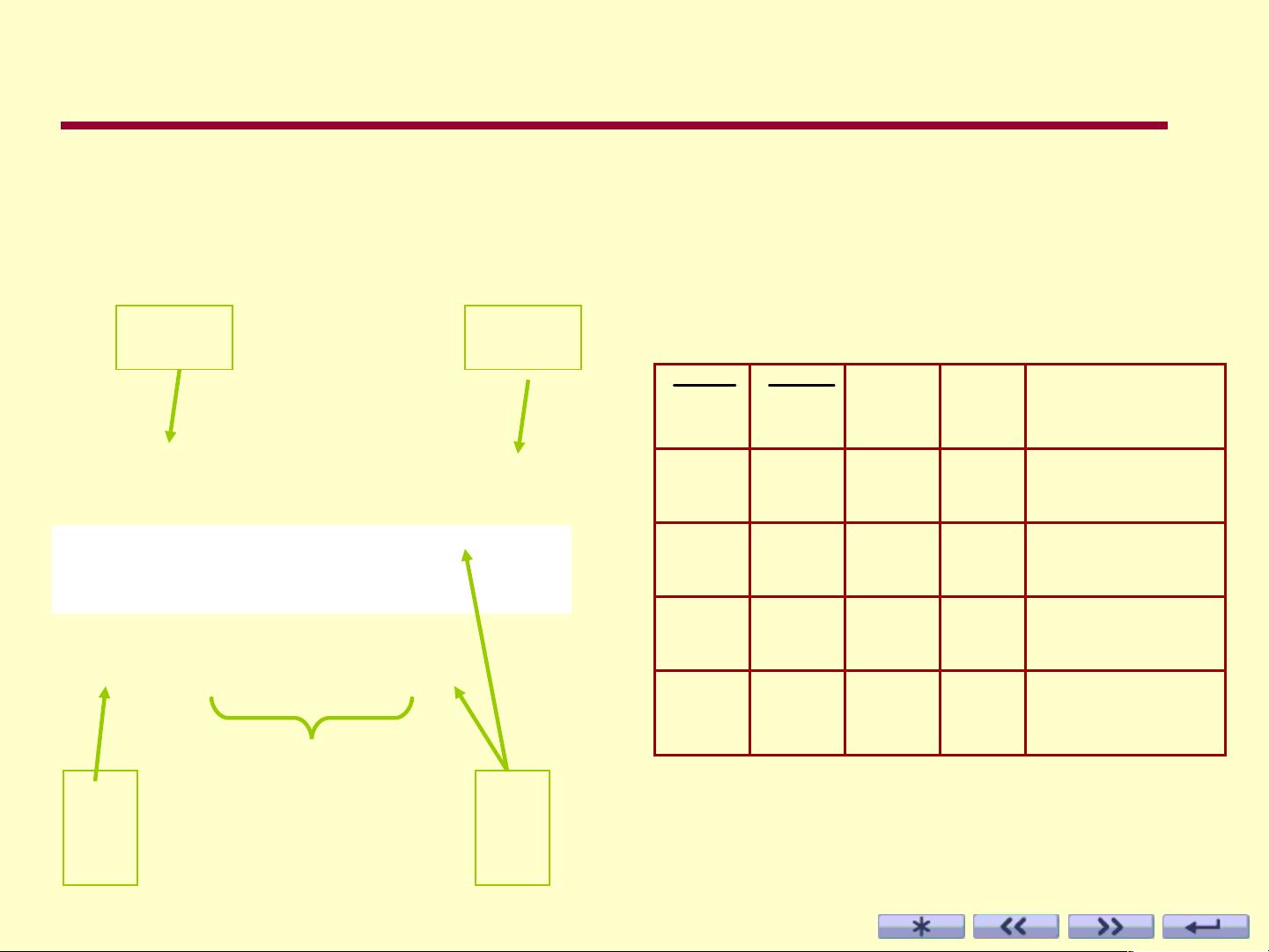

1. 30s定时器设计:设计的核心组件是30s计时器,它可以通过不同类型的IC芯片实现,如使用具有递减计数功能的芯片,如CPLD,或者通过组合如40161这样的同步计数器来构建。40161是一个4位二进制同步加计数器,可以用来实现秒脉冲的发生和计数功能。设计者需要考虑如何利用它的预置、清零和保持功能,以及同步与异步操作方式,以确保计时的准确性。

2. 秒脉冲发生器:设计中提到可以使用555定时器或石英晶体振荡器作为基础,这些元件能够产生稳定的秒脉冲,驱动计数器进行计时。设计时需要关注清零、预置和保持等操作的时机,确保秒脉冲的产生与计数的同步。

3. 译码和显示电路:这部分负责将计数结果转换成易于读取的形式,通常通过译码器将二进制计数值转换为相应的数码显示,比如7段数码管。这一步是整个设计中的难点,可能需要通过试凑法来优化电路结构。

4. 控制电路:这是整个系统的指挥中心,它负责接收外部操作开关的指令,控制计时器的启动、暂停、连续和清零功能。这部分设计需要灵活且精确,确保操作响应及时且无误。

5. 报警电路:当计时器递减到零时,电路会触发光电报警信号,可能通过继电器或其他形式的输出设备实现,以便在比赛过程中及时提醒相关人员。

在整个设计过程中,需要注意的是,电路设计不仅要满足功能需求,还要考虑电路的稳定性和可靠性,确保在实际应用中能稳定、准确地执行计时任务。此外,电源管理、接口设计以及可能的故障处理也是不可忽视的部分。通过这个实验,学习者可以深入理解数字电子技术在实际应用场景中的应用和调试技巧。

118 浏览量

点击了解资源详情

点击了解资源详情

118 浏览量

631 浏览量

631 浏览量

2021-09-29 上传

363 浏览量

2013 浏览量

xhroop

- 粉丝: 0

- 资源: 1

最新资源

- 图书馆管理信息系统.rar

- 教育培训宣传专题网页模板

- UI_DialogPlus:通过在根视图添加视图实现的Dialog效果缺点是层级不是那么的明显

- web:SoftNB网站

- 类似IOS弹性滚动视图效果

- datastructures-ES6:ES6中的数据结构

- emacs-customize-101-jp:想写一篇自定义Emacs的介绍(欲望)

- ssh整合_jar包.zip

- 网络游戏-基于遗传神经网络的矿山通风系统故障判断方法.zip

- 基于设计模式的俄罗斯方块程序

- Cpp编程:C ++编程问题

- Appcover-crx插件

- free-codes.github.io:只是测试

- vigir_wide_angle_image_proc:包含与处理广角鱼眼镜头图像有关的软件包

- CMS登录界面网页模板

- robo3t-1.3.1