DC中文教程:详解Design Compiler使用与设置

Design Compiler是一款在数字集成电路后端设计中广泛应用的工具,本文档是一份难得的中文教程,详细讲解了如何有效地利用它进行综合设计流程。以下是本文的核心知识点:

1. **系统环境设置**:

首先,用户需要确保系统的环境配置正确,包括将Synopsys Design Compiler的相关路径添加到`.cshrc`文件中,以便于后续调用。通过命令行操作,如`cat`、`source`等来设置环境变量。

2. **默认合成流程**:

文档介绍了如何执行默认的Synthesis流程,这可能包括设置设计规范(Design SPEC),这是关键步骤,因为它定义了电路的行为预期和性能目标。

3. **设计约束设置**:

对于组合逻辑电路,重点在于设置定时约束(Timing constraints),以确保电路满足速度和功耗的要求。对于时序电路,需要指定时钟、输入延迟和输出延迟,这些都是影响电路性能的重要因素。

4. **顺序电路处理**:

用户指南指导如何正确处理时序逻辑,包括设定clock信号以及输入和输出延迟,这对于保持电路的时序一致性至关重要。

5. **避免tri_state叙述**:

提醒读者,在SYNOPSYS输出的Verilog文件中,不能包含tri_state(三态)的描述,因为这可能与Cadence的工具兼容性问题有关。

6. **自定义库的使用**:

用户可以创建并定义自己的细胞库(Verilog模型),并通过Synopsys的转换程序将其转换为所需的.db文件(二进制文件),以便在设计中引用。

7. **.synopsys_dc.setupFile**:

这个文件是关键的配置文件,用于指定Design Compiler启动时的参数和使用的库。用户可以直接在该文件中设置搜索路径,通常包含本地或预定义的库目录。

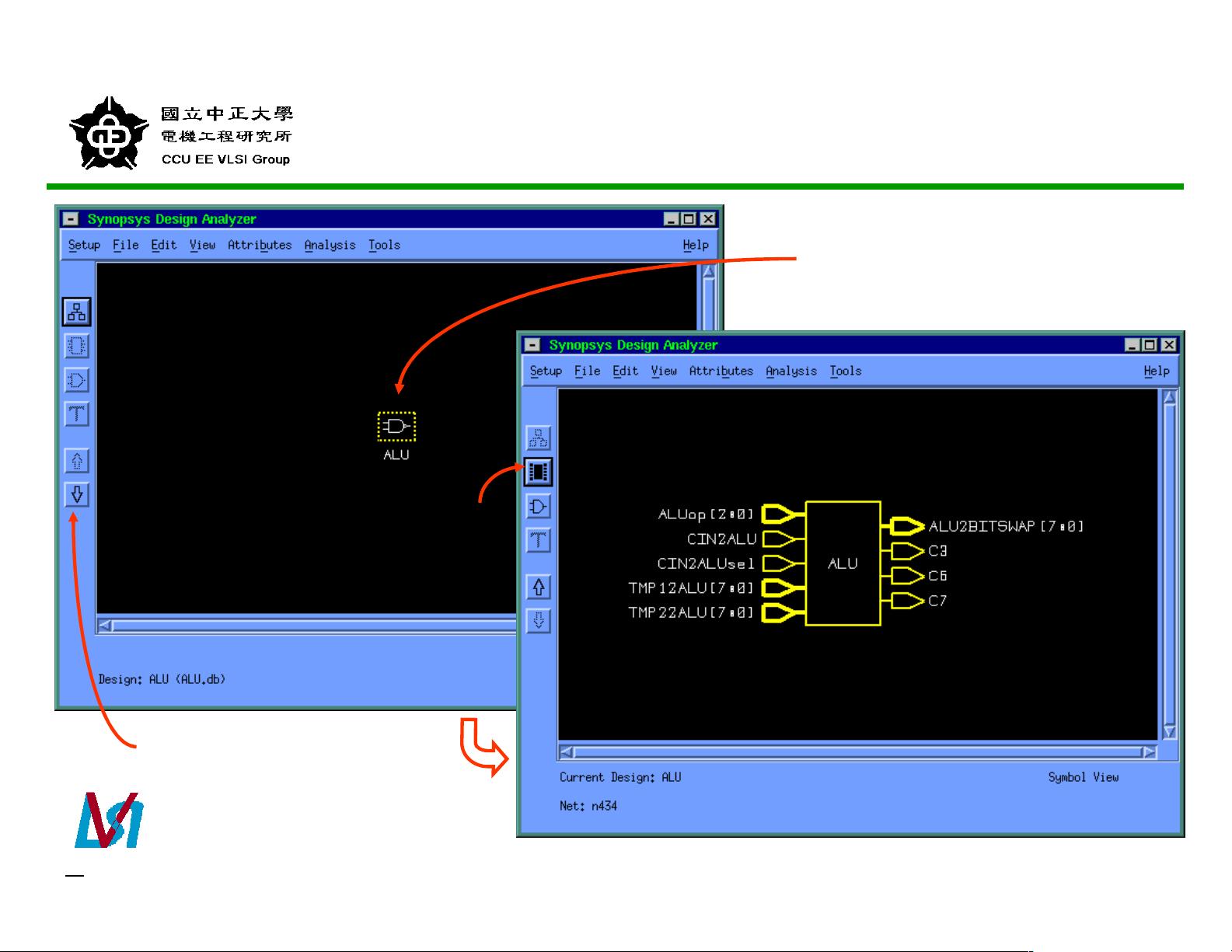

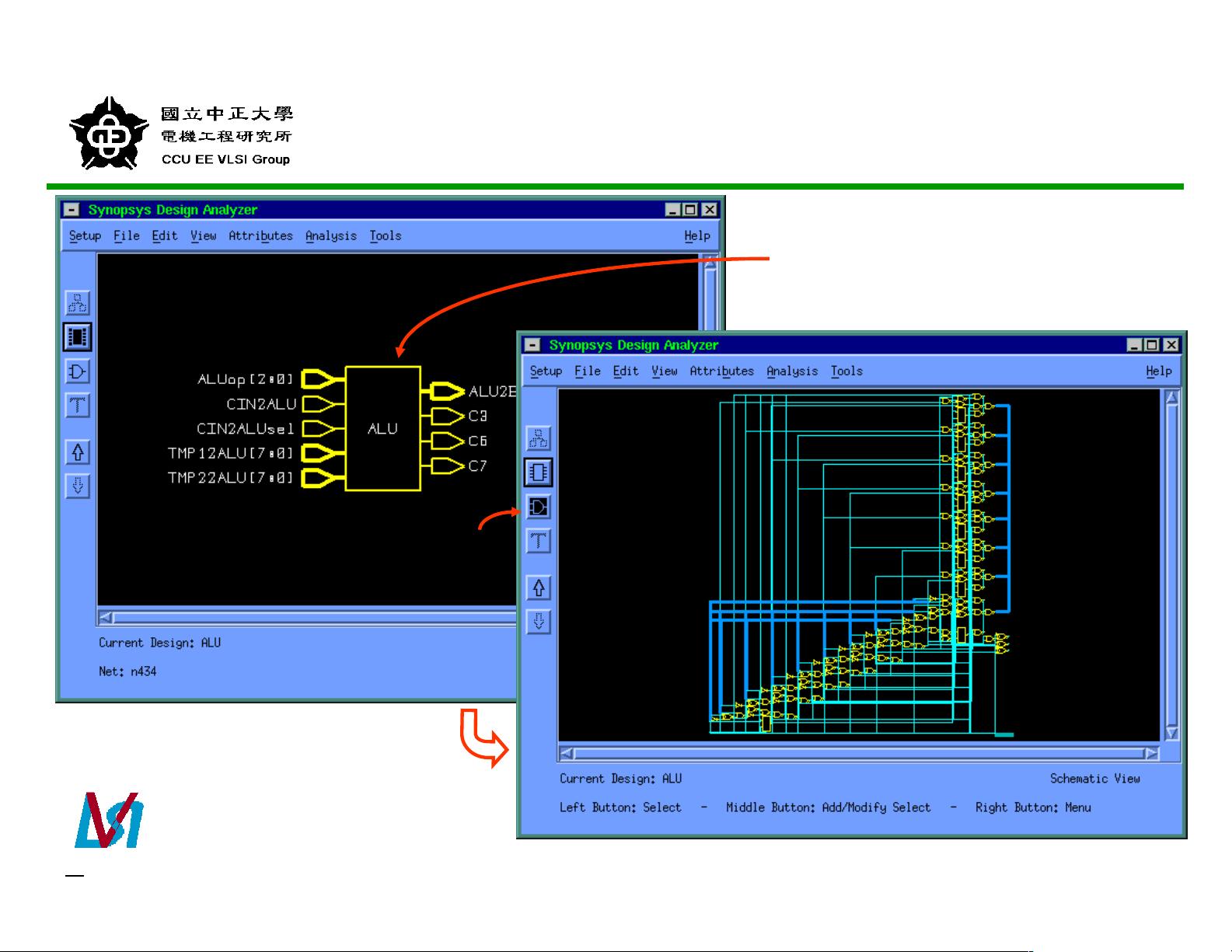

8. **用户界面和文档**:

文档还推荐使用在线文档资源和图形界面工具Iview进行交互,以便于理解和操作Synopsys Design Compiler的各项功能。

通过这篇教程,学习者将掌握如何设置和使用Design Compiler进行高效的设计分析和综合,包括如何处理各种类型的电路、设置约束条件以及管理库文件,从而确保最终设计的质量和效率。

2015-01-23 上传

2014-09-23 上传

2022-01-01 上传

2011-04-19 上传

点击了解资源详情

点击了解资源详情

why_900109

- 粉丝: 3

- 资源: 7

最新资源

- C++ Qt影院票务系统源码发布,代码稳定,高分毕业设计首选

- 纯CSS3实现逼真火焰手提灯动画效果

- Java编程基础课后练习答案解析

- typescript-atomizer: Atom 插件实现 TypeScript 语言与工具支持

- 51单片机项目源码分享:课程设计与毕设实践

- Qt画图程序实战:多文档与单文档示例解析

- 全屏H5圆圈缩放矩阵动画背景特效实现

- C#实现的手机触摸板服务端应用

- 数据结构与算法学习资源压缩包介绍

- stream-notifier: 简化Node.js流错误与成功通知方案

- 网页表格选择导出Excel的jQuery实例教程

- Prj19购物车系统项目压缩包解析

- 数据结构与算法学习实践指南

- Qt5实现A*寻路算法:结合C++和GUI

- terser-brunch:现代JavaScript文件压缩工具

- 掌握Power BI导出明细数据的操作指南