组合逻辑电路分析与设计:从原理到Verilog HDL

版权申诉

149 浏览量

更新于2024-07-03

收藏 13.47MB PPT 举报

"该资源是关于数字电子线路基础的第四章——组合逻辑电路的PPT,涵盖了组合逻辑电路的分析、设计、竞争和冒险现象、常用集成电路、可编程逻辑器件以及如何用Verilog HDL描述组合逻辑电路。"

在数字电子线路中,组合逻辑电路是一个重要的概念。它是由逻辑门(如与门、或门、非门等)组成的电路,其中输出信号的计算完全基于当前的输入信号,不依赖于电路的前一状态。这种特性使得组合逻辑电路在信息处理和数据计算中广泛应用。

组合逻辑电路的工作特点是:在任何时间点,电路的输出仅取决于同一时刻的输入,与电路之前的状态无关。它的结构特征包括没有反馈延迟路径,不含任何记忆元件,如触发器或寄存器,因此不具备存储信息的能力。

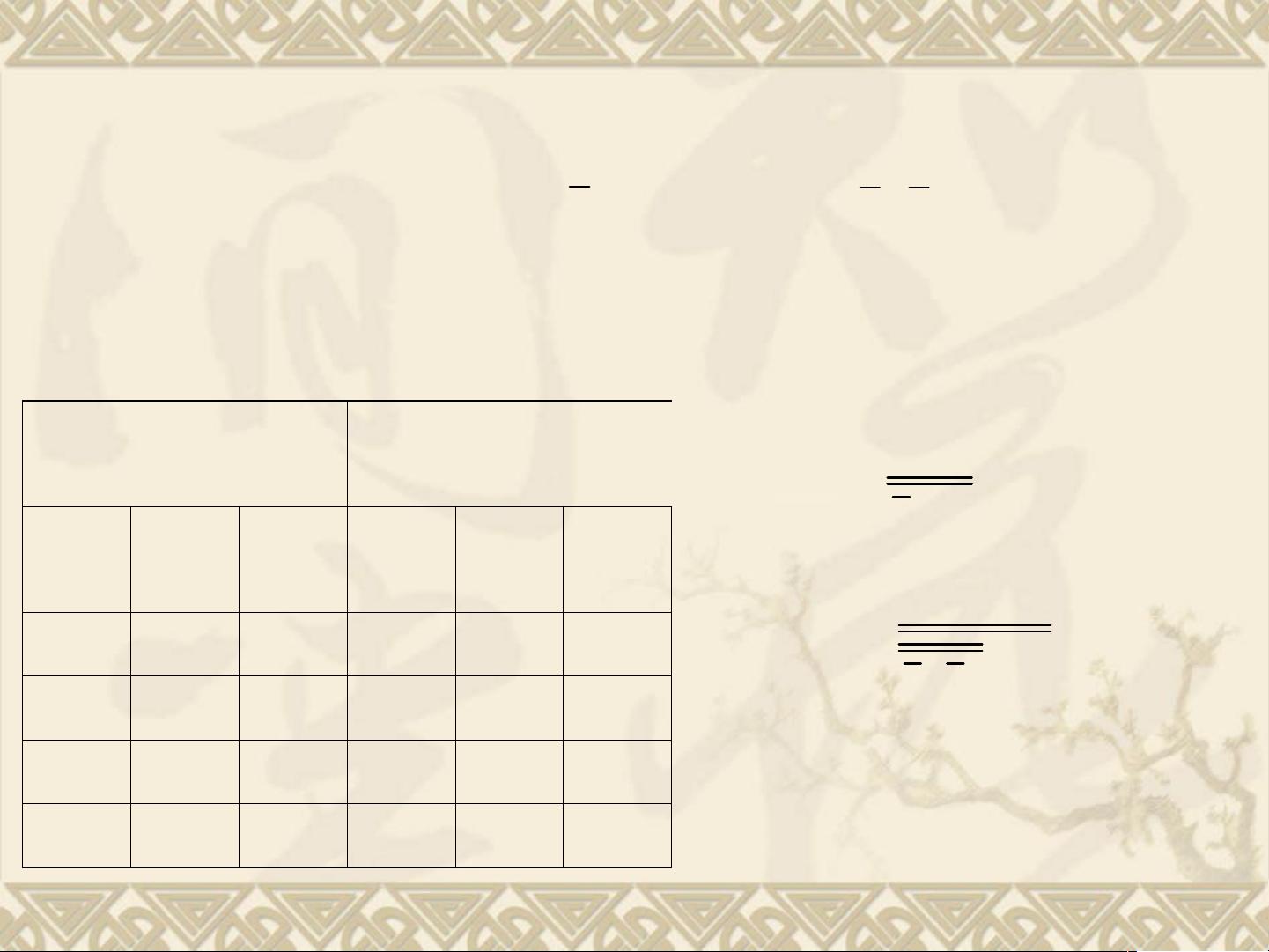

分析组合逻辑电路通常涉及以下步骤:

1. 从电路图中提取每个输出端的逻辑表达式,即找出每个输出Li与输入A1, A2,..., An之间的逻辑关系。

2. 对逻辑表达式进行化简,通常使用代数法或卡诺图法,以得到最简形式。

3. 列出真值表,这有助于理解电路在所有可能输入情况下的行为。

4. 基于真值表或简化后的逻辑表达式,确定电路的具体逻辑功能。

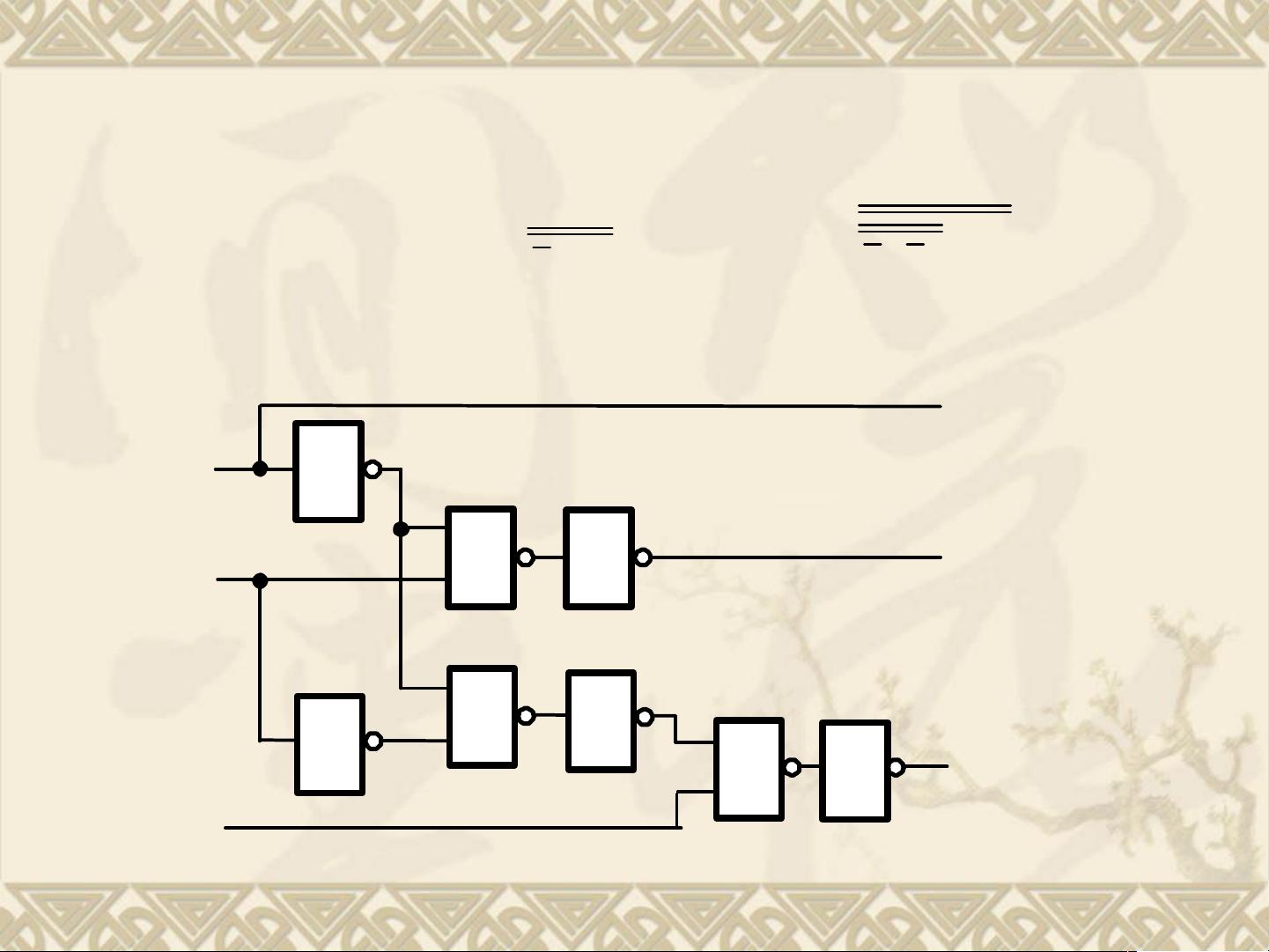

例如,在电路分析中,我们可能遇到如下的例子:

- 在一个电路中,如果输出L在输入变量A、B和C中有奇数个1时为1,其他情况为0,则该电路实现了奇校验功能。如果要改为偶校验,只需要将其中一个输入通过反相器连接到输出,这样当输入变量中1的个数为偶数时,输出才会为1。

- 另一个电路可能有多个输出,如Y和Z,它们分别与输入A、B、C和X有关。我们需要分析每个输出的逻辑表达式,然后列出真值表来确定它们各自的功能。

在实际应用中,组合逻辑电路的常用集成电路包括编码器、译码器、数据选择器、数值比较器和加法器等。编码器可以将几个输入位转换为一个编码输出,译码器则相反,它接受一个编码并产生多个输出。数据选择器允许从多个输入中选择一个特定的信号,数值比较器可以比较两个数字的大小,而加法器则执行二进制加法运算。

此外,随着可编程逻辑器件(如PLD,Programmable Logic Device)的发展,设计者能够根据需求自定义组合逻辑电路。使用Verilog HDL(硬件描述语言)可以更灵活地描述和设计这些电路,使得电路设计更加模块化和易于验证。

理解和掌握组合逻辑电路的分析和设计方法是计算机和电子工程领域的基础,对于实现复杂逻辑功能的电路系统至关重要。通过学习这些基础知识,工程师们能够创建出满足特定需求的高效电子设备。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-06-17 上传

2022-06-17 上传

2022-06-17 上传

2022-06-28 上传

2022-05-17 上传

点击了解资源详情

智慧安全方案

- 粉丝: 3837

- 资源: 59万+

最新资源

- ConcurrentStudy:Java并发编程和netty中学习加强相关代码

- 与一只巨大的鸡战斗至死:一场史诗般的最终幻想风格的战斗,对抗具有动态界面的 AI 控制的鸡:P-matlab开发

- Parstagram

- dsc字符串实验室在线ds-pt-090919

- UMLS-explorer

- txline,微带线计算工具

- OPPOR9S OPPOR9Splus原厂维修图纸电路图PCB位件图资料.zip

- stocks-chaser-frontend:库存跟踪应用

- 通过非线性导数进行边缘检测:这个简短的演示展示了一种有效的边缘检测算法。-matlab开发

- mariebeigelman.github.io

- AnoClient

- 开发基于JSP Servlet JavaBean的网上交易系统(JSP Servlet JavaBean Web Service

- Weather Forecast-crx插件

- go-jsonrpc-websocket.rar

- AM调制和解调研究:这个演示有助于研究和分析AM MOD和DEMOD。-matlab开发

- gocloud-secrets-awssecretsmanager