卡耐基梅隆大学Verilog硬件描述语言教程

需积分: 9 69 浏览量

更新于2024-08-02

收藏 292KB PDF 举报

"卡耐基梅隆大学的Verilog教程讲义是针对电子工程和计算机科学领域的一份教学资料,由Don Thomas教授编写。这份讲义并非一个完整的Verilog介绍,而是从不同层次的CMU课程中收集的多个主题。虽然不构成连贯的单一讲座,但可作为学习Verilog语言的辅助资源。对于发现的任何错误或问题,可以向作者thomas@ece.cmu.edu报告。此外,更正式的《The Verilog Hardware Description Language》第四版可在Kluwer Academic Publishers获取。

讲义的第二部分重点介绍了数字系统的模拟。模拟是验证设计功能的关键步骤。在软件编程中,我们通过输入测试来检查程序是否按预期工作,但即使经过详尽的测试,也无法保证程序完全没有错误。然而,模拟帮助我们确定设计在理论上能够执行预期任务。在硬件描述语言中,模拟用于测试你希望构建的系统模型。它允许你在实际制造之前检查逻辑设计的行为,以确保其在各种条件下的正确性。

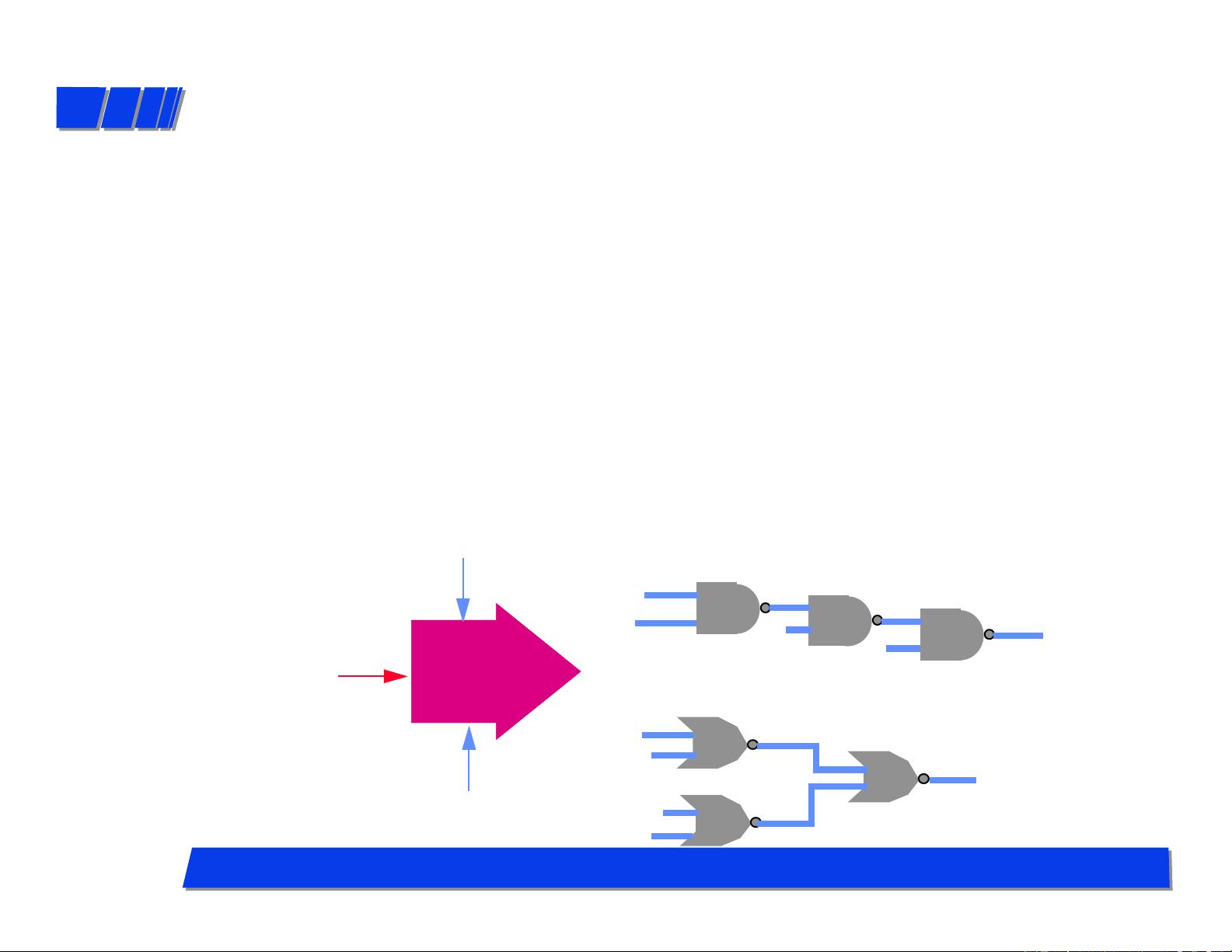

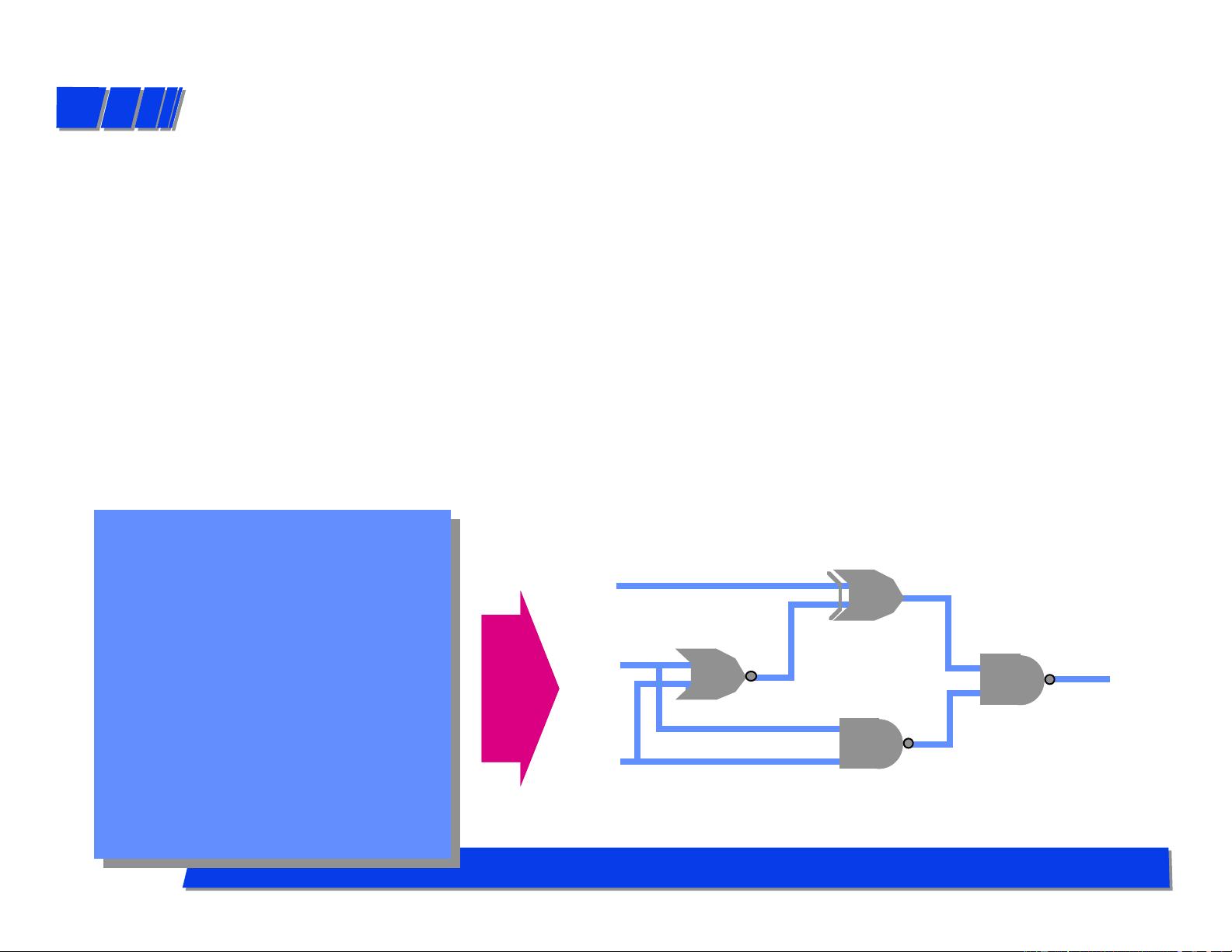

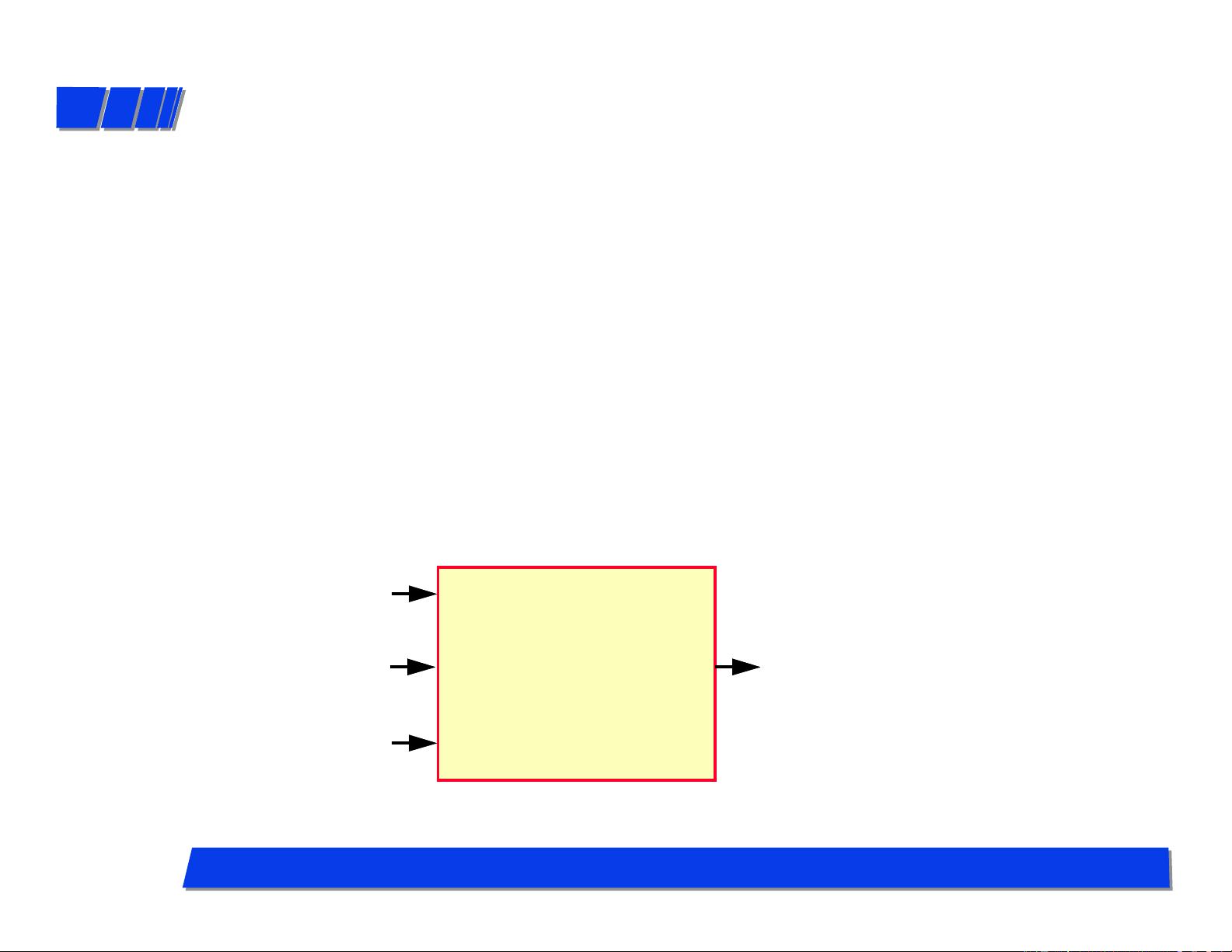

Verilog是一种广泛使用的硬件描述语言,它允许工程师以抽象的方式描述数字系统,从逻辑门级到行为级。在Verilog中,你可以定义模块,这些模块代表电路的各个部分,它们可以包含输入、输出、内部信号以及实现逻辑操作的代码。通过模拟,我们可以给这些模块提供输入信号,观察它们的输出,以此验证设计的正确性。

讲义可能会涵盖以下内容:

1. **基本语法和结构**:包括如何声明变量、常量,以及定义模块的基本结构。

2. **逻辑运算符**:AND、OR、NOT、NAND、NOR、XOR等,以及它们在Verilog中的表示方式。

3. **数据类型**:例如,wire(无源信号)、reg(有源信号)、integer、real等。

4. **赋值语句**:如阻塞赋值(`=`)和非阻塞赋值(`<=`)的区别。

5. **进程和时序控制**:如always块,用于描述时序逻辑。

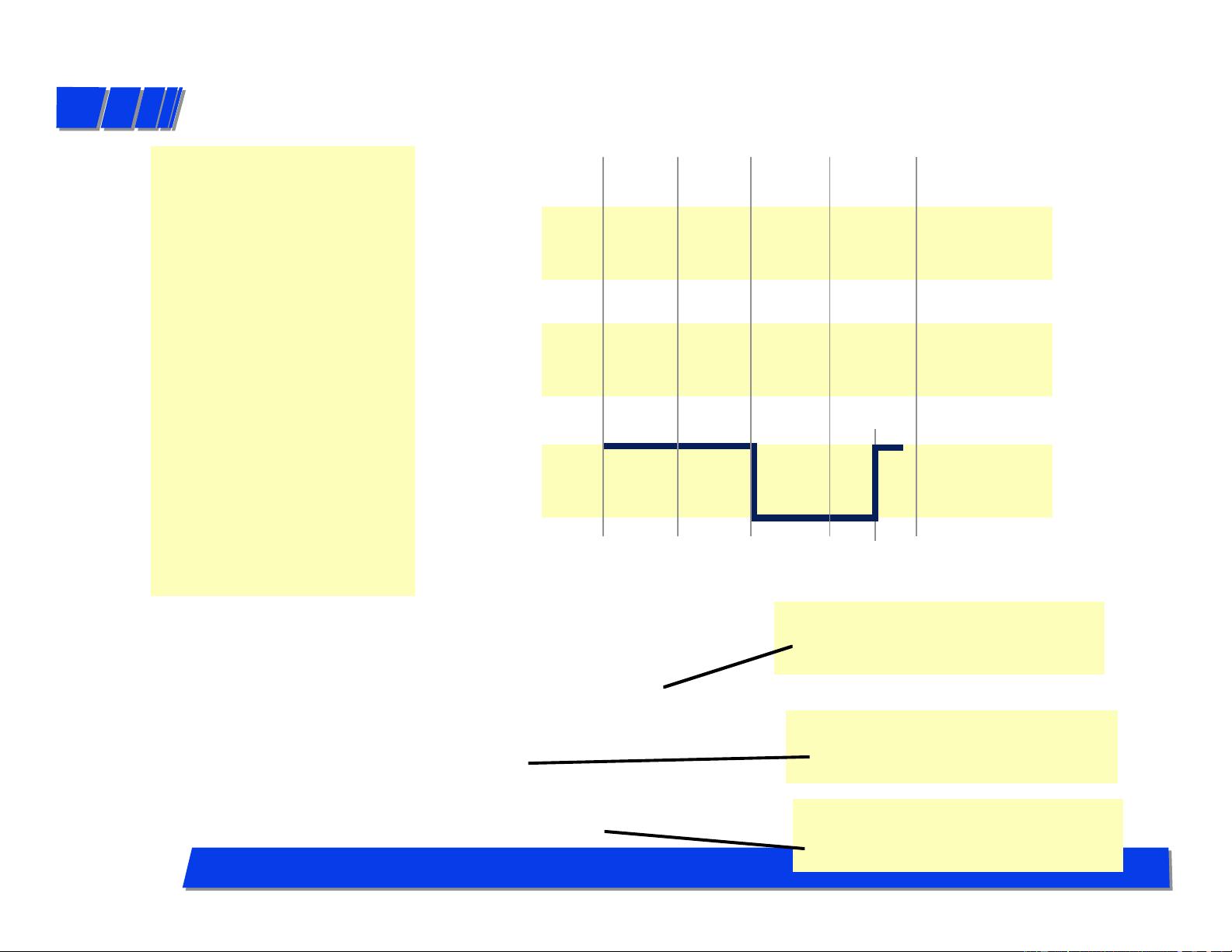

6. **结构化建模**:如组合逻辑和时序逻辑的建模方法。

7. **模块实例化**:如何在不同的模块之间连接电路。

8. **综合与仿真**:Verilog代码如何被综合成硬件电路,以及如何使用仿真工具进行测试。

通过深入学习这个教程,你将能够理解和编写Verilog代码,为数字系统的设计和验证打下坚实的基础。这个过程可能涉及阅读更多关于Verilog的章节,理解模块接口、参数化、任务和函数、条件语句、循环以及错误处理等方面的知识。同时,掌握模拟工具的使用,如ModelSim、VHDL仿真器等,也是不可或缺的一部分。最后,实践是检验理解的最好方式,通过实际项目来应用所学知识,将使你的Verilog技能更加熟练。"

138 浏览量

606 浏览量

2010-11-16 上传

411 浏览量

175 浏览量

548 浏览量

459 浏览量

222 浏览量

2024-12-27 上传

mazl02

- 粉丝: 0

最新资源

- LoadRunner中配置WebSphere监控指南

- XSLT中文参考手册:元素详解

- C++Builder6实战教程:14章精讲与实例分析

- Zend Framework 1.0 中文教程:入门数据库驱动应用

- C++编程入门:从零开始探索编程世界

- Ruby编程指南:从新手到专业者

- ARM ADS1.2开发详解:从创建工程到AXD调试

- 实时字数统计:输入限制250字

- 在Eclipse中集成Gridsphere框架:开发与调试指南

- SIP协议详解:从基础到应用

- 希腊字根解密:morph与英文单词的故事

- JPA入门指南:快速理解与实战示例

- 数据库分页技术详解与实现

- C语言笔试题目集锦

- 基于实例学习:实例存储与局部逼近的优势与挑战

- ArcGIS Engine应用开发教程