DDR2 PCB布局指南:解决布线与设计问题

"DDR2 布板指导手册 - 解析DDR2的PCB布局设计"

在嵌入式系统的设计中,内存的选择至关重要。随着技术的发展,SDRAM逐渐被DDR、DDR2和DDR3替代,其中DDR2因其性能优势成为当前的主流。尽管DDR、DDR2和DDR3在预存取技术上有差异,但它们的外部接口速度相似,例如,当clock频率为266MHz时,数据速率(BitRate)通常为533MHz,因为每个周期包含一个'0'和一个'1'。

DDR2的PCB布局设计是一项精细的工作,遵循一定的指导原则能确保系统的稳定性和性能。根据Micron和Freescale的设计指南,以下是一些关键点:

1. 地线处理:VSS通常代表数字地,VSSQ则用于信号地。如果没有特殊说明,两者可视为等效。同样,VDD提供器件核心电源,而VDDDQ供给DQ和I/O电源,这两者在一般情况下也可互换。

2. 信号分组:DDR2的信号分为多个组别,包括:

- 数字信号组:DQ、DQS和DM,每个字节由一组通道(Lane)组成,如DQ0~DQ7、DQS0和DM0。

- 地址信号组:ADDRESS

- 命令信号组:CAS#、RAS#和WE#

- 控制信号组:CS#和CKE

- 时钟信号组:CK和CK#

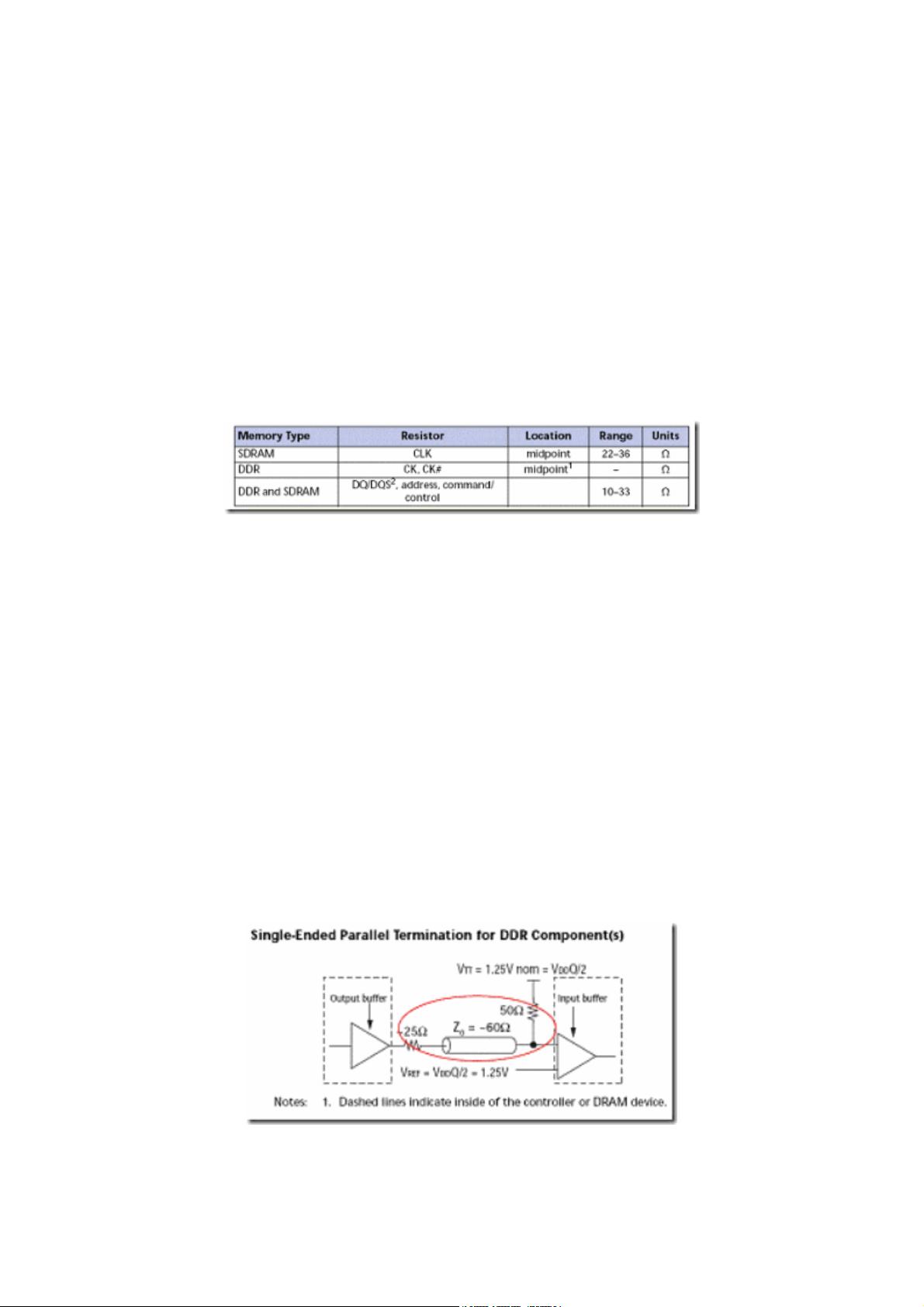

3. PCB叠层设计(Stackup):推荐采用6层PCB设计,具体层分布应考虑阻抗控制在50~60欧姆,以保证信号质量。电路板的厚度通常选为1.5英寸,这有助于实现理想的信号传输特性。

4. 阻抗控制:确保所有高速信号线的阻抗匹配是至关重要的,这可以通过精确计算和布局来实现,以减少信号反射和噪声。

5. 层间分配:将电源和地线层靠近信号层,可以有效地降低电磁干扰(EMI)并提高信号完整性。

6. 信号路由:DQ、DQS和DM应在相同层上并行路由,保持间距均匀,同时与时钟信号(CK和CK#)保持正确的相对位置,以最小化时钟到数据的延迟差。

7. 连接器和过孔设计:应尽量减少过孔的数量,特别是在高速信号路径中,过孔会引入额外的延迟和阻抗不连续性。连接器的选择也要注意其电气特性是否符合DDR2的需求。

8. 温度和电源管理:考虑器件的热设计,确保良好的散热,以及电源的稳定供应,防止电压波动影响内存性能。

9. DDR2设计检查清单:配合使用DDR2 design checklist,可以进一步确保设计中的各项指标符合规范。

DDR2的PCB布局设计需要综合考虑信号完整性和电源完整性,遵循厂商提供的设计指南,通过精细的布局和布线策略,可以有效地解决潜在的问题,确保系统运行的高效和可靠。

2011-12-21 上传

2021-12-16 上传

2013-10-28 上传

2012-03-23 上传

2024-01-26 上传

2021-07-10 上传

2009-10-06 上传

2024-03-06 上传

点击了解资源详情

sbsb888sbsb

- 粉丝: 0

- 资源: 4

最新资源

- Android圆角进度条控件的设计与应用

- mui框架实现带侧边栏的响应式布局

- Android仿知乎横线直线进度条实现教程

- SSM选课系统实现:Spring+SpringMVC+MyBatis源码剖析

- 使用JavaScript开发的流星待办事项应用

- Google Code Jam 2015竞赛回顾与Java编程实践

- Angular 2与NW.js集成:通过Webpack和Gulp构建环境详解

- OneDayTripPlanner:数字化城市旅游活动规划助手

- TinySTM 轻量级原子操作库的详细介绍与安装指南

- 模拟PHP序列化:JavaScript实现序列化与反序列化技术

- ***进销存系统全面功能介绍与开发指南

- 掌握Clojure命名空间的正确重新加载技巧

- 免费获取VMD模态分解Matlab源代码与案例数据

- BuglyEasyToUnity最新更新优化:简化Unity开发者接入流程

- Android学生俱乐部项目任务2解析与实践

- 掌握Elixir语言构建高效分布式网络爬虫