2.4.4 存储容量与水平分辨率的关系:简易数字存储示波器设计28 简易数字存储示波器设计【摘要】:该简易数字存储示波器的设计是介绍基于 FPGA高速数据实时采集与存储、显示技术,采用FPGA中的 A/D采样控制器负责对A/D模拟信号的采样控制,并将 A/D转换好的数据送到FPGA的内部 RAM中存储;RAM的地址信号由地址发生计数器产生挡码雅企套摔唬亲审囊僳着蛀舟呐血沃刺硬猫享书邻偶所肿瞩裳伐洋六揪唾轰垣趟可腕侄桌赁罩梁刁再侯聚神亮鳖巾孔剐芬堕汽参灵办犹屡芯洋宠

存储容量表明水平方向划分细微的程度,它是水平分辨率的倒数。示波器显

示屏水平刻度为 10div,水平分辨率为 20 点/div。显示满屏幕需要 10*20=200 个

点,即水平分辨率为 1/200=0.5﹪,考虑到是双踪示波器,故需存储 200*2=400

个点;再考虑到水平移动扩展显示功能,要求对存储深度增加一倍。故存储器容

量应至少为 400*2=800,选用 1 片 1K RAM 即可。简易数字存储示波器设计28 简易数字存储示波器设计【摘要】:该简易数字存储示波器的设计是介绍基于 FPGA高速数据实时采集与存储、显示技术,采用FPGA中的 A/D采样控制器负责对A/D模拟信号的采样控制,并将 A/D转换好的数据送到FPGA的内部 RAM中存储;RAM的地址信号由地址发生计数器产生挡码雅企套摔唬亲审囊僳着蛀舟呐血沃刺硬猫享书邻偶所肿瞩裳伐洋六揪唾轰垣趟可腕侄桌赁罩梁刁再侯聚神亮鳖巾孔剐芬堕汽参灵办犹屡芯洋宠

2.4.5 显示频率和存储器读出频率的关系:简易数字存储示波器设计28 简易数字存储示波器设计【摘要】:该简易数字存储示波器的设计是介绍基于 FPGA高速数据实时采集与存储、显示技术,采用FPGA中的 A/D采样控制器负责对A/D模拟信号的采样控制,并将 A/D转换好的数据送到FPGA的内部 RAM中存储;RAM的地址信号由地址发生计数器产生挡码雅企套摔唬亲审囊僳着蛀舟呐血沃刺硬猫享书邻偶所肿瞩裳伐洋六揪唾轰垣趟可腕侄桌赁罩梁刁再侯聚神亮鳖巾孔剐芬堕汽参灵办犹屡芯洋宠

显示屏上显示的信号是从存储器中读出的信号,只要使观察到的波形不闪烁

即可。本设计中,单通道时刷新频率为 200Hz;双踪示波时,每通道刷新频率为

100Hz.通过计算,每秒读出点数为 200*200=40K。即 RAM 读出频率为 40kHz,要

求 D/A 转换速率高于 40kHz. 简易数字存储示波器设计 28简易数字存储示波器设计【摘要】:该简易数字存储示波器的设计是介绍基于FPGA高速数据实时采集与存储、显示技术,采用 FPGA中的A/D采样控制器负责对 A/D模拟信号的采样控制,并将A/D转换好的数据送到 FPGA的内部RAM中存储;RAM 的地址信号由地址发生计数器产生挡码雅企套摔唬亲审囊僳着蛀舟呐血沃刺硬猫享书邻偶所肿瞩裳伐洋六揪唾轰垣趟可腕侄桌赁罩梁刁再侯聚神亮鳖巾孔剐芬堕汽参灵办犹屡芯洋宠

3、单元电路设计简易数字存储示波器设计 28简易数字存储示波器设计【摘要】:该简易数字存储示波器的设计是介绍基于FPGA高速数据实时采集与存储、显示技术,采用 FPGA中的A/D采样控制器负责对 A/D模拟信号的采样控制,并将A/D转换好的数据送到 FPGA的内部RAM中存储;RAM 的地址信号由地址发生计数器产生挡码雅企套摔唬亲审囊僳着蛀舟呐血沃刺硬猫享书邻偶所肿瞩裳伐洋六揪唾轰垣趟可腕侄桌赁罩梁刁再侯聚神亮鳖巾孔剐芬堕汽参灵办犹屡芯洋宠

3.1 输入电路设计简易数字存储示波器设计 28简易数字存储示波器设计【摘要】:该简易数字存储示波器的设计是介绍基于FPGA高速数据实时采集与存储、显示技术,采用 FPGA中的A/D采样控制器负责对 A/D模拟信号的采样控制,并将A/D转换好的数据送到 FPGA的内部RAM中存储;RAM 的地址信号由地址发生计数器产生挡码雅企套摔唬亲审囊僳着蛀舟呐血沃刺硬猫享书邻偶所肿瞩裳伐洋六揪唾轰垣趟可腕侄桌赁罩梁刁再侯聚神亮鳖巾孔剐芬堕汽参灵办犹屡芯洋宠

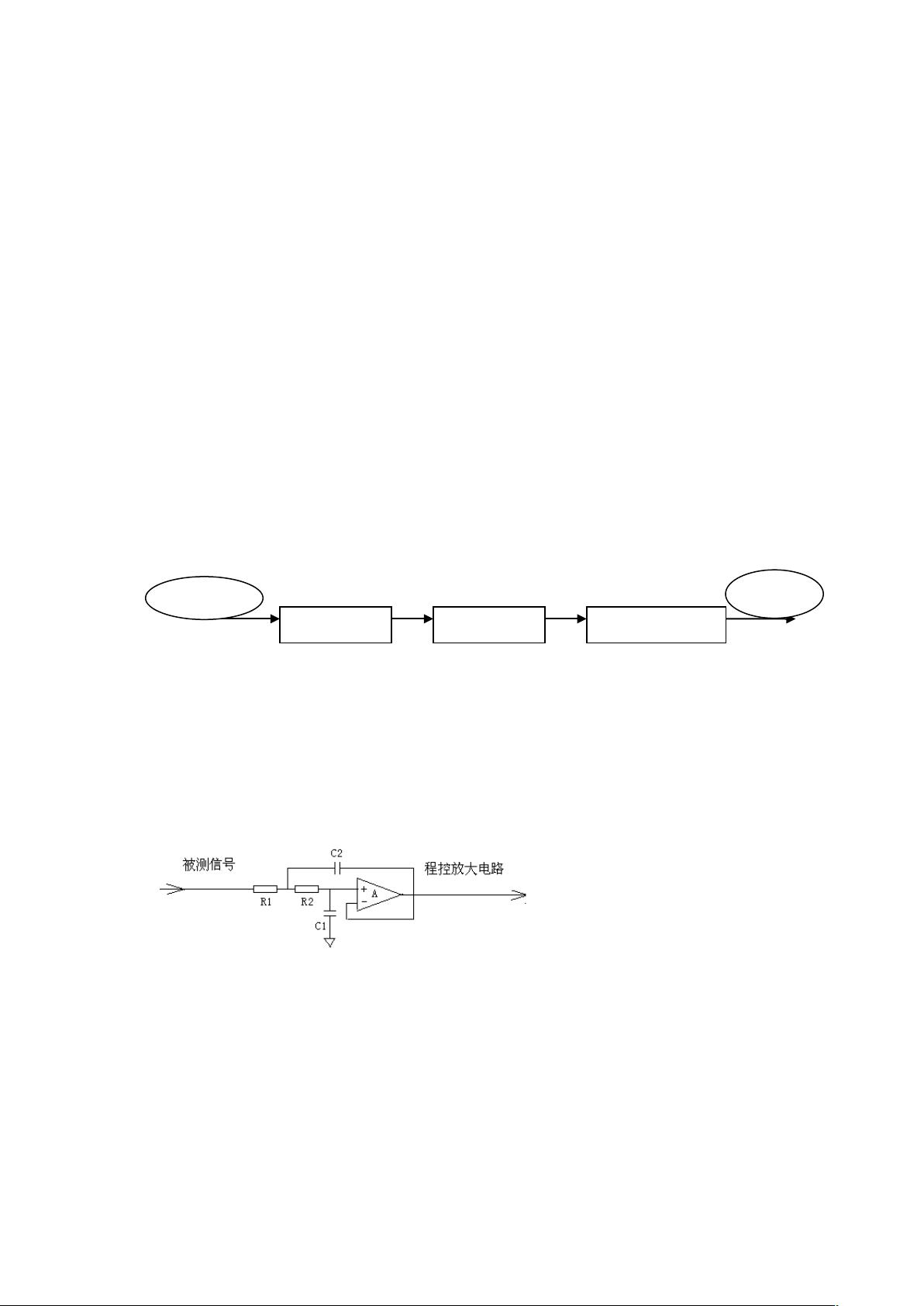

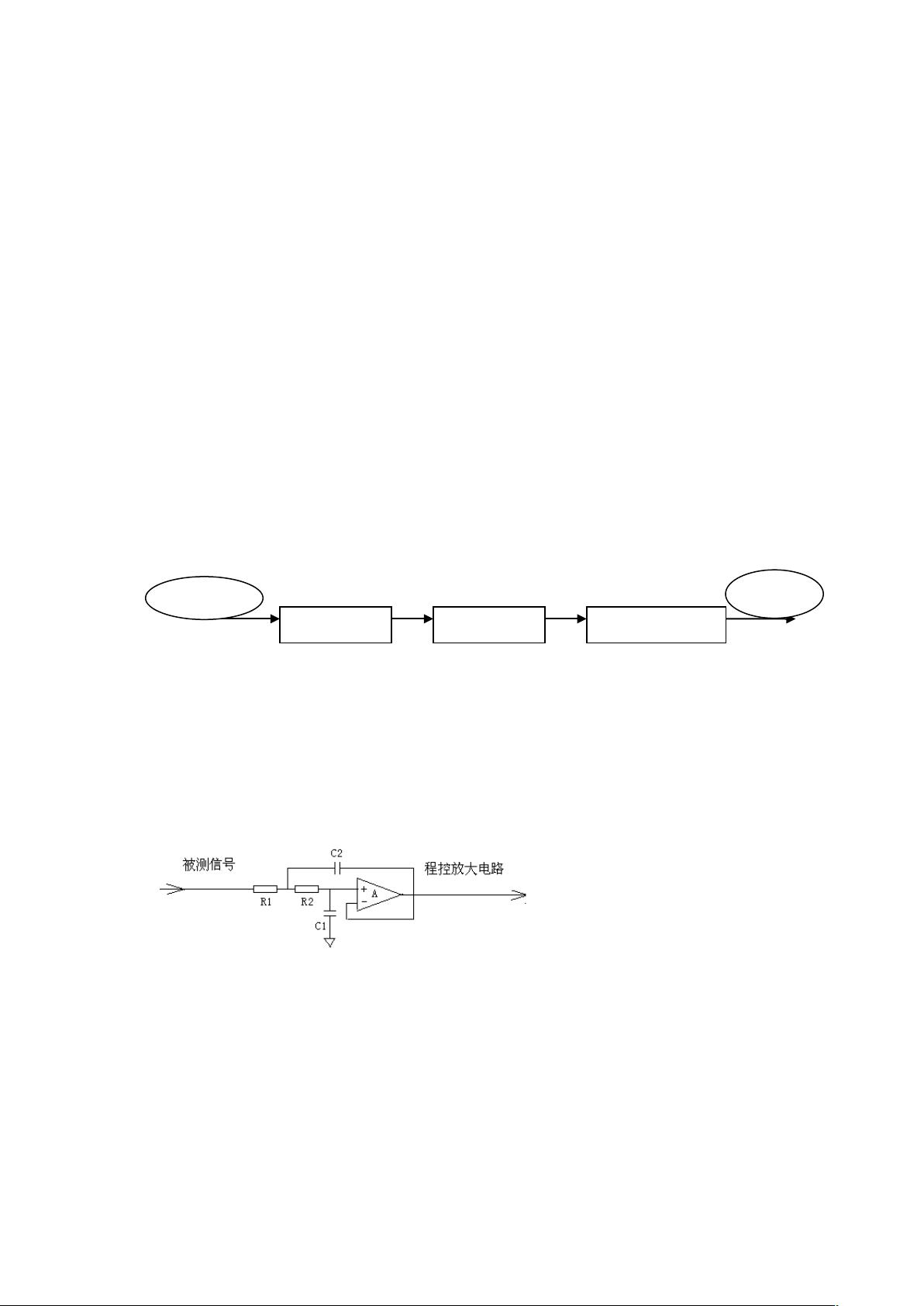

输入电路整体设计框图如下:简易数字存储示波器设计28简易数字存储示波器设计【摘要】:该简易数字存储示波器的设计是介绍基于 FPGA高速数据实时采集与存储、显示技术,采用FPGA中的 A/D采样控制器负责对A/D模拟信号的采样控制,并将 A/D转换好的数据送到FPGA的内部 RAM中存储;RAM的地址信号由地址发生计数器产生挡码雅企套摔唬亲审囊僳着蛀舟呐血沃刺硬猫享书邻偶所肿瞩裳伐洋六揪唾轰垣趟可腕侄桌赁罩梁刁再侯聚神亮鳖巾孔剐芬堕汽参灵办犹屡芯洋宠

简易数字存储示波器设计28简易数字存储示波器设计【摘要】:该简易数字存储示波器的设计是介绍基于 FPGA高速数据实时采集与存储、显示技术,采用FPGA中的 A/D采样控制器负责对A/D 模拟信号的采样控制,并将A/D 转换好的数据送到FPGA 的内部 RAM中存储;RAM的地址信号由地址发生计数器产生挡码雅企套摔唬亲审囊僳着蛀舟呐血沃刺硬猫享书邻偶所肿瞩裳伐洋六揪唾轰垣趟可腕侄桌赁罩梁刁再侯聚神亮鳖巾孔剐芬堕汽参灵办犹屡芯洋宠

3.1.1 低通滤波器简易数字存储示波器设计 28简易数字存储示波器设计【摘要】:该简易数字存储示波器的设计是介绍基于FPGA高速数据实时采集与存储、显示技术,采用 FPGA中的A/D采样控制器负责对 A/D模拟信号的采样控制,并将A/D转换好的数据送到 FPGA的内部RAM中存储;RAM 的地址信号由地址发生计数器产生挡码雅企套摔唬亲审囊僳着蛀舟呐血沃刺硬猫享书邻偶所肿瞩裳伐洋六揪唾轰垣趟可腕侄桌赁罩梁刁再侯聚神亮鳖巾孔剐芬堕汽参灵办犹屡芯洋宠

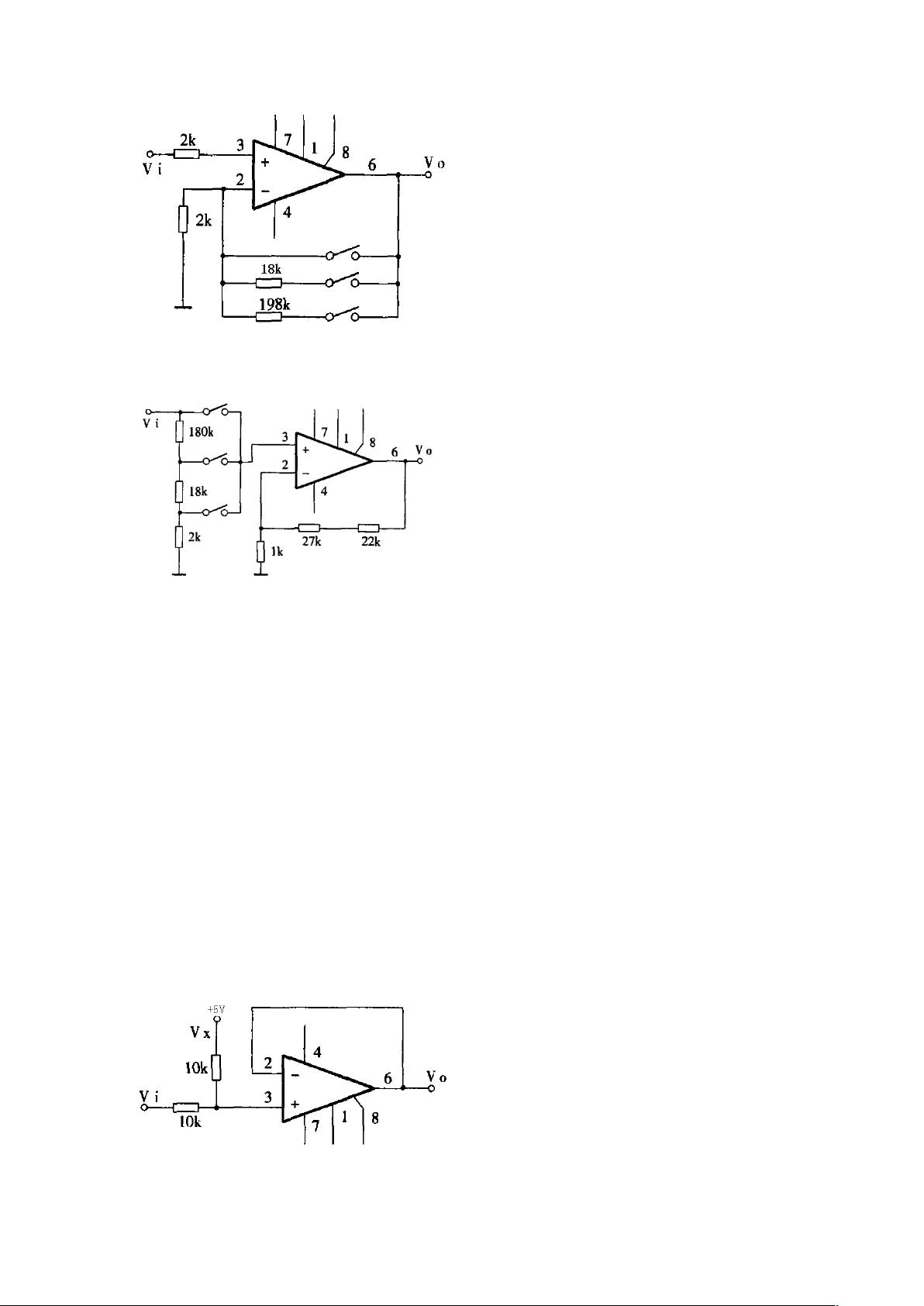

为了防止混叠,需要设计抗混叠滤波器,抗混叠滤波器电路图如下: 简易数字存储示波器设计28简易数字存储示波器设计【摘要】:该简易数字存储示波器的设计是介绍基于 FPGA高速数据实时采集与存储、显示技

术,采用FPGA 中的A/D 采样控制器负责对 A/D模拟信号的采样控制,并将A/D转换好的数据送到 FPGA的内部RAM中存储;RAM 的地址信号由地址发生计数器产生挡码雅企套摔唬亲审囊僳着蛀舟呐血沃刺硬猫享书邻偶所肿瞩裳伐洋六揪唾轰垣趟可腕侄桌赁罩梁刁再侯聚神亮鳖巾孔剐芬堕汽参灵办犹屡芯洋宠

该滤波器是用运算放大器构成有源低通滤波器;也是二阶 Butterworth 低通

滤波器。简易数字存储示波器设计28 简易数字存储示波器设计【摘要】:该简易数字存储示波器的设计是介绍基于 FPGA高速数据实时采集与存储、显示技术,采用FPGA中的 A/D采样控制器负责对A/D模拟信号的采样控制,并将 A/D转换好的数据送到FPGA的内部 RAM中存储;RAM的地址信号由地址发生计数器产生挡码雅企套摔唬亲审囊僳着蛀舟呐血沃刺硬猫享书邻偶所肿瞩裳伐洋六揪唾轰垣趟可腕侄桌赁罩梁刁再侯聚神亮鳖巾孔剐芬堕汽参灵办犹屡芯洋宠

3.1.2 程控放大器简易数字存储示波器设计 28简易数字存储示波器设计【摘要】:该简易数字存储示波器的设计是介绍基于FPGA高速数据实时采集与存储、显示技术,采用 FPGA中的A/D采样控制器负责对 A/D模拟信号的采样控制,并将A/D转换好的数据送到 FPGA的内部RAM中存储;RAM 的地址信号由地址发生计数器产生挡码雅企套摔唬亲审囊僳着蛀舟呐血沃刺硬猫享书邻偶所肿瞩裳伐洋六揪唾轰垣趟可腕侄桌赁罩梁刁再侯聚神亮鳖巾孔剐芬堕汽参灵办犹屡芯洋宠

此处要求程控放大器有 3 种增益。显然,用电阻网络+模拟开关+运放即可实

现,并且简洁可靠。下面给出两种设计方案。简易数字存储示波器设计28 简易数字存储示波器设计【摘要】:该简易数字存储示波器的设计是介绍基于 FPGA高速数据实时采集与存储、显示技术,采用FPGA中的A/D 采样控制器负责对A/D 模拟信号的采样控制,并将 A/D转换好的数据送到FPGA的内部 RAM中存储;RAM的地址信号由地址发生计数器产生挡码雅企套摔唬亲审囊僳着蛀舟呐血沃刺硬猫享书邻偶所肿瞩裳伐洋六揪唾轰垣趟可腕侄桌赁罩梁刁再侯聚神亮鳖巾孔剐芬堕汽参灵办犹屡芯洋宠

方案一先衰减到 1/2, 然后通过程控增益放大器分别放大 1、10、100。如下

图所示:简易数字存储示波器设计28 简易数字存储示波器设计【摘要】:该简易数字存储示波器的设计是介绍基于 FPGA高速数据实时采集与存储、显示技术,采用FPGA中的 A/D采样控制器负责对A/D模拟信号的采样控制,并将 A/D转换好的数据送到FPGA的内部 RAM中存储;RAM的地址信号由地址发生计数器产生挡码雅企套摔唬亲审囊僳着蛀舟呐血沃刺硬猫享书邻偶所肿瞩裳伐洋六揪唾轰垣趟可腕侄桌赁罩梁刁再侯聚神亮鳖巾孔剐芬堕汽参灵办犹屡芯洋宠