PDF: 09005aef826aa906/Source: 09005aef82a357c3 Micron Technology, Inc., reserves the right to change products or specifications without notice.

1Gb_DDR3_D2.fm - Rev. F 11/08 EN

17 ©2006 Micron Technology, Inc. All rights reserved.

1Gb: x4, x8, x16 DDR3 SDRAM

Ball Assignments and Descriptions

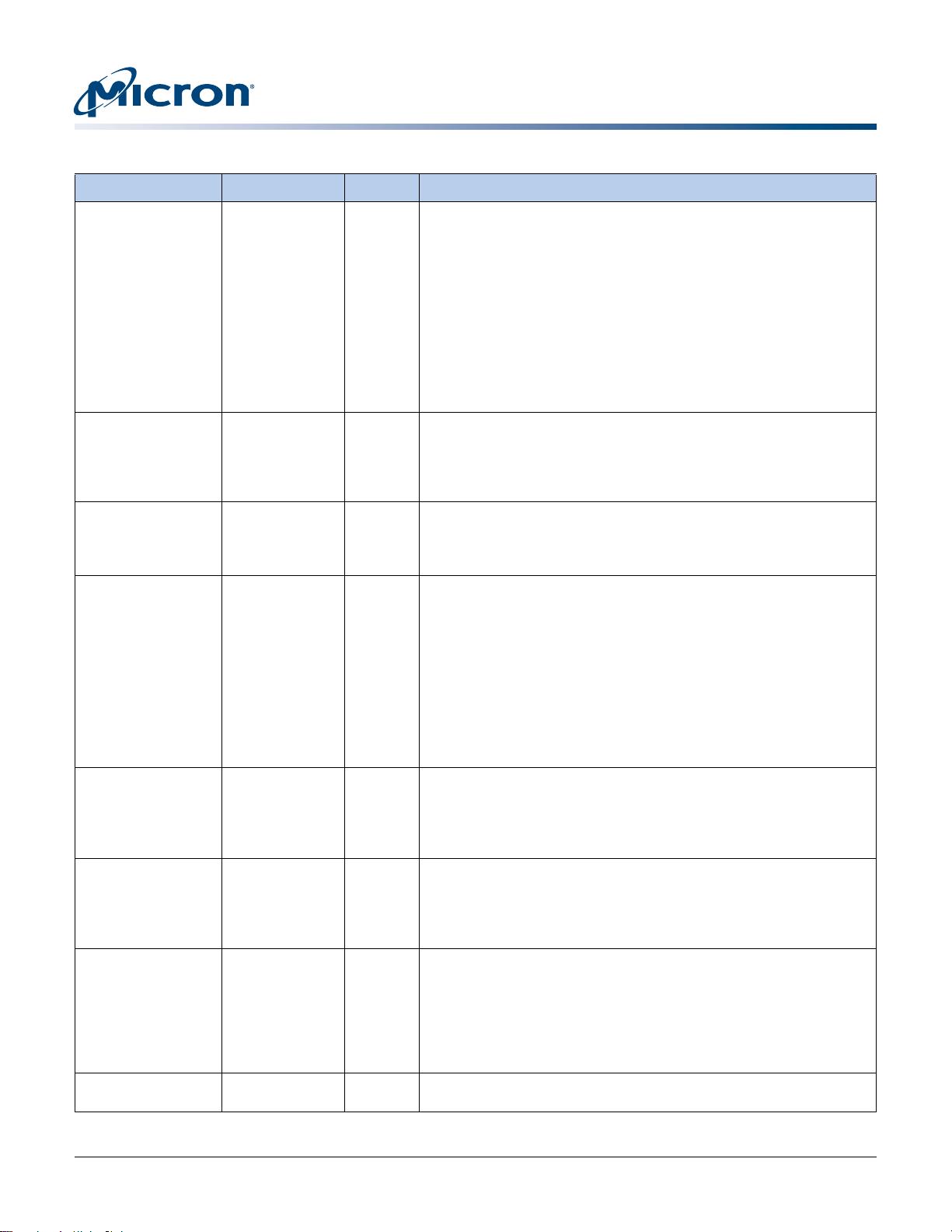

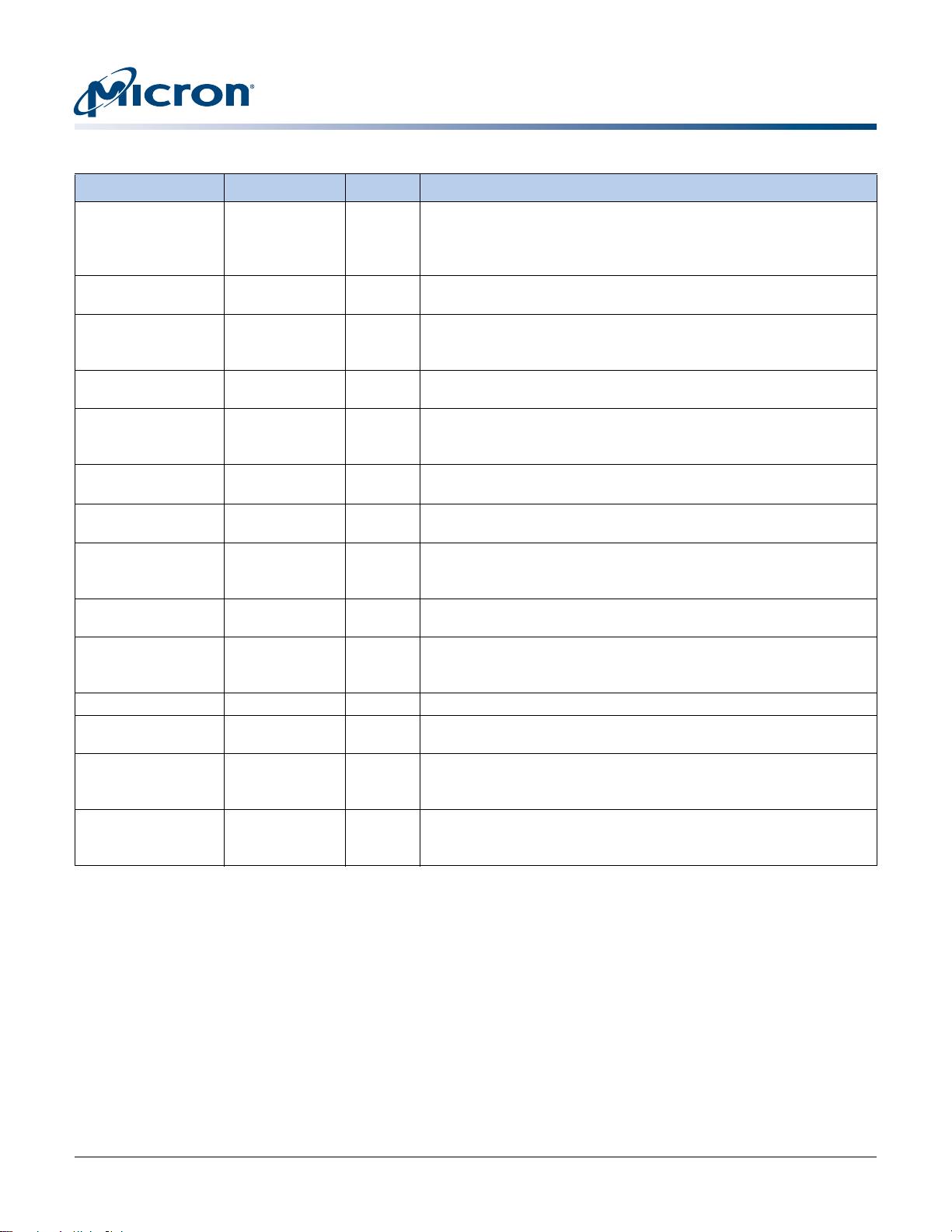

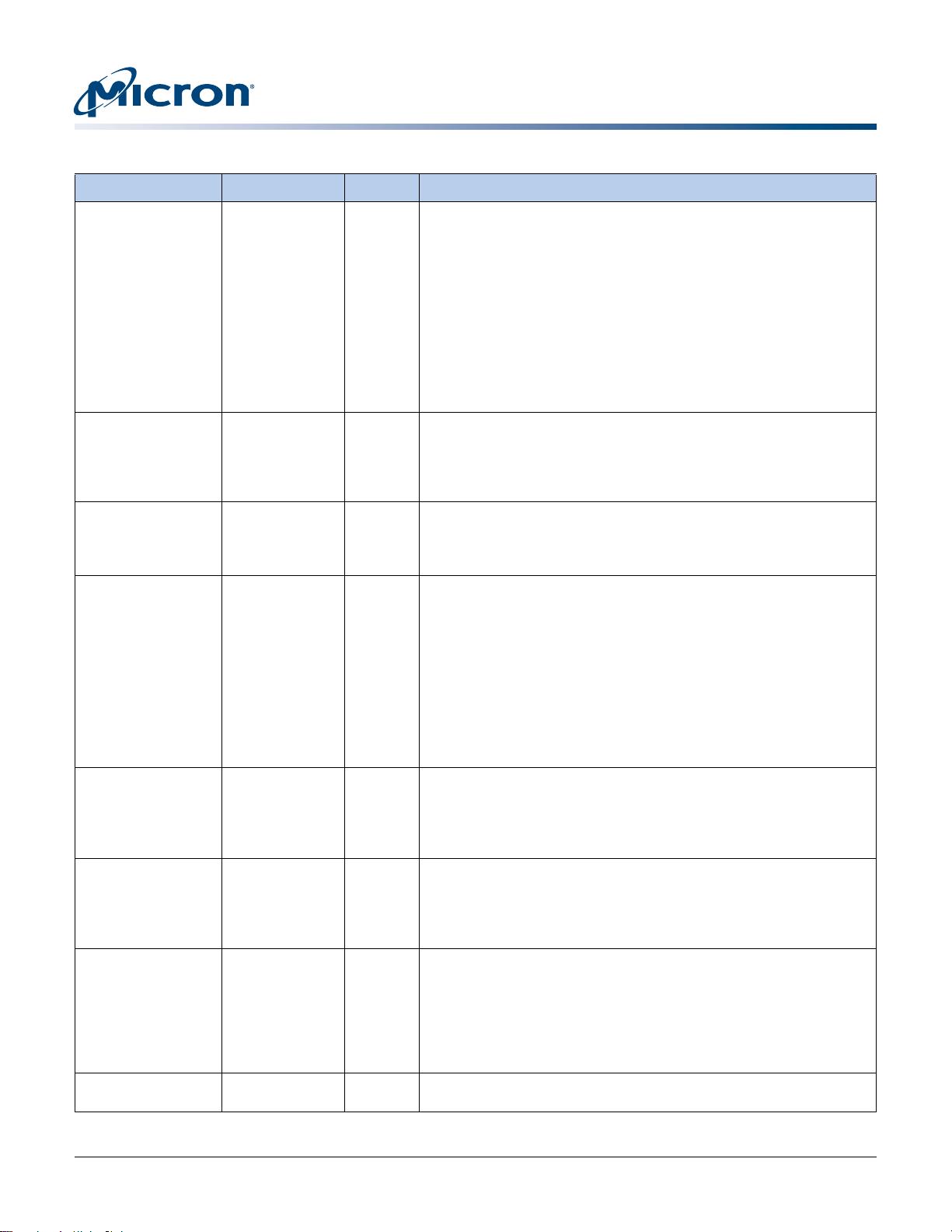

Table 3: 78-Ball FBGA – x4, x8 Ball Descriptions

Ball Assignments Symbol Type Description

K3, L7, L3, K2,

L8, L2, M8, M2,

N8, M3, H7, M7,

K7, N3

A0, A1, A2, A3,

A4, A5, A6, A7,

A8, A9, A10/AP,

A11, A12/BC#,

A13

Input Address inputs: Provide the row address for ACTIVATE commands,

and the column address and auto precharge bit (A10) for READ/

WRITE commands, to select one location out of the memory array in

the respective bank. A10 sampled during a PRECHARGE command

determines whether the PRECHARGE applies to one bank (A10 LOW,

bank selected by BA[2:0]) or all banks (A10 HIGH). The address inputs

also provide the op-code during a LOAD MODE command. Address

inputs are referenced to V

REFCA. A12/BC#: When enabled in the

mode register (MR), A12 is sampled during READ and WRITE

commands to determine whether burst chop (on-the-fly) will be

performed (HIGH = BL8 or no burst chop, LOW = BC4 burst chop).

See Table 62 on page 91.

J2, K8, J3 BA0, BA1, BA2 Input Bank address inputs: BA[2:0] define the bank to which an

ACTIVATE, READ, WRITE, or PRECHARGE command is being applied.

BA[2:0] define which mode register (MR0, MR1, MR2, or MR3) is

loaded during the LOAD MODE command. BA[2:0] are referenced to

V

REFCA.

F7, G7 CK, CK# Input Clock: CK and CK# are differential clock inputs. All control and

address input signals are sampled on the crossing of the positive

edge of CK and the negative edge of CK#. Output data strobe (DQS,

DQS#) is referenced to the crossings of CK and CK#.

G9 CKE Input Clock enable: CKE enables (registered HIGH) and disables

(registered LOW) internal circuitry and clocks on the DRAM. The

specific circuitry that is enabled/disabled is dependent upon the

DDR3 SDRAM configuration and operating mode. Taking CKE LOW

provides PRECHARGE power-down and SELF REFRESH operations (all

banks idle), or active power-down (row active in any bank). CKE is

synchronous for power-down entry and exit and for self refresh

entry. CKE is asynchronous for self refresh exit. Input buffers

(excluding CK, CK#, CKE, RESET#, and ODT) are disabled during

power-down. Input buffers (excluding CKE and RESET#) are disabled

during SELF REFRESH. CKE is referenced to V

REFCA.

H2 CS# Input Chip select: CS# enables (registered LOW) and disables (registered

HIGH) the command decoder. All commands are masked when CS# is

registered HIGH. CS# provides for external rank selection on systems

with multiple ranks. CS# is considered part of the command code.

CS# is referenced to V

REFCA.

B7 DM Input Input data mask: DM is an input mask signal for write data. Input

data is masked when DM is sampled HIGH along with the input data

during a write access. Although the DM ball is input-only, the DM

loading is designed to match that of the DQ and DQS balls. DM is

referenced to V

REFDQ. DM has an optional use as TDQS on the x8.

G1 ODT Input On-die termination: ODT enables (registered HIGH) and disables

(registered LOW) termination resistance internal to the DDR3

SDRAM. When enabled in normal operation, ODT is only applied to

each of the following balls: DQ[7:0], DQS, DQS#, and DM for the x8;

DQ[3:0], DQS, DQS#, and DM for the x4. The ODT input is ignored if

disabled via the LOAD MODE command. ODT is referenced to

V

REFCA.

F3, G3, H3 RAS#, CAS#, WE# Input Command inputs: RAS#, CAS#, and WE# (along with CS#) define

the command being entered and are referenced to V

REFCA.

http://www.BDTIC.com/Micron