设计与实现ONFI2.1同步模式NAND Flash控制器

"本文主要介绍了支持ONFI2.1同步模式的NAND Flash控制器的设计,旨在解决高速数据传输和信号对齐等问题,提供高效的非易失性存储解决方案。" 0 引言 随着数字信息时代的快速发展,大容量数据存储的需求日益增长。NAND Flash作为一种非易失性存储技术,因其高密度、低成本的特性,被广泛应用于移动设备、固态硬盘和其他存储系统中。然而,NAND Flash的访问机制与传统的NOR Flash不同,它不支持随机字节访问,读写操作需按页面进行,且有特定的擦除规则,因此需要专门的控制器来协调这些操作。 1 ONFI标准 ONFI标准的诞生是为了统一并简化NAND Flash的接口,减少制造商间的兼容性问题。由Intel发起,ONFI规范通过定义统一的引脚布局和协议,促进了不同供应商间的互操作性。早期的ONFI1.0标准虽然实现了接口标准化,但传输速度限制在34MB/s,难以满足高速应用需求。因此,ONFI2.1标准应运而生,将接口速度提升至200MB/s,采用了DDR技术来实现双倍数据传输速率,显著提高了性能。 2 NAND Flash控制器设计 本文设计的控制器特别针对ONFI2.1标准,支持源同步高速模式。设计的关键部分包括状态机的设计,用于管理NAND Flash的各种操作,如读、写、擦除等。此外,接口设计也是关键,需要处理与NAND Flash设备之间的通信协议。 在源同步模式下,信号对齐是设计中的一个重要挑战,因为高速数据传输可能导致信号延迟和同步问题。文章提出了一个解决信号对齐问题的方法,确保控制器能准确接收和发送数据。 另一个挑战是数据跨时钟域传输。由于控制器和NAND Flash可能工作在不同的时钟域,数据在两个域之间传输时可能会出现时序问题。为解决这个问题,文章给出了相应的同步策略,保证数据的正确无损传输。 3 结果与验证 经过仿真和综合,该设计被证实完全符合ONFI2.1标准,能在200MB/s的速率下高效地读写NAND Flash,提升了存储系统的整体性能。这一设计具有很高的实用价值,可以广泛应用于需要高速数据存取的系统中。 设计一款支持ONFI同步模式的NAND Flash控制器对于实现高速、高效率的数据存储至关重要。本文提出的解决方案不仅解决了接口标准化问题,还优化了信号对齐和跨时钟域传输,为NAND Flash的应用提供了更强大的支撑。

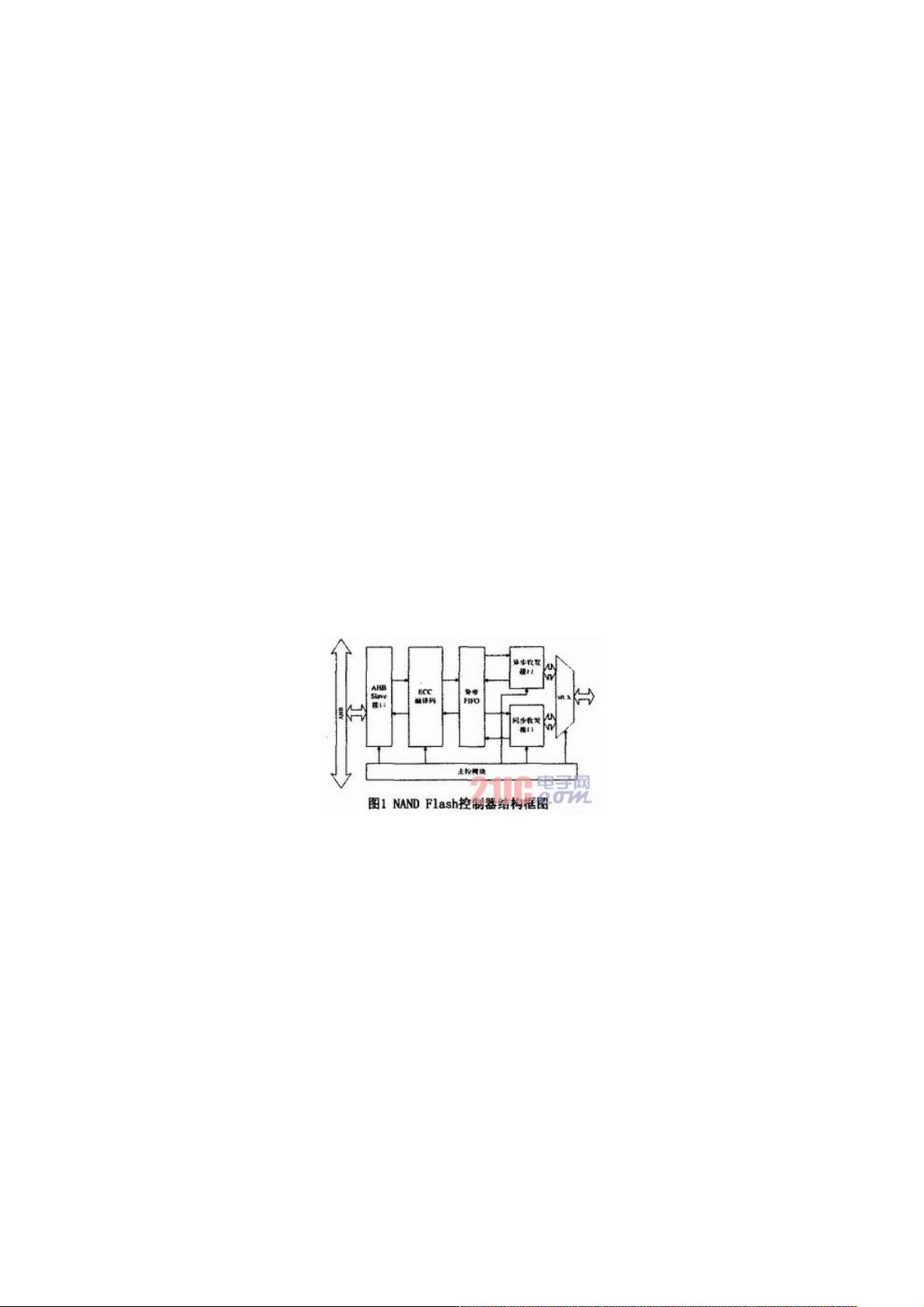

下载后可阅读完整内容,剩余3页未读,立即下载

- 粉丝: 6

- 资源: 913

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- C++标准程序库:权威指南

- Java解惑:奇数判断误区与改进方法

- C++编程必读:20种设计模式详解与实战

- LM3S8962微控制器数据手册

- 51单片机C语言实战教程:从入门到精通

- Spring3.0权威指南:JavaEE6实战

- Win32多线程程序设计详解

- Lucene2.9.1开发全攻略:从环境配置到索引创建

- 内存虚拟硬盘技术:提升电脑速度的秘密武器

- Java操作数据库:保存与显示图片到数据库及页面

- ISO14001:2004环境管理体系要求详解

- ShopExV4.8二次开发详解

- 企业形象与产品推广一站式网站建设技术方案揭秘

- Shopex二次开发:触发器与控制器重定向技术详解

- FPGA开发实战指南:创新设计与进阶技巧

- ShopExV4.8二次开发入门:解决升级问题与功能扩展

信息提交成功

信息提交成功