基于FPGA/SoC的AVS 3D实时解码器设计与实现

PDF格式 | 376KB |

更新于2024-09-03

| 90 浏览量 | 举报

AVS 3D实时解码器在FPGA/SoC平台上的设计与实现是一项重要的技术突破,它结合了AVS音频视频编码标准(Audio Video Coding Standard)和三维立体视频技术。AVS标准是中国自主研发的第二代编码标准,而针对3D视频,工作组提出了双目立体视频编解码方案,这是一种创新的编码方式,旨在提供更高质量的立体视觉体验。

设计的核心在于利用FPGA(Field-Programmable Gate Array)硬件加速模块来加速双目立体ES流(Enhanced Side-by-Side,一种3D视频流格式)的语法元素解析。FPGA以其高度可编程性和高效计算能力,能够实现高效的并行处理,提升解码速度。在这个项目中,选择的SoC开发板是Xilinx ZYNQ 7020,这是一款嵌入式系统芯片,拥有两个M9处理核心,具有高度集成、强大控制能力和通用软件支持的特点。

设计过程分为两个主要部分:首先,一个主PS(Processing System)负责与外部接口通信,管理解码图像显示,并协调整个解码过程;其次,由一个从PS以及多个硬件加速模块(包括ES流语法解析、算术码解码和变长码解码等)共同执行AVS双目拼接解码算法。这种协同工作模式使得在FPGA/SoC平台上实现了AVS 3D实时解码器,能够实现实时且高效的3D视频解码。

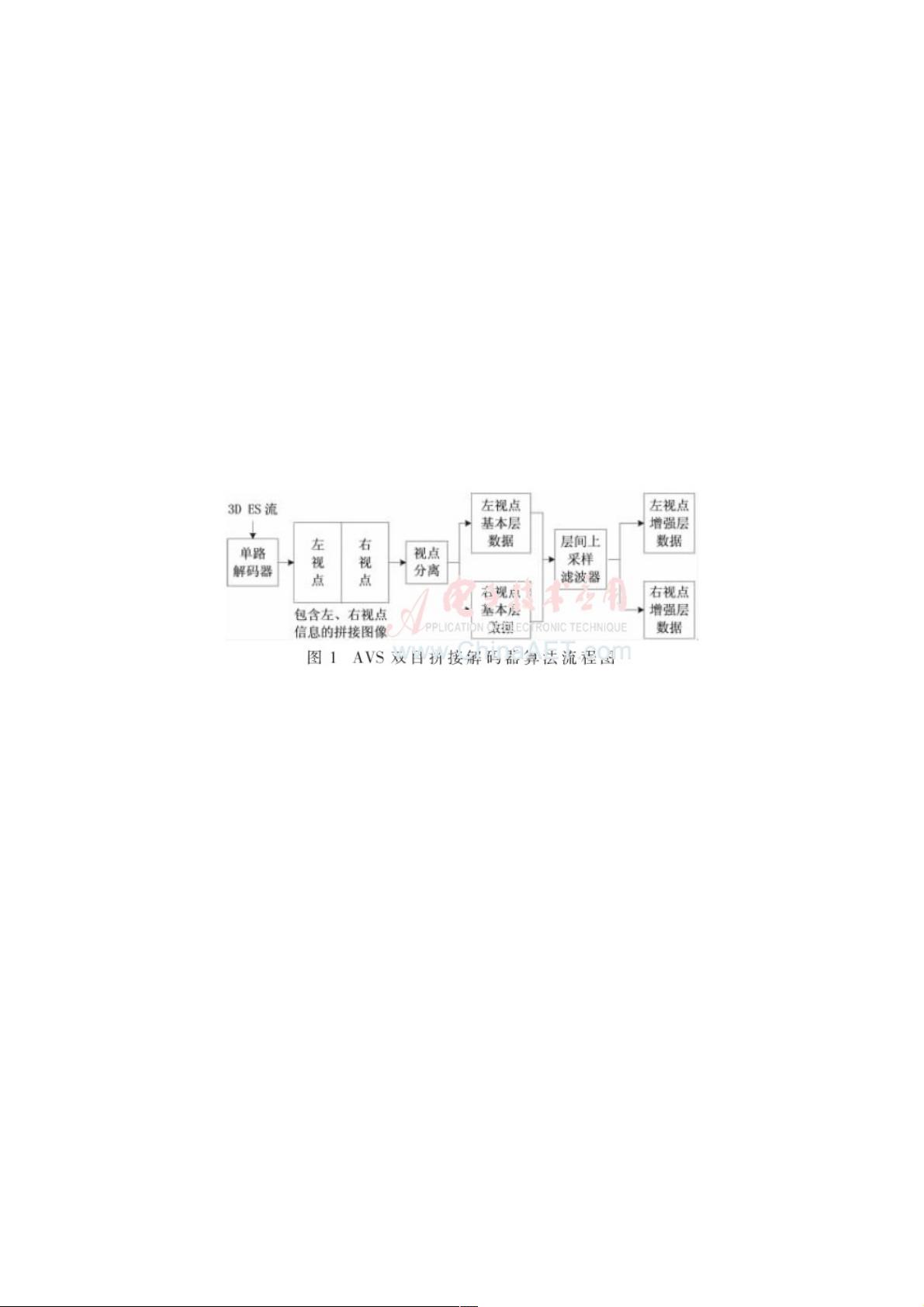

算法流程方面,AVS 3D解码器采用了双目拼接算法,从3DES流中同时提取左、右视点的信息。解码过程以帧为单位进行,类似于单路AVS解码器,但涉及到立体视觉处理,如视点分离后对基本层图像进行水平维度的上采样插值,以提升增强层图像的分辨率。

为了进一步优化性能,设计了一个CABAC(Context Adaptive Binary Arithmetic Coding)和CAVLC(Context Adaptive Variable Length Coding)的硬件加速模块,用于快速解析编码后的语法元素,减少了CPU的负载,从而提升了整个系统的实时性。

这项研究不仅推动了AVS标准在3D视频领域的应用,还展示了如何有效地利用FPGA/SoC平台进行高性能实时解码器的设计与实现,为未来基于AVS的三维视频处理提供了新的解决方案和技术参考。

相关推荐

点击了解资源详情

346 浏览量

121 浏览量

2021-07-13 上传

2021-07-13 上传

114 浏览量

128 浏览量

2021-09-25 上传

135 浏览量

weixin_38732425

- 粉丝: 6

最新资源

- CF平台DevOps研讨:掌握微服务部署与蓝绿部署策略

- haproxy-1.9.12:Linux下的高效负载均衡解决方案

- 奇数阶魔方阵的C++实现源代码

- 学习CSS按钮与网站后台设计的炫酷应用

- 精选VC++编程源码:大学编程学习参考

- 基于空域互相关技术的VC图像配准算法研究

- IIS7.0英文手册下载指南与jb51资源整理

- C#开发简洁倒计时demo及其多鼠标功能介绍

- 拉格朗日系数在Matlab开发中的应用

- php100新手入门新闻系统源码教程

- Spring boot与Mybatis通用mapper集成示例教程

- UCWeb for Windows CE手机的适用指南

- 微信风格的图片裁剪工具,操作流畅体验升级

- 实现带行号功能的RichEdit控件技巧分享

- C#2005深入数据库编程教程与实例代码解析

- 手机号与IP信息查询工具:正反向检索功能