5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

FSBSEL1

FSBSEL0

FSBSEL2

CLK_VTT_PWRGDJ

CK_48M_SIO

CK_48M_ICH

CK_33M_ICH

CK_33M_PCI1

CK_33M_PCI2

CK_33M_LAN

CK_33M_FWH

CK_14M_ICH

TURBOJ

TURBOJ

CK_33M_SIO

48M_SIO

3D3V_CLK_A_SRC_CPU

200M_P_CPU

SATA_100M_P_ICH

3D3V_CLK_A_SRC_CPU

33M_ICH

3D3V_CLK_A_SRC_CPU

3D3V_CLK_PCI_REF_USB

48M_SIO

ICS_FSBSEL1

200M_N_GMCH

PE_100M_P_ICH

PE_100M_P_16PORT

96M_DOT_P

48M_ICH 200M_P_GMCH

SATA_100M_N_ICH

200M_N_CPU

PE_100M_N_GMCH

33M_SIO

CLK_VTT_PWRGDJ

33M_PCI1

3D3V_CLK_PCI_REF_USB

PE_100M_N_ICH

33M_FWH

PE_100M_N_16PORT

96M_DOT_N

CLK_IREF

33M_LAN

PE_100M_P_GMCH

ICS_FSBSEL0

3D3V_CLK_A_SRC_CPU

3D3V_CLK_PCI_REF_USB

3D3V_CLK_A_SRC_CPU

3D3V_CLK_A_SRC_CPU

ICS_FSBSEL2

14M_ICH

ICS_FSBSEL0

ICS_FSBSEL1

ICS_FSBSEL2

3D3V_CLK_PCI_REF_USB

3D3V_CLK_PCI_REF_USB

BSEL1ICS_FSBSEL1

FSBSEL0

33M_PCI2

3D3V_CLK_A_SRC_CPU

3D3V_SYS

FSB_VTT

3D3V_SYS

3D3V_SYS

VCCP

3D3V_SYS

3D3V_SYS

5V_SYS

3D3V_CLK_PCI_REF_USB

FSB_VTT

3D3V_SYS

3D3V_SYS

CK_33M_SIO34

CK_48M_ICH22

FSBSEL0 12,14

FSBSEL1 12,14

FSBSEL2 12,14

CK_48M_SIO34

CK_SATA_100M_N_ICH23

CK_96M_P_GMCH14

CK_96M_N_GMCH14

CK_200M_N_CPU 12

CK_200M_P_CPU 12

CK_200M_N_GMCH 14

TURBOJ34

CK_33M_PCI125

SMB_CLK_MAIN 17,18,35

CK_200M_P_GMCH 14

CK_SATA_100M_P_ICH23

SMB_DATA_MAIN 17,18,35

ICH_SYS_RSTJ 12,22,37

CK_14M_ICH 22

FSBSEL2 12,14

FSBSEL1 12,14

FSBSEL0 12,14

CK_33M_LAN28

CK_PE_100M_N_GMCH 14

CK_PE_100M_P_GMCH 14

CK_PE_100M_N_16PORT20

CK_PE_100M_P_16PORT20

CK_PE_100M_P_ICH 22

CK_PE_100M_N_ICH 22

CK_33M_FWH 31

BSEL1 14

CK_PE_100M_N_1PORT26

CK_PE_100M_P_1PORT26

CK_33M_ICH24

CK_33M_PCI2 25

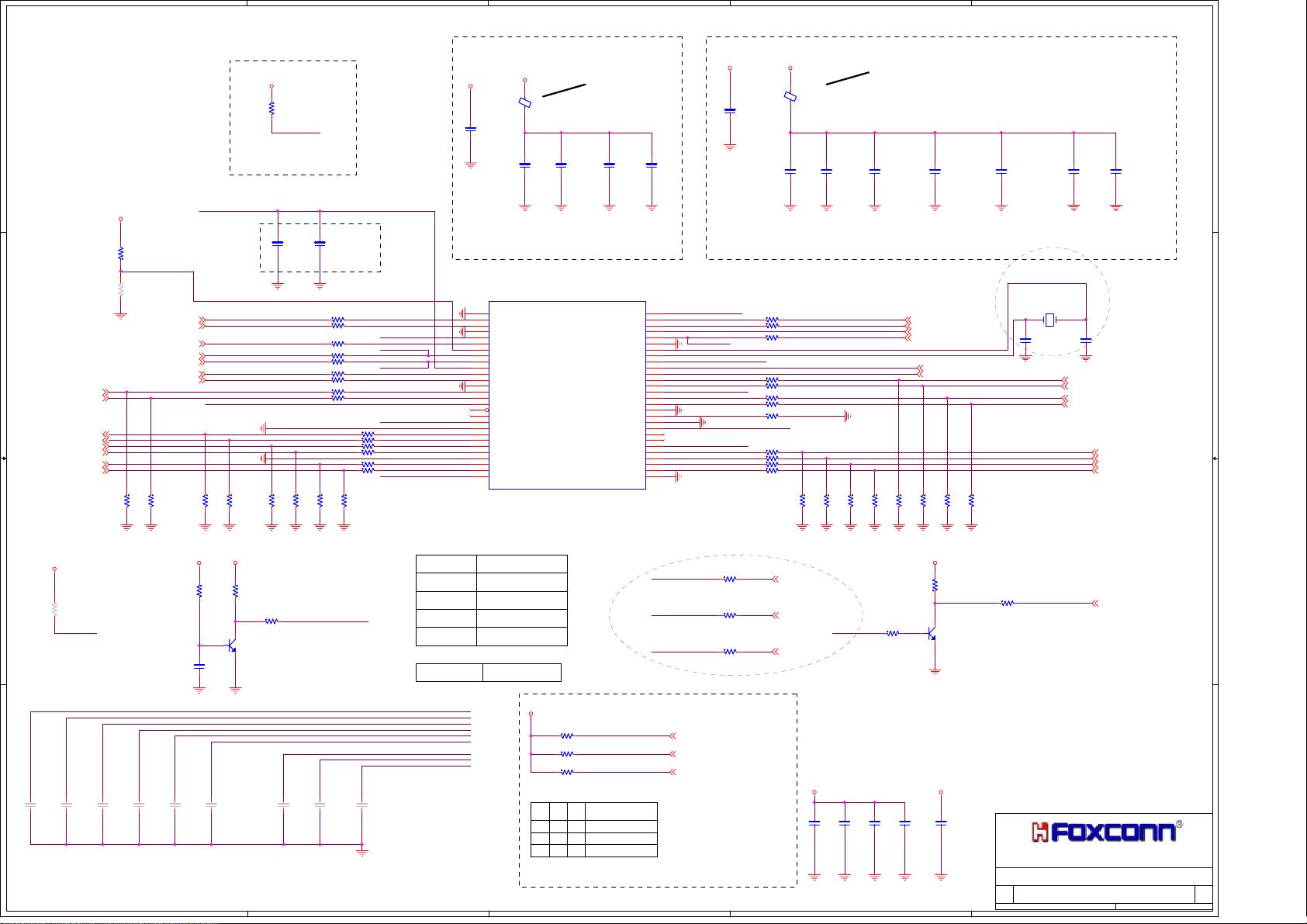

Title

Size Document Number Rev

Date: Sheet

of

FOXCONN PCEG

945M03

AC

740Thursday, July 13, 2006

CK410 ClockGen

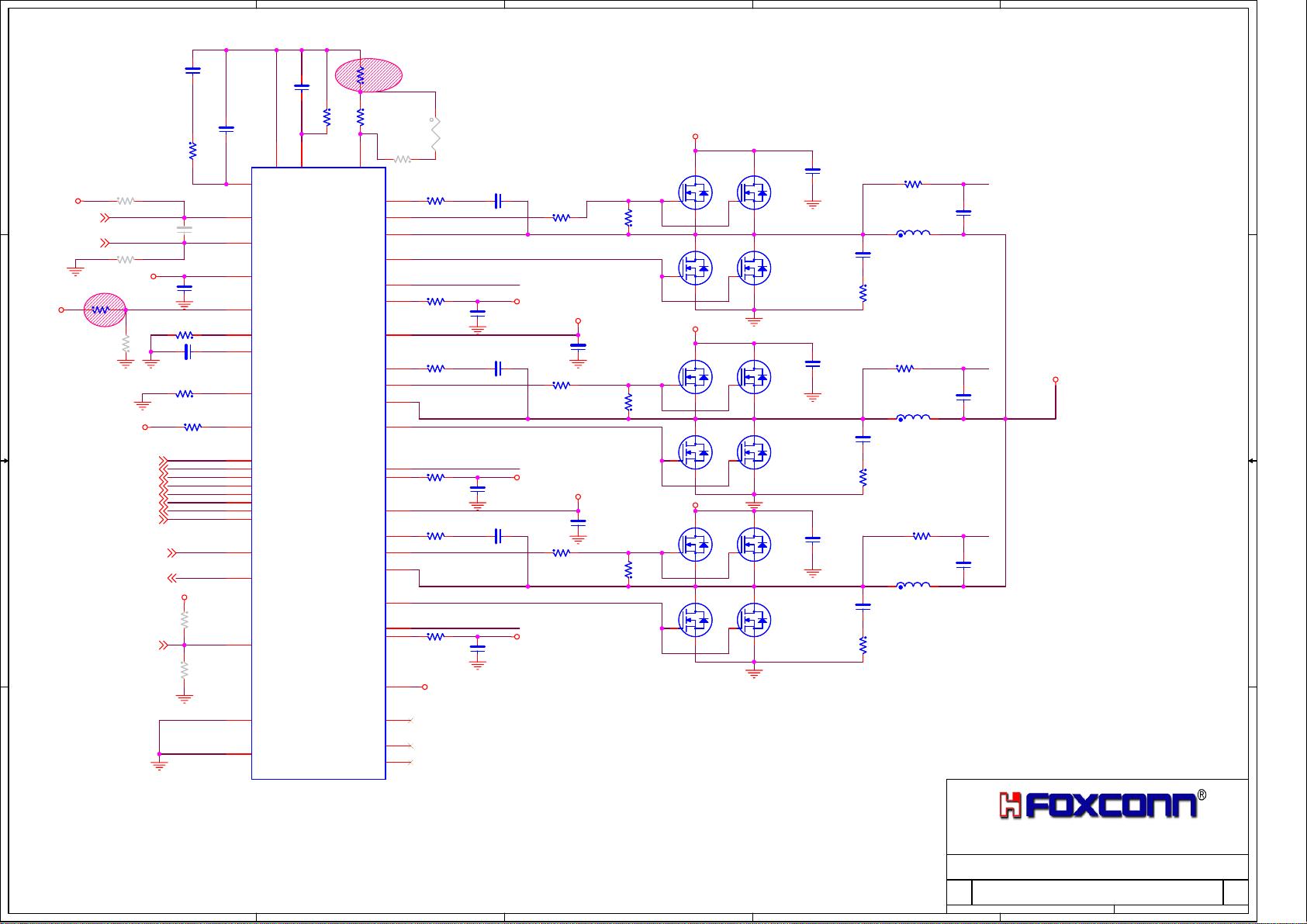

Title

Size Document Number Rev

Date: Sheet

of

FOXCONN PCEG

945M03

AC

740Thursday, July 13, 2006

CK410 ClockGen

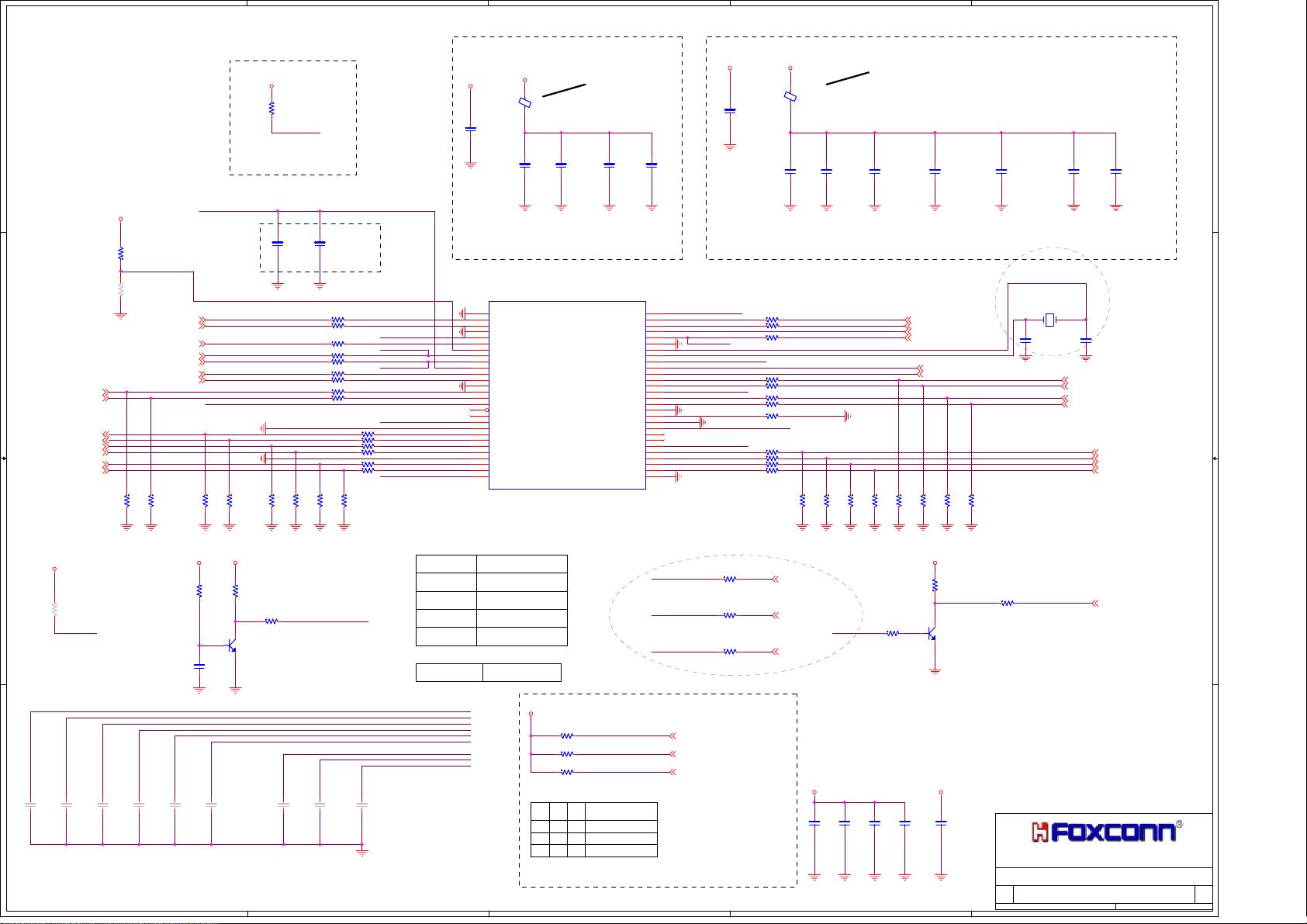

Title

Size Document Number Rev

Date: Sheet

of

FOXCONN PCEG

945M03

AC

740Thursday, July 13, 2006

CK410 ClockGen

SMBus Address :1101-0010

Analog/SRC/CPU Power Filter

TBD

Add EMI caps. for cross planes after layout

EMI CAPS.

00

0

FSB Frequency

266MHz(1066)

0

0

1

0

1

0

133MHz(533)

200MHz(800)

BSEL TABLE

place near pin 10

XDP/PCI-E selection

High=XDP enable

Low=PCI-E enable

PCI/REF/USB Power Filter

PCIEX2

PCIEX4

100 MHz(PCIEX)

GMCH

ICH7

100 MHz(SRC SATA)

SRCCLK_SATA ICH7

FS_AFS_BFS_C

Real time input pin to change frequency

to a pre_programmed under or over clock

entries located in the ROM table

making the IREF 2.32 mA

place near pin 5, 56 place near pin 48

place near pin 37place near pin 43place near pin 19, 28, 34

latched select input for 24 or 48 MHz output

1: 24MHz

0: 48MHz

PCIEX1

PCIEX3

X16 connector

20pf

B

R2

4.7K

+/-5%

R0603

R2

4.7K

+/-5%

R0603

R49

4.7K

+/-5%

R0603

Dummy

R49

4.7K

+/-5%

R0603

Dummy

R42

49.9

+/-1%

R0603

R42

49.9

+/-1%

R0603

R54 470

+/-5%R0603

R54 470

+/-5%R0603

12

*

C20

10pF

50V, NPO, +/-5%

C0603

Dummy

*

C20

10pF

50V, NPO, +/-5%

C0603

Dummy

R33

49.9

+/-1%

R0603

R33

49.9

+/-1%

R0603

R15 0R15 0

B

E C

Q1

PMBT3904

@945GZ@945PL

Q1

PMBT3904

@945GZ@945PL

R8 33R8 33

12

*

C30

0.1uF

C0603

25V, Y5V, +80%/-20%

*

C30

0.1uF

C0603

25V, Y5V, +80%/-20%

R10 33R10 33

12

*

C16

C0603

33pF

50V, NPO, +/-5%

*

C16

C0603

33pF

50V, NPO, +/-5%

12

*

C22

10pF

50V, NPO, +/-5%

C0603

Dummy

*

C22

10pF

50V, NPO, +/-5%

C0603

Dummy

R43

49.9

+/-1%

R0603

R43

49.9

+/-1%

R0603

R45

4.7K

+/-5%

R0603

R45

4.7K

+/-5%

R0603

R25

33

+/-5%

R0603

R25

33

+/-5%

R0603

R27

33

+/-5%

R0603

R27

33

+/-5%

R0603

R34

49.9

+/-1%

R0603

R34

49.9

+/-1%

R0603

12

*

C9

0.1uF

C0603

25V, Y5V, +80%/-20%

*

C9

0.1uF

C0603

25V, Y5V, +80%/-20%

R24 33 +/-5%R24 33 +/-5%

R53

2.2K

R0603

+/-5%

R53

2.2K

R0603

+/-5%

12

*

C27

10pF

50V, NPO, +/-5%

C0603

Dummy

*

C27

10pF

50V, NPO, +/-5%

C0603

Dummy

R52

2.2K R0603 +/-5%

@945G@945P

R52

2.2K R0603 +/-5%

@945G@945P

R47

2.2K R0603

+/-5%

R47

2.2K R0603

+/-5%

R32

49.9

+/-1%

R0603

R32

49.9

+/-1%

R0603

R44

49.9

+/-1%

R0603

R44

49.9

+/-1%

R0603

R35

49.9

+/-1%

R0603

R35

49.9

+/-1%

R0603

R9

33

+/-5%

R0603

R9

33

+/-5%

R0603

12

*

C2

0.1uF

C0603

25V, Y5V, +80%/-20%

*

C2

0.1uF

C0603

25V, Y5V, +80%/-20%

12

*

C19

10pF

50V, NPO, +/-5%

C0603

Dummy

*

C19

10pF

50V, NPO, +/-5%

C0603

Dummy

*

L1

FB L0805 300 Ohm

*

L1

FB L0805 300 Ohm

R5 33 +/-5%R5 33 +/-5%

12

*

C31

0.1uF

C0603

25V, Y5V, +80%/-20%

*

C31

0.1uF

C0603

25V, Y5V, +80%/-20%

1 2

X1

XTAL-14.318MHz

+/-20PPM

X2O

X1

XTAL-14.318MHz

+/-20PPM

X2O

R615 4.7K

@945GZ@945PL

R615 4.7K

@945GZ@945PL

R31

49.9

+/-1%

R0603

R31

49.9

+/-1%

R0603

R13 33 +/-5%R13 33 +/-5%

R36

49.9

+/-1%

R0603

R36

49.9

+/-1%

R0603

12

*

C10

0.1uF

C0603

25V, Y5V, +80%/-20%

*

C10

0.1uF

C0603

25V, Y5V, +80%/-20%

R1

4.7K

+/-5%

R0603

R1

4.7K

+/-5%

R0603

R14 33R14 33

R29

33

+/-5%

R0603

R29

33

+/-5%

R0603

R51

4.7K

+/-5%

R0603

R51

4.7K

+/-5%

R0603

12

*

C24

10pF

50V, NPO, +/-5%

C0603

Dummy

*

C24

10pF

50V, NPO, +/-5%

C0603

Dummy

R11 33R11 33

R56 470

+/-5%R0603

R56 470

+/-5%R0603

R50

8.2K

+/-5%

R0603@945GZ@945PL

R50

8.2K

+/-5%

R0603@945GZ@945PL

R12 33R12 33

R37

49.9

+/-1%

R0603

R37

49.9

+/-1%

R0603

12

*

C26

10pF

50V, NPO, +/-5%

C0603

Dummy

*

C26

10pF

50V, NPO, +/-5%

C0603

Dummy

R26 33 +/-5%R26 33 +/-5%

12

*

C17

C0603

33pF

50V, NPO, +/-5%

*

C17

C0603

33pF

50V, NPO, +/-5%

GND

1

PCICLK2

2

*Turbo#

6

ITP_EN/PCICLK_F0

7

PCICLK3

3

GND

4

VDDPCI

5

FS_A/PCICLK_F1

8

FS_B/PCICLK_F2

9

VDD48

10

**SEL24_48#/24_48MHz

11

USB_48MHz

12

GND

13

DOTT_96MHz

14

DOTC_96MHz

15

Vtt_PwrGd#_PD

16

PCIEXT0

17

PCIEXC0

18

VDDPCIEX

19

GND

20

PCIEXC1

22

PCIEXT2

23

PCIEXT1

21

PCIEXC2

24

GND

25

SRCCLKT_SATA

26

SRCCLKC_SATA

27

VDDSRC

28

VDDPCI

56

PCICLK1

55

PCICLK0

54

GND

29

PCIEXC3

30

PCIEXT3

31

PCIEXC4

32

PCIEXT4

33

VDDPCIEX

34

CPUCLK_ITP/PCIEXC5

35

CPUCLK_ITP/PCIEXT5

36

VDDA

37

GNDA

38

IREF

39

GND

40

CPUCLKC1

41

CPUCLKT1

42

CPUCLKC0

44

VDDCPU

43

CPUCLKT0

45

SDATA

46

SCLK

47

VDDREF

48

X2

49

X1

50

GND

51

REF0/FS_C

52

Reset#

53

U1

ICS954128AFLF

U1

ICS954128AFLF

R46

10K

+/-5%

R0603

R46

10K

+/-5%

R0603

R55 470

+/-5%R0603

R55 470

+/-5%R0603

R209 33 +/-5%R209 33 +/-5%

12

*

C32

0.1uF

C0603

25V, Y5V, +80%/-20%

*

C32

0.1uF

C0603

25V, Y5V, +80%/-20%

12

*

C34

0.1uF

C0603

25V, Y5V, +80%/-20%

*

C34

0.1uF

C0603

25V, Y5V, +80%/-20%

12

*

C4

0.1uF

C0603

25V, Y5V, +80%/-20%

*

C4

0.1uF

C0603

25V, Y5V, +80%/-20%

12

*

C11

0.1uF

C0603

25V, Y5V, +80%/-20%

*

C11

0.1uF

C0603

25V, Y5V, +80%/-20%

R48

2.2K

+/-5%

r0603h6

@945GZ@945PL

R48

2.2K

+/-5%

r0603h6

@945GZ@945PL

R38

49.9

+/-1%

R0603

R38

49.9

+/-1%

R0603

2 1

L2

FB L0805 300 Ohm

+/-25%

0805

L2

FB L0805 300 Ohm

+/-25%

0805

R17 33R17 33

*

C14

10uF

+-10%

C1206h18

*

C14

10uF

+-10%

C1206h18

R30

33

+/-5%

R0603

R30

33

+/-5%

R0603

R256 33 +/-5%R256 33 +/-5%

R18 33R18 33

R28 33 +/-5%R28 33 +/-5%

R19

33

+/-5%

R0603

R19

33

+/-5%

R0603

R3

4.7K

+/-5%

R0603

Dummy

R3

4.7K

+/-5%

R0603

Dummy

R39

49.9

+/-1%

R0603

R39

49.9

+/-1%

R0603

*

C448

10uF

+-10%

C1206h18

*

C448

10uF

+-10%

C1206h18

12

*

C28

10pF

50V, NPO, +/-5%

C0603

Dummy

*

C28

10pF

50V, NPO, +/-5%

C0603

Dummy

12

*

C23

10pF

50V, NPO, +/-5%

C0603

Dummy

*

C23

10pF

50V, NPO, +/-5%

C0603

Dummy

12

*

C1

0.1uF

C0603

25V, Y5V, +80%/-20%

*

C1

0.1uF

C0603

25V, Y5V, +80%/-20%

R6 33R6 33

12

*

C33

0.1uF

C0603

25V, Y5V, +80%/-20%

*

C33

0.1uF

C0603

25V, Y5V, +80%/-20%

R23 33 +/-5%R23 33 +/-5%

12

*

C5

0.1uF

C0603

25V, Y5V, +80%/-20%

*

C5

0.1uF

C0603

25V, Y5V, +80%/-20%

*

C7

10uF

+-10%

C1206h18

*

C7

10uF

+-10%

C1206h18

12

*

C13

0.1uF

C0603

25V, Y5V, +80%/-20%

*

C13

0.1uF

C0603

25V, Y5V, +80%/-20%

R40

49.9

+/-1%

R0603

R40

49.9

+/-1%

R0603

*

C12

10uF

+-10%

C1206h18

*

C12

10uF

+-10%

C1206h18

R20

33

+/-5%

R0603

R20

33

+/-5%

R0603

R257

49.9

+/-1%

R0603

R257

49.9

+/-1%

R0603

12

*

C15

10nF

C0603

25V, X7R, +/-10%

*

C15

10nF

C0603

25V, X7R, +/-10%

R41

49.9

+/-1%

R0603

R41

49.9

+/-1%

R0603

R7 33R7 33

12

*

C21

10pF

50V, NPO, +/-5%

C0603

Dummy

*

C21

10pF

50V, NPO, +/-5%

C0603

Dummy

R22 470

+/-1%

R0603

R22 470

+/-1%

R0603

12

*

C18

0.22uF

10V, X7R, +/-10%

C0603

*

C18

0.22uF

10V, X7R, +/-10%

C0603

12

*

C8

0.1uF

C0603

25V, Y5V, +80%/-20%

*

C8

0.1uF

C0603

25V, Y5V, +80%/-20%

R261

49.9

+/-1%

R0603

R261

49.9

+/-1%

R0603

R21

33

+/-5%

R0603

R21

33

+/-5%

R0603

B

E C

Q2

PMBT3904

Q2

PMBT3904

12

*

C6

0.1uF

C0603

25V, Y5V, +80%/-20%

*

C6

0.1uF

C0603

25V, Y5V, +80%/-20%