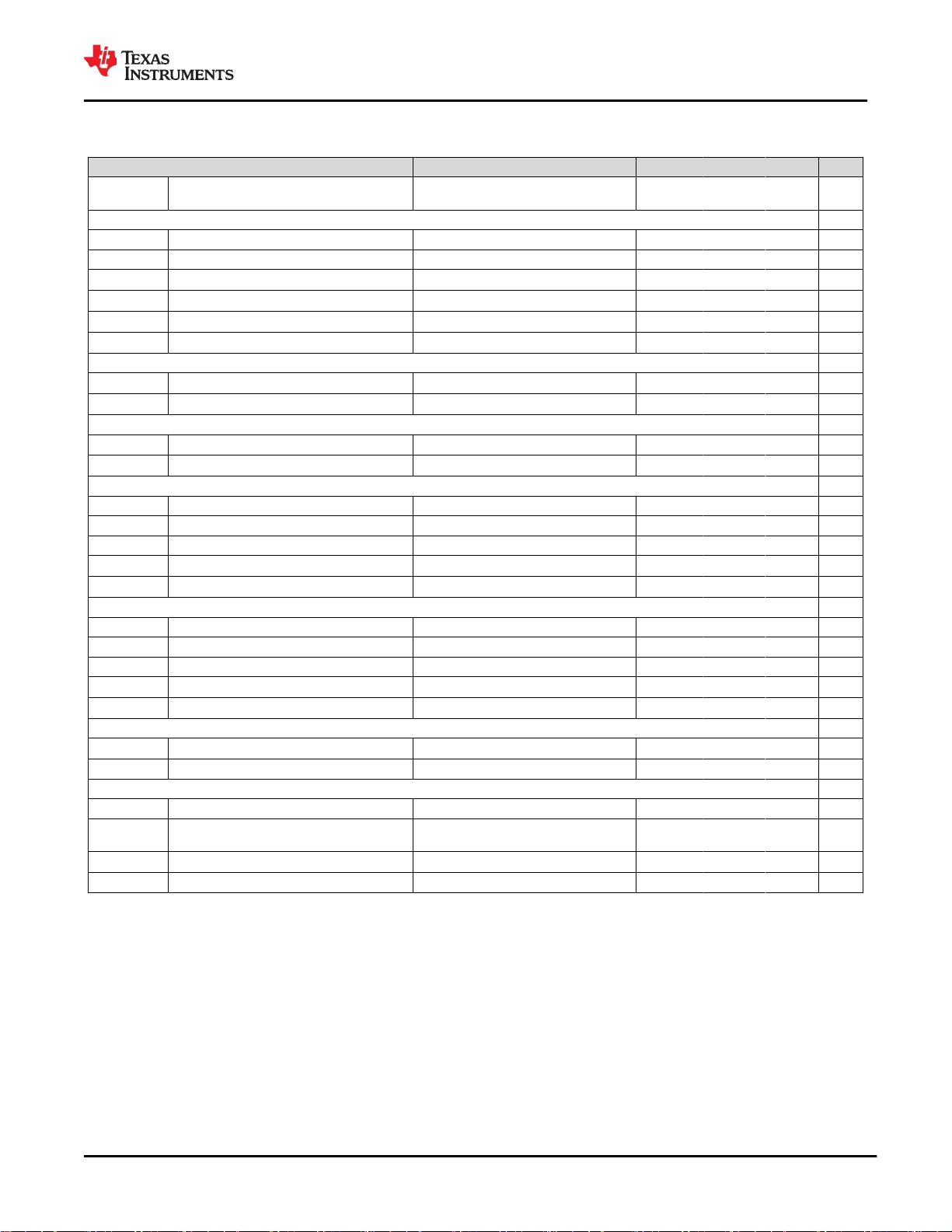

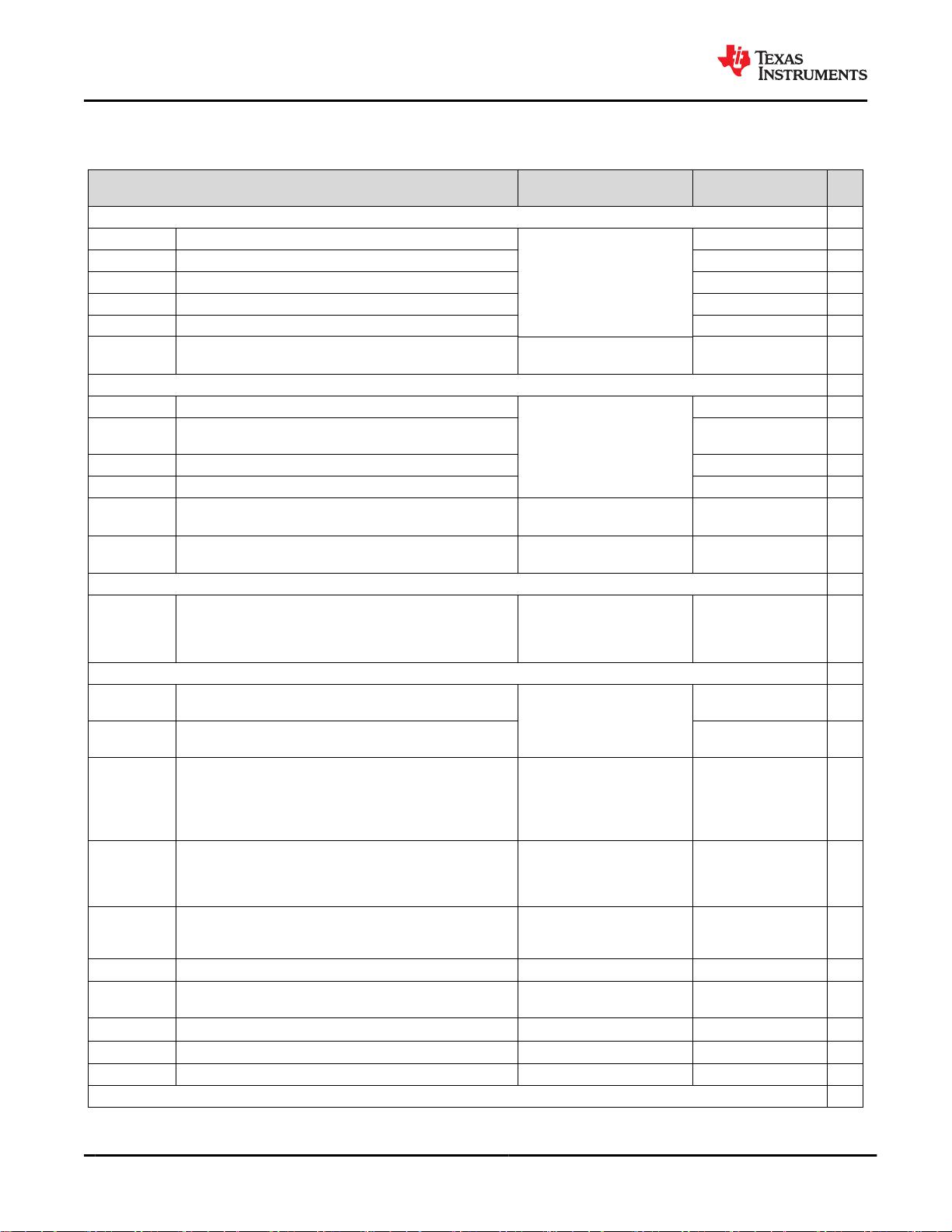

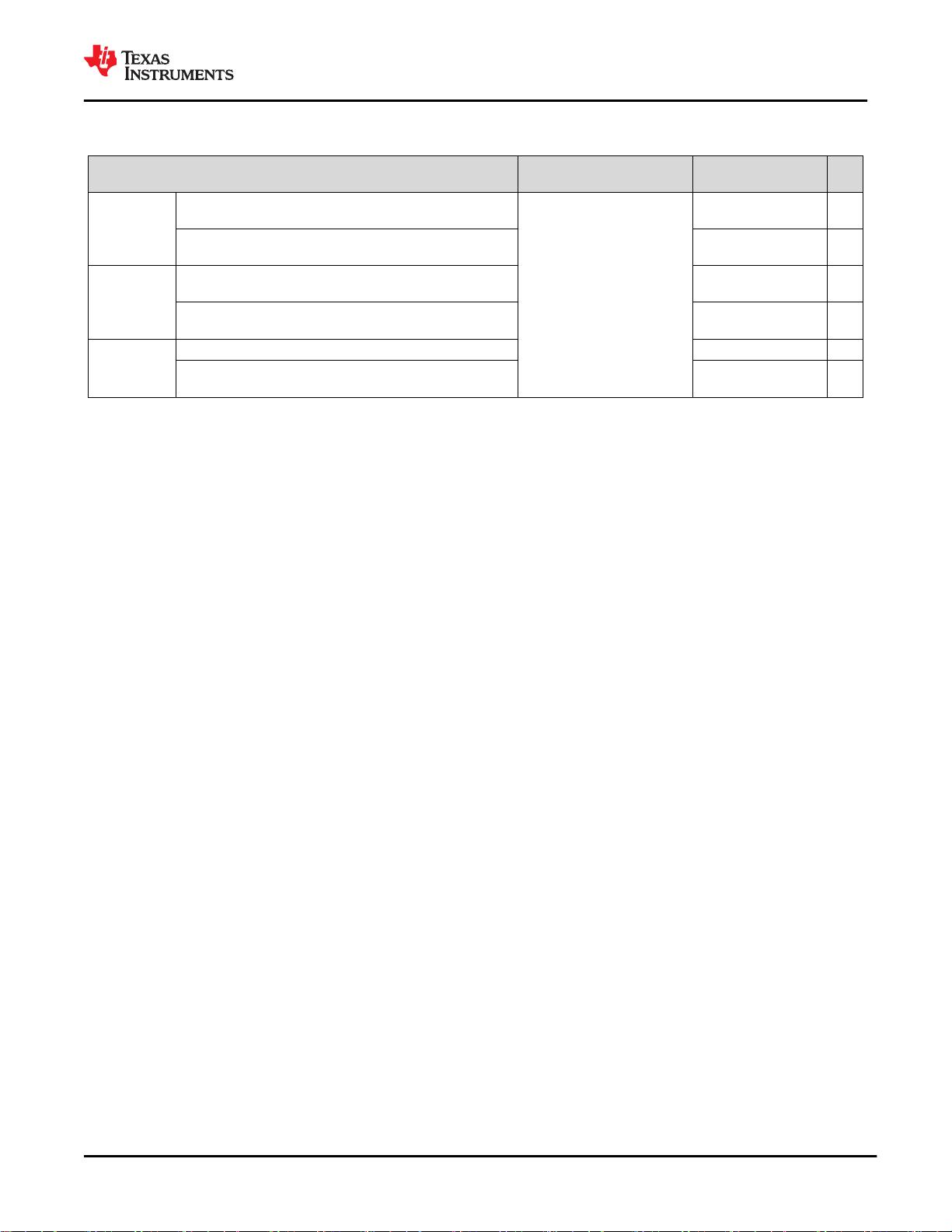

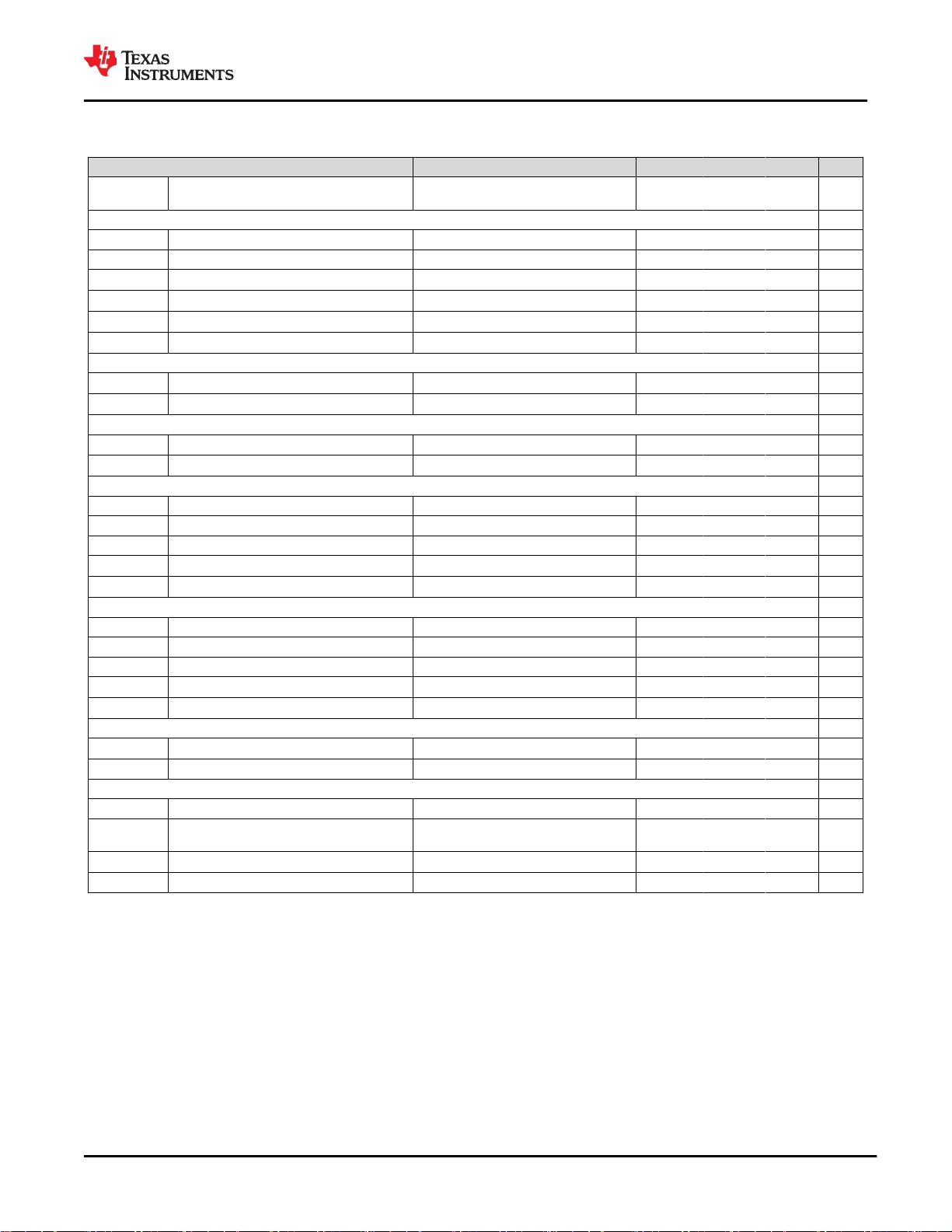

7.7 Electrical Characteristics (continued)

Over recommended operating conditions with T

A

= –55°C to 125°C (unless otherwise noted).

PARAMETER TEST CONDITIONS MIN TYP

(1)

MAX UNIT

R

CBF

Valid differential load impedance range for bus

fault circuitry

R

CM

= R

L

, C

L

= open 45 70

Ω

TXD TERMINAL (CAN TRANSMIT DATA INPUT)

V

IH

High level input voltage 0.7 V

IO

V

V

IL

Low level input voltage 0.3 V

IO

V

I

IH

High level input leakage current TXD = V

CC

= V

IO

= 5.5 V

–2.5

0 1 µA

I

IL

Low level input leakage current TXD = 0 V, V

CC

= V

IO

= 5.5 V

–100 –2.5

µA

I

LKG(OFF)

Unpowered leakage current TXD = 5.5 V, V

CC

= V

IO

= 0 V

–1

0 1 µA

C

I

Input capacitance

V

IN

= 0.4 x sin(2 x π x 2 x 10

6

x t) + 2.5 V

5 pF

RXD TERMINAL (CAN RECEIVE DATA OUTPUT)

V

OH

High level output voltage

See 图 8-3, I

O

= –2 mA.

0.8 V

IO

V

V

OL

Low level output voltage

See 图 8-3, I

O

= –2 mA.

0.2 V

IO

V

nFAULT TERMINAL (FAULT AND STATUS OUTPUT)

V

OH

High level output voltage

See 图 8-1, I

O

= –2 mA.

0.8 V

IO

V

V

OL

Low level output voltage

See 图 8-1 I

O

= 2 mA.

0.2 V

IO

V

nSTB TERMINAL (STANDBY MODE INPUT)

V

IH

High level input voltage 0.7 V

IO

V

V

IL

Low level input voltage 0.3 V

IO

V

I

IH

High level input leakage current nSTB = V

CC

= V

IO

= 5.5 V 0.5 10 µA

I

IL

Low level input leakage current nSTB = 0 V, V

CC

= V

IO

= 5.5 V

–1

1 µA

I

LKG(OFF)

Unpowered leakage current nSTB = 5.5 V, V

CC

= 0V, V

IO

= 0 V

–1

0 1 µA

EN TERMINAL (ENABLE MODE INPUT)

V

IH

High level input voltage 0.7 V

IO

V

V

IL

Low level input voltage 0.3 V

IO

V

I

IH

High level input leakage current EN = V

CC

= V

IO

= 5.5 V 0.5 10 µA

I

IL

Low level input leakage current EN = 0 V, V

CC

= V

IO

= 5.5 V

–1

1 µA

I

LKG(OFF)

Unpowered leakage current EN = 5.5 V, V

CC

= 0V, V

IO

= 0 V

–1

0 1 µA

INH TERMINAL (INHIBIT OUTPUT)

ΔV

H

High level voltage drop INH with respect to V

SUP

I

INH

= –0.5 mA

0.5 1 V

I

LKG(INH)

Leakage current INH = 0 V, Sleep Mode -5 5 µA

Wake TERMINAL (WAKE INPUT)

V

IH

High level input voltage Standby and Sleep Mode V

SUP

- 1.9 V

V

IL

Low level input voltage Standby and Sleep Mode

V

SUP

-

3.5

V

I

IH

High level input current

(5)

WAKE = V

SUP

– 1 V –25 –15

µA

I

IL

Low level input current

(5)

WAKE = 1 V 15 25 µA

(1) All typical values are at 25°C and supply voltages of V

CC

= 5 V, V

IO

= 3.3 V, and R

L

= 60 Ω. Unless otherwise noted.

(2) The recessive bus voltage will be the same if the device is in Normal mode with the nSTB and EN terminals high or if the device is in

Silent mode with the nSTB terminal high and EN terminal low.

(3) The bus output voltage symmetry, V

SYM

, is measured using R

TERM

/ 2 = 30 Ω and C

SPLIT

= 4.7 nF as shown in 图 10-4

(4) Specified by design and verified during product validation using the ISO 11898-2 method.

(5) To minimize system level current consumption, the WAKE pin will automatically configure itself based on the applied voltage to have

either an internal pull-up or pull-down current source. A high level input results in an internal pull-up and a low level input results in an

internal pull-down. For more information, refer to Section 10.4.6.2

www.ti.com.cn

TCAN1043-Q1, TCAN1043H-Q1

TCAN1043HG-Q1, TCAN1043G-Q1

ZHCSH19E – NOVEMBER 2017 – REVISED MARCH 2021

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

9

Product Folder Links: TCAN1043-Q1 TCAN1043H-Q1 TCAN1043HG-Q1 TCAN1043G-Q1