Verilog HDL基础教程:快速入门与建模指南

需积分: 50 103 浏览量

更新于2024-07-23

1

收藏 286KB PDF 举报

Verilog HDL入门教程是一份详细的指南,专为想要学习Verilog Hardware Description Language (HDL) 的初学者设计。该教程涵盖了Verilog语言的基础概念,从第1章的前言开始,逐步深入到设计方法学,包括数字电路设计的不同方式,如结构化、数据流和行为建模。章节中详细讲解了:

1. 语法基础:介绍了Verilog的书写规范,包括关键字、标识符、定义等,以及数据类型,如线网类型和寄存器类型,以及算术、关系、逻辑、位逻辑和条件运算符的使用。

2. 模块和结构:模块是Verilog设计的核心,3.1章节讲述了模块的定义、结构和语法,包括简单事例演示,以及模块端口的定义。

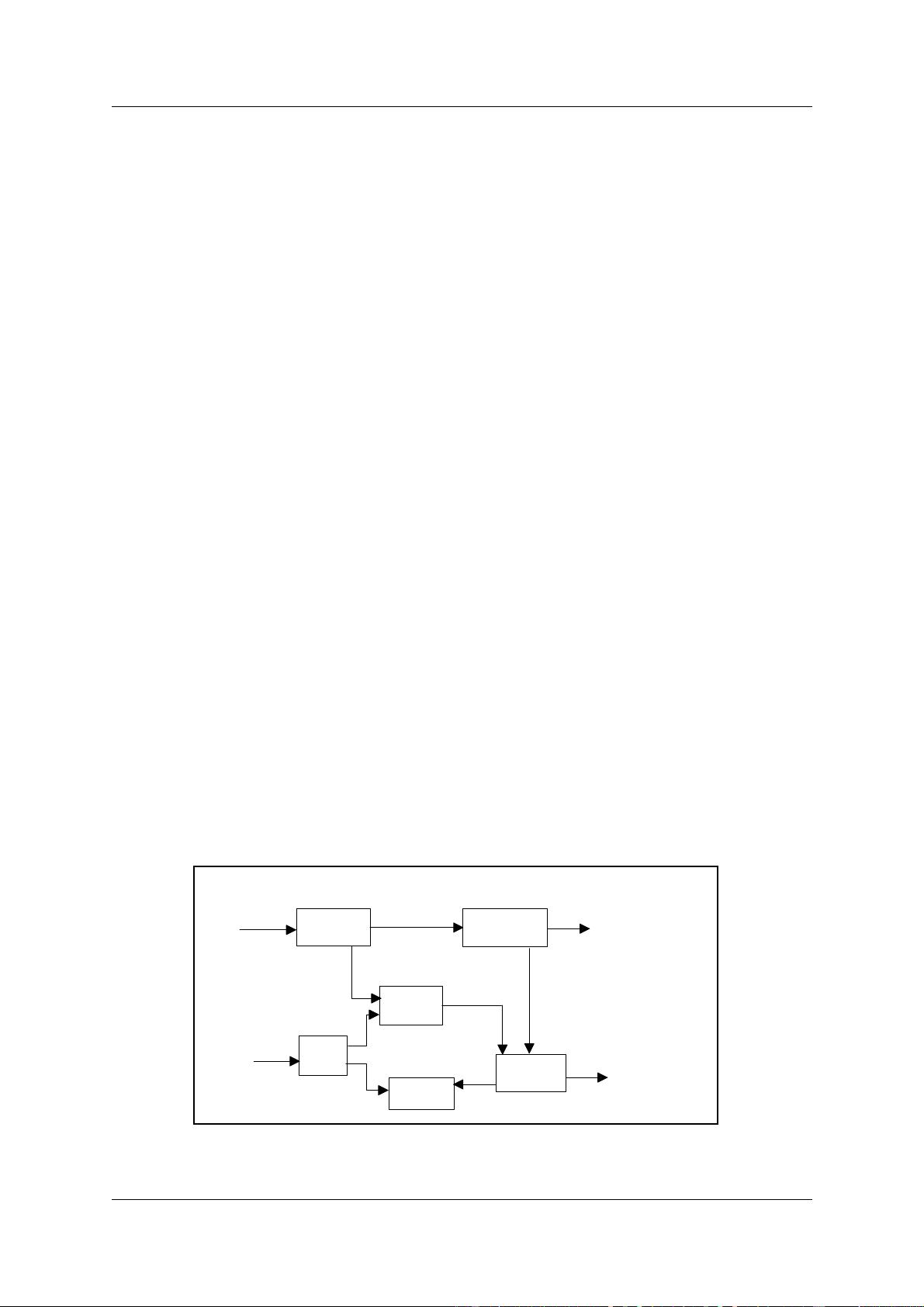

3. 建模方式:3.3部分讨论了三种建模方式——结构化、数据流和行为描述,这些是设计中的主要表达手段,如连续赋值、阻塞赋值和顺序语句块。

4. 行为建模:7.1节从简介开始,讲解了行为建模的具体实例,涉及过程赋值语句和控制结构,如case和if-else语句。

5. 数据流建模:6.1至6.3章节详细介绍了数据流建模,包括连续赋值语句、阻塞赋值语句和具体实例。

6. 结构化建模:5.1至5.4章节阐述了如何使用实例化语句进行模块化设计,并提供了具体实例来加深理解。

7. 保留字和注释:还介绍了Verilog的保留字列表,以及如何使用注释来提高代码可读性。

通过本教程,读者可以系统地学习到Verilog HDL语言的基本要素,从理解基本语法到进行实际的设计建模,为初学者在华为或其他公司进行HDL设计打下坚实的基础。

2020-09-02 上传

2023-07-05 上传

2023-06-14 上传

2023-09-15 上传

2023-11-05 上传

2023-06-26 上传

2023-08-28 上传

powerhome3

- 粉丝: 0

- 资源: 1

最新资源

- WPF渲染层字符绘制原理探究及源代码解析

- 海康精简版监控软件:iVMS4200Lite版发布

- 自动化脚本在lspci-TV的应用介绍

- Chrome 81版本稳定版及匹配的chromedriver下载

- 深入解析Python推荐引擎与自然语言处理

- MATLAB数学建模算法程序包及案例数据

- Springboot人力资源管理系统:设计与功能

- STM32F4系列微控制器开发全面参考指南

- Python实现人脸识别的机器学习流程

- 基于STM32F103C8T6的HLW8032电量采集与解析方案

- Node.js高效MySQL驱动程序:mysqljs/mysql特性和配置

- 基于Python和大数据技术的电影推荐系统设计与实现

- 为ripro主题添加Live2D看板娘的后端资源教程

- 2022版PowerToys Everything插件升级,稳定运行无报错

- Map简易斗地主游戏实现方法介绍

- SJTU ICS Lab6 实验报告解析