LatticeECP3 FPGA技术规格详解

需积分: 10 97 浏览量

更新于2024-07-22

收藏 10.31MB PDF 举报

“LatticeECP3 Family Data Sheet”

LatticeECP3系列是一款由Lattice Semiconductor公司推出的高性能 FPGA(Field-Programmable Gate Array)产品。这款芯片家族提供了更高级的逻辑密度,增强了系统集成能力,适用于各种高速通信和接口应用。

主要特性包括:

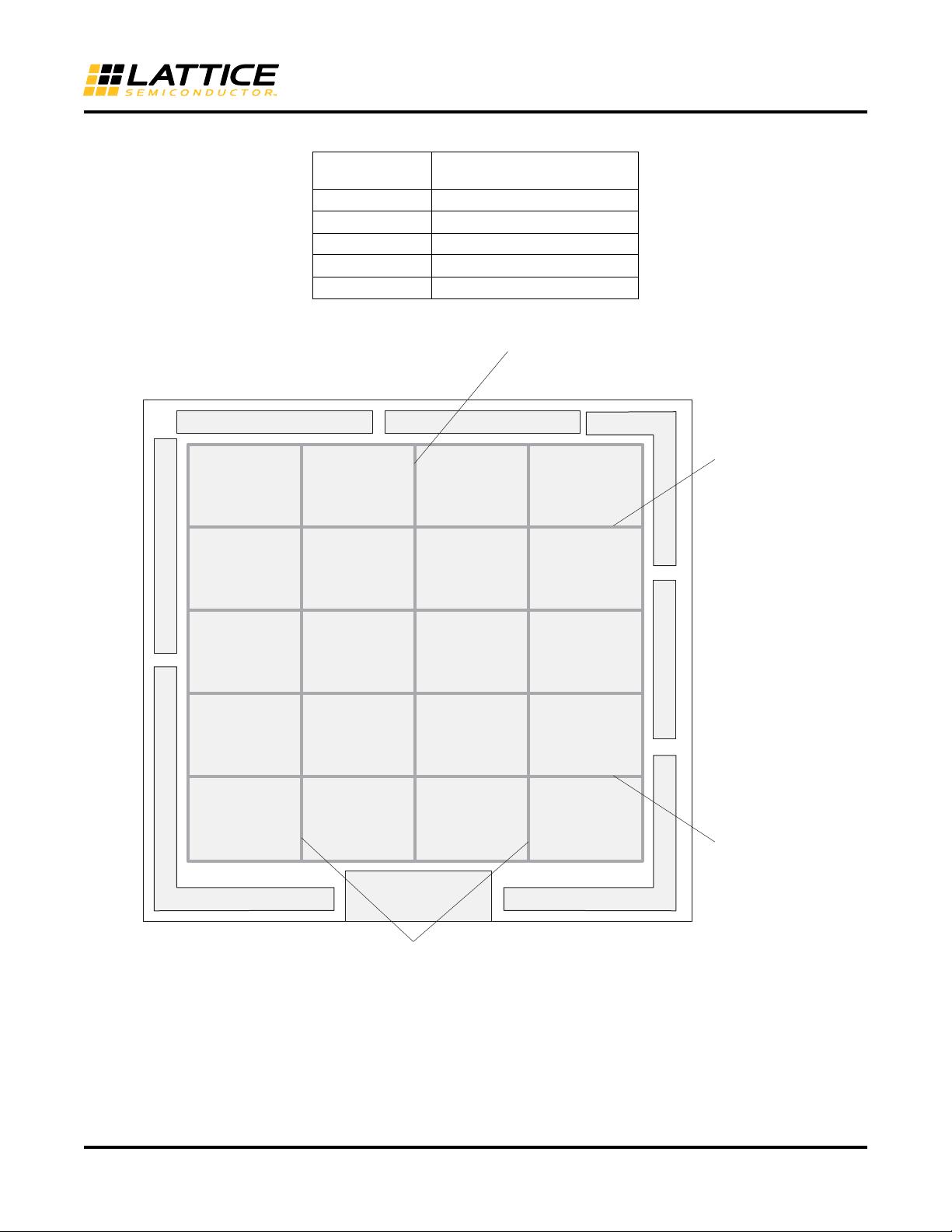

1. **更高的逻辑密度**:LatticeECP3系列提供了17K到149K的查找表(LUTs),这使得设计者能够在单一芯片上实现更复杂的逻辑功能,从而减少系统中的组件数量,提高集成度。

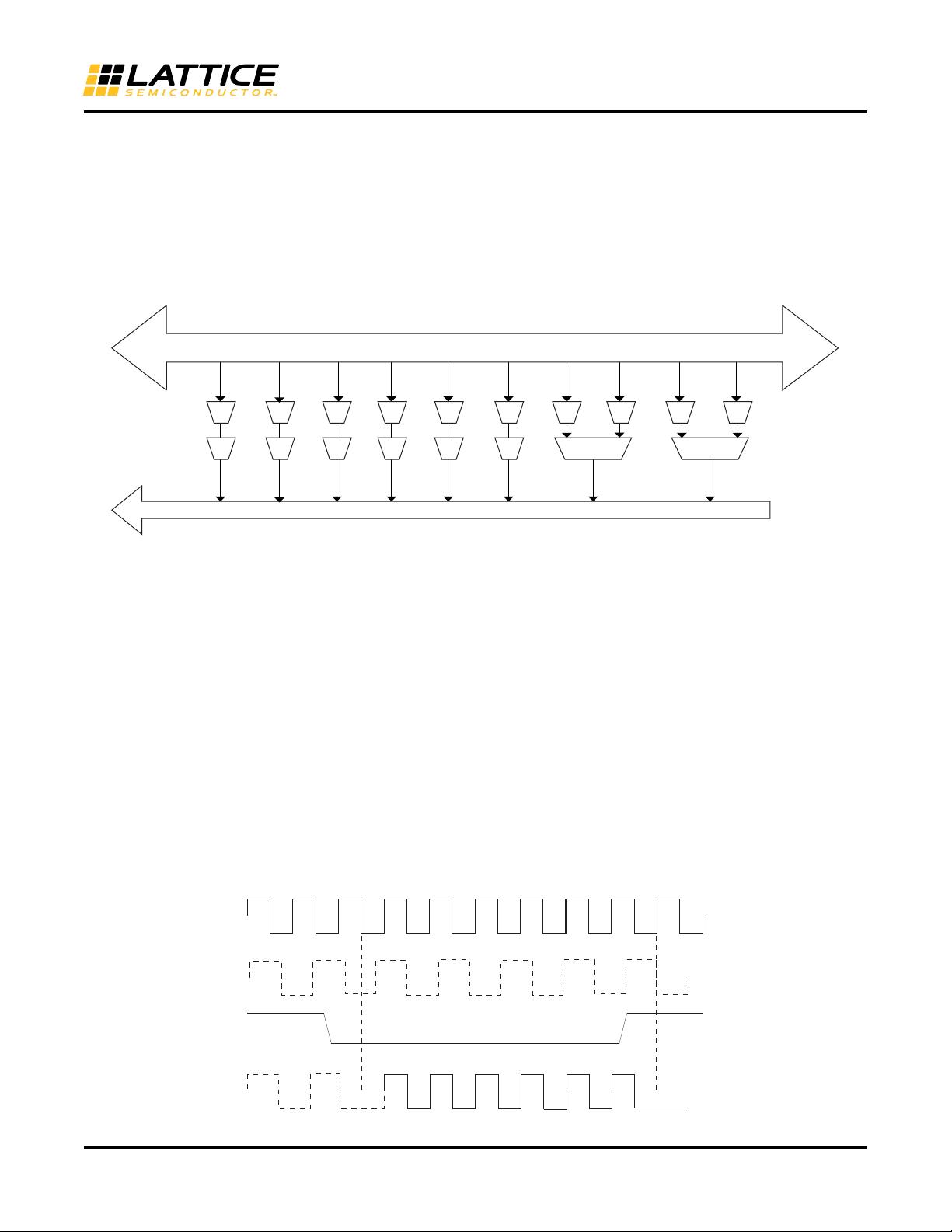

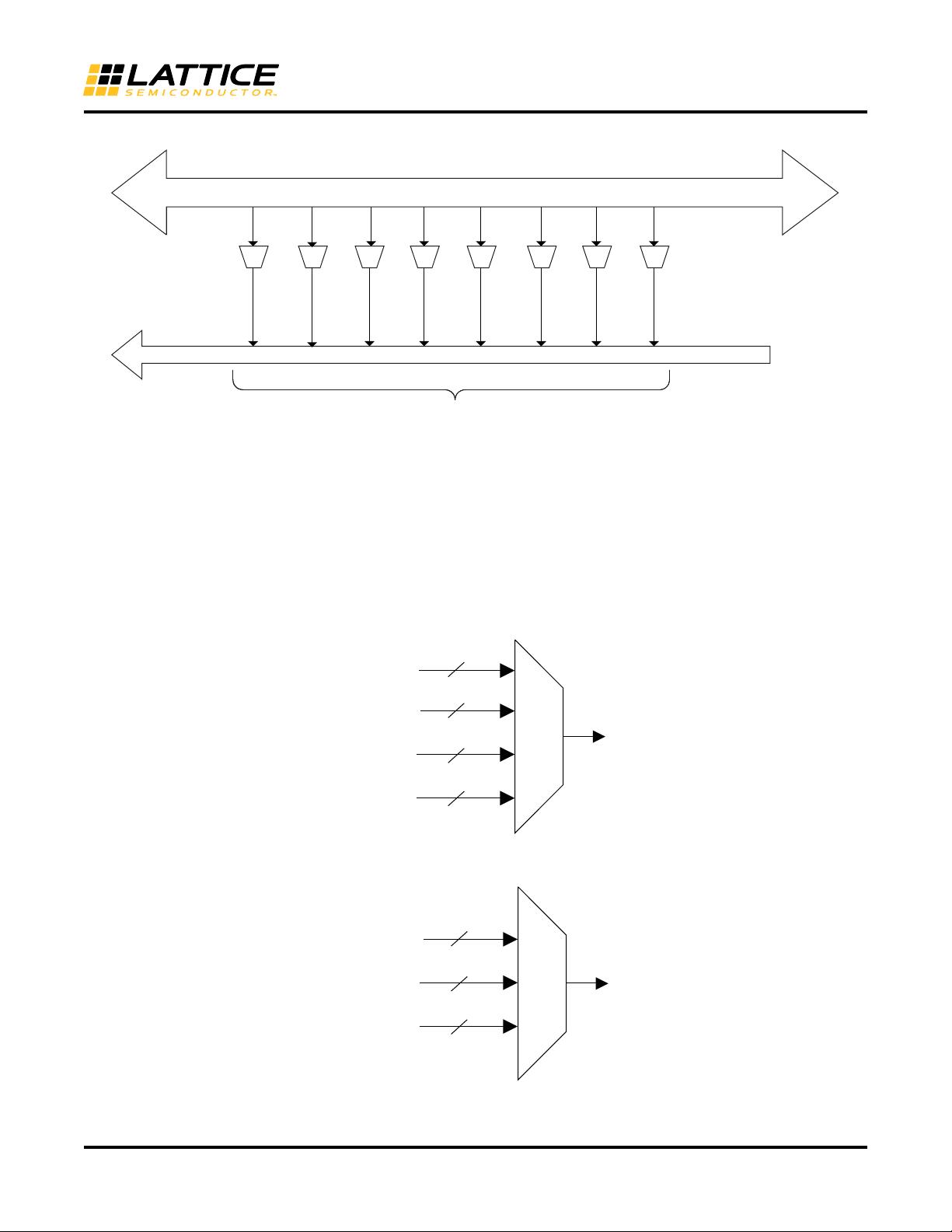

2. **嵌入式SERDES**:该系列支持从150Mbps到3.2Gbps的通用8b10b、10位SERDES和8位SERDES模式,每个通道的数据速率可达230Mbps到3.2Gbps,适用于多种协议,如PCI Express、SONET/SDH、Ethernet(1GbE、SGMII、XAUI)、CPRI、SMPTE 3G以及Serial RapidIO。这样的高速串行数据传输能力使得LatticeECP3成为高速数据通信的理想选择。

3. **sysDSP™技术**:LatticeECP3集成了sysDSP模块,这是一种完全可级联的片上架构,提供12到160个片,专门用于高性能的乘加运算。sysDSP包含一个强大的54位算术逻辑单元(ALU),支持时间分复用MAC共享、舍入和截断操作。每个片可以支持半36x36、两个18x18或四个9x9的乘法器,极大地提升了数字信号处理性能。

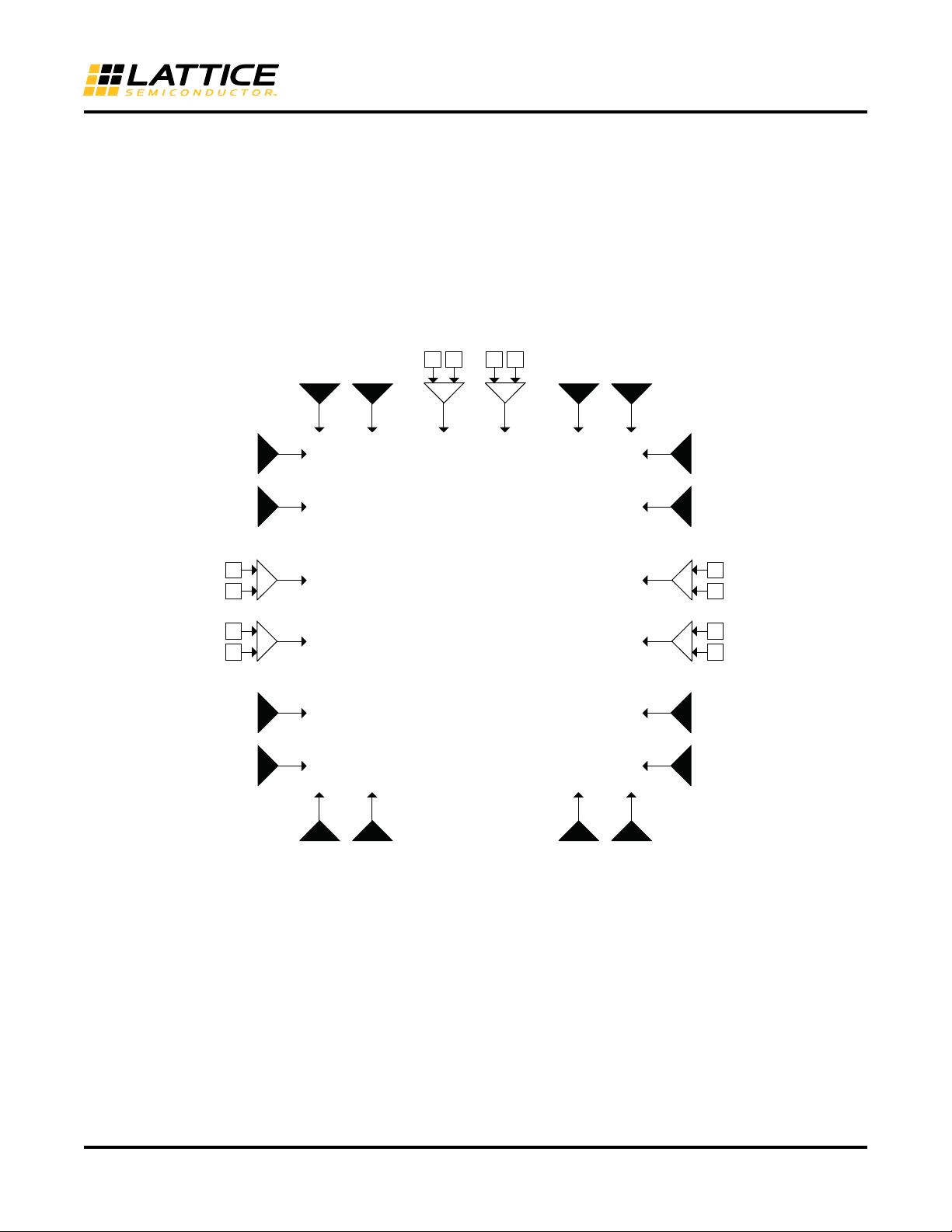

4. **灵活性和可扩展性**:由于其丰富的I/O数量(从116到586个),LatticeECP3能够适应广泛的接口需求,无论是简单的GPIO还是复杂的高速串行接口,都能灵活应对。

5. **不断更新的技术**:数据表提到的版本是DS1021 Version 02.2 EA,发布于2012年4月,表明Lattice Semiconductor致力于不断更新和优化其产品,以满足不断变化的市场需求和技术进步。

6. **知识产权保护**:Lattice Semiconductor对其商标、专利和免责声明有明确的规定,并提醒用户注意所有规格和信息可能会随时变更,使用者需要访问官方网站获取最新信息。

LatticeECP3 FPGA家族凭借其高逻辑密度、高速嵌入式SERDES和sysDSP技术,成为高性能、高集成度系统设计的优选解决方案,广泛应用于通信、数据处理、网络和工业控制等领域。

2018-09-13 上传

2019-03-15 上传

2021-10-03 上传

2013-12-31 上传

2009-10-13 上传

2020-10-25 上传

2022-06-15 上传

kkk81

- 粉丝: 1

- 资源: 7

最新资源

- JavaScript实现的高效pomodoro时钟教程

- CMake 3.25.3版本发布:程序员必备构建工具

- 直流无刷电机控制技术项目源码集合

- Ak Kamal电子安全客户端加载器-CRX插件介绍

- 揭露流氓软件:月息背后的秘密

- 京东自动抢购茅台脚本指南:如何设置eid与fp参数

- 动态格式化Matlab轴刻度标签 - ticklabelformat实用教程

- DSTUHack2021后端接口与Go语言实现解析

- CMake 3.25.2版本Linux软件包发布

- Node.js网络数据抓取技术深入解析

- QRSorteios-crx扩展:优化税务文件扫描流程

- 掌握JavaScript中的算法技巧

- Rails+React打造MF员工租房解决方案

- Utsanjan:自学成才的UI/UX设计师与技术博客作者

- CMake 3.25.2版本发布,支持Windows x86_64架构

- AR_RENTAL平台:HTML技术在增强现实领域的应用