"基于Quartus II软件的FPGA原理图方式设计流程解析与实践"

版权申诉

104 浏览量

更新于2024-03-07

收藏 1.5MB PDF 举报

本章以FPGA原理图方式设计为主线,通过三个完整的例子,详细介绍了Quartus II软件的使用以及开发板的操作。首先,通过设计一个3-8译码器,读者可以掌握组合逻辑电路设计的方法,并初步了解Quartus II采用原理图方式进行设计的流程。在设计过程中,读者将会逐步掌握FPGA开发的流程,以及基本的设计方法和仿真分析方法。

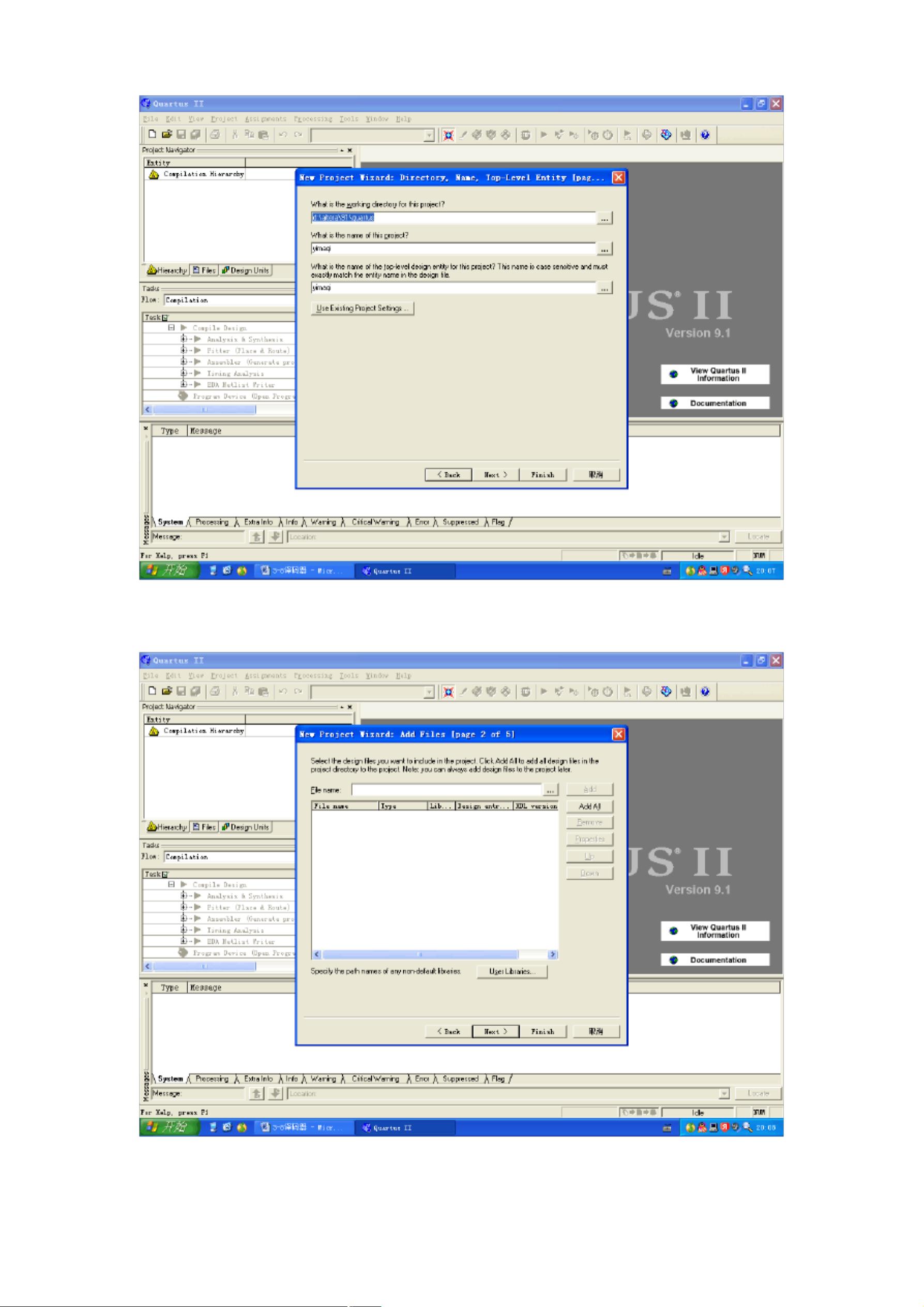

在设计步骤中,首先需要建立工程文件。通过双击桌面上的Quartus II图标,打开软件界面,并选择File下拉菜单中的New Project Wizard,然后按照提示逐步完成工程的建立。工程目录的选择非常重要,建议根据个人需要更改存放路径,以避免在默认路径下存放多个工程文件而造成混乱。

接下来,进行原理图的绘制工作。选择File下拉菜单中的New进行新建原理图,然后在打开的页面中拖动所需元件进行电路的搭建。在设计3-8译码器的过程中,需要注意元件的连接方式以及属性的设置,确保整个设计符合逻辑要求。对于不熟悉元件的功能或者属性设置的部分,可以通过查阅帮助文档或者进行在线搜索来获取更多信息。

一旦原理图设计完成,就需要进行编译和综合的操作。点击Quartus II工具栏中的Compile按钮,软件将对原理图进行分析和综合,生成相应的逻辑网表。如果编译过程中出现错误或者警告,需要及时检查并调整设计,以确保顺利通过编译。

接着,进行时序约束的设置和时序分析。在设计中,时序约束非常重要,可以帮助FPGA实现电路的稳定运行。通过点击Quartus II工具栏中的TimeQuest按钮,打开时序约束工具,在其中设置时钟频率、延迟等参数,然后进行时序分析,保证电路符合时序要求。

最后,进行下载与仿真操作。连接FPGA开发板,点击Quartus II工具栏中的Download按钮,将设计好的逻辑网表下载到FPGA芯片中。同时,可以通过Quartus II提供的仿真工具,对电路进行仿真分析,验证设计的正确性和稳定性。

通过这三个设计示例,读者可以深入了解FPGA设计与开发的全过程,掌握Quartus II软件的使用方法,熟悉开发板的操作流程。同时,通过实际操作,读者还可以提升对组合逻辑电路设计、时序约束设置等方面的技能,为以后更复杂的FPGA设计奠定良好的基础。希望通过本章的学习,读者能够快速有效地掌握FPGA设计与开发的方法,为未来的项目实践提供有力支持。

2023-04-04 上传

2023-04-04 上传

2023-02-26 上传

2022-04-22 上传

2023-02-27 上传

2022-11-02 上传

apple_51426592

- 粉丝: 9839

- 资源: 9652

最新资源

- 利用J2EE+Apache Tomcat搭建J2EE环境

- EIGRP的不等价负载均衡.pdf

- 搞活 富裕挥发油 答合金钢合金钢环境

- 函数信号发生器,函数信号发生器

- Struts2+Spring应用电子书

- ASP电子商务毕业设计论文

- Support Vector Machines for Classification and Regression

- dreamweaver asp 网上选课系统论文

- java笔记.pdf

- Flex 3 Cookbook

- 《控制反转,依赖注入》

- Flex与JSON及XML的互操作

- SQL语言艺术.pdf

- struts中文手册

- linux下搭建iscsi

- 软件无线电设计的A_D采样分析.pdf