时序逻辑电路分析与设计:从基础知识到Verilog实现

版权申诉

70 浏览量

更新于2024-07-03

收藏 11.57MB PPT 举报

"数字电子技术基础第六章 时序逻辑电路的分析与设计"

时序逻辑电路是数字系统中的重要组成部分,它不仅处理当前输入,还依赖于之前的状态。本讲义主要涵盖时序逻辑电路的基本概念、分析方法以及设计技巧。

6.1 时序逻辑电路的基本概念

时序逻辑电路由两部分组成:组合电路和存储电路(如触发器)。这些电路具有反馈机制,使得输出不仅取决于当前输入,还与电路的当前状态有关。根据时钟信号的同步性,时序电路分为同步时序电路和异步时序电路。在同步电路中,所有存储元件(如触发器)在同一个时钟周期内更新状态;而在异步电路中,状态更新可能不同步,没有统一的时钟控制。

6.1.1 时序逻辑电路的模型与分类

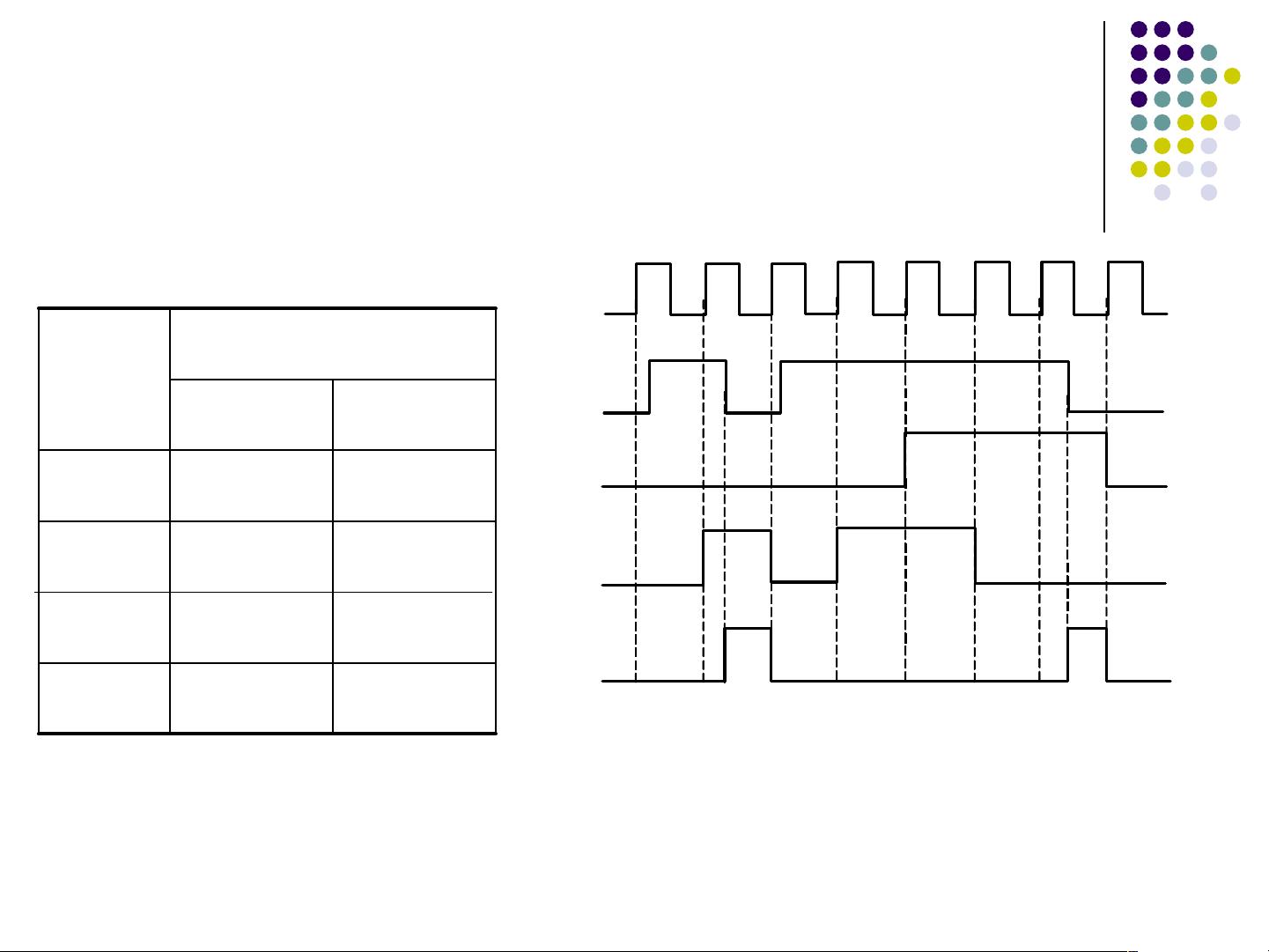

时序电路的一般化模型包括激励方程(E=g(I,S))、状态方程(Sn+1=h(E,Sn))和输出方程(O=f(I,S)),分别描述了输入、状态变化和输出之间的关系。同步与异步时序电路的主要区别在于时钟控制的统一性。

6.1.2 时序电路逻辑的表达

时序电路的功能可以通过多种方式表达,如状态转换真值表、状态图、状态方程和驱动方程。状态转换真值表列出所有可能的输入和状态组合以及相应的下一个状态。

6.2 同步时序逻辑电路的分析

同步电路分析主要关注状态转换图和状态表,通过这些工具可以理解电路的动态行为,确定其状态机的性质。

6.3 同步时序逻辑电路的设计

设计同步时序逻辑电路通常涉及定义初始状态、确定状态转换规则、构建状态编码和选择适当的存储元件类型(如D触发器、JK触发器或T触发器)。

6.4 异步时序逻辑电路的分析

异步电路的分析更为复杂,因为状态更新可能不是同步的,需要考虑时钟路径延迟和竞争冒险等现象。

6.5 几个典型的时序逻辑集成电路

常见的时序逻辑集成电路包括计数器(如二进制计数器、模N计数器)、寄存器(如数据寄存器、移位寄存器)等,它们在数字系统中有广泛应用。

6.6 用Verilog描述时序逻辑电路

硬件描述语言如Verilog提供了描述时序逻辑电路的语法,可以用来定义触发器、计数器等组件,以及整个时序系统的结构。

6.7 时序逻辑可编程逻辑器件

现代可编程逻辑器件(如FPGA)提供了实现时序逻辑电路的平台,可以通过配置这些器件来实现各种复杂的时序逻辑设计。

教学基本要求强调了对时序逻辑电路的描述方式、分析方法、设计方法的熟练掌握,以及对计数器、寄存器、移位寄存器等典型时序逻辑电路的理解和应用。通过深入学习这一章节,学生将能够理解和设计复杂的数字系统中的时序逻辑部分。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-06-17 上传

2022-06-17 上传

智慧安全方案

- 粉丝: 3820

- 资源: 59万+

最新资源

- Angular程序高效加载与展示海量Excel数据技巧

- Argos客户端开发流程及Vue配置指南

- 基于源码的PHP Webshell审查工具介绍

- Mina任务部署Rpush教程与实践指南

- 密歇根大学主题新标签页壁纸与多功能扩展

- Golang编程入门:基础代码学习教程

- Aplysia吸引子分析MATLAB代码套件解读

- 程序性竞争问题解决实践指南

- lyra: Rust语言实现的特征提取POC功能

- Chrome扩展:NBA全明星新标签壁纸

- 探索通用Lisp用户空间文件系统clufs_0.7

- dheap: Haxe实现的高效D-ary堆算法

- 利用BladeRF实现简易VNA频率响应分析工具

- 深度解析Amazon SQS在C#中的应用实践

- 正义联盟计划管理系统:udemy-heroes-demo-09

- JavaScript语法jsonpointer替代实现介绍