CAZAC序列在OFDM时频同步方案中的FPGA实现

60 浏览量

更新于2024-09-02

1

收藏 488KB PDF 举报

"基于CAZAC序列的OFDM时频同步方案及FPGA实现"

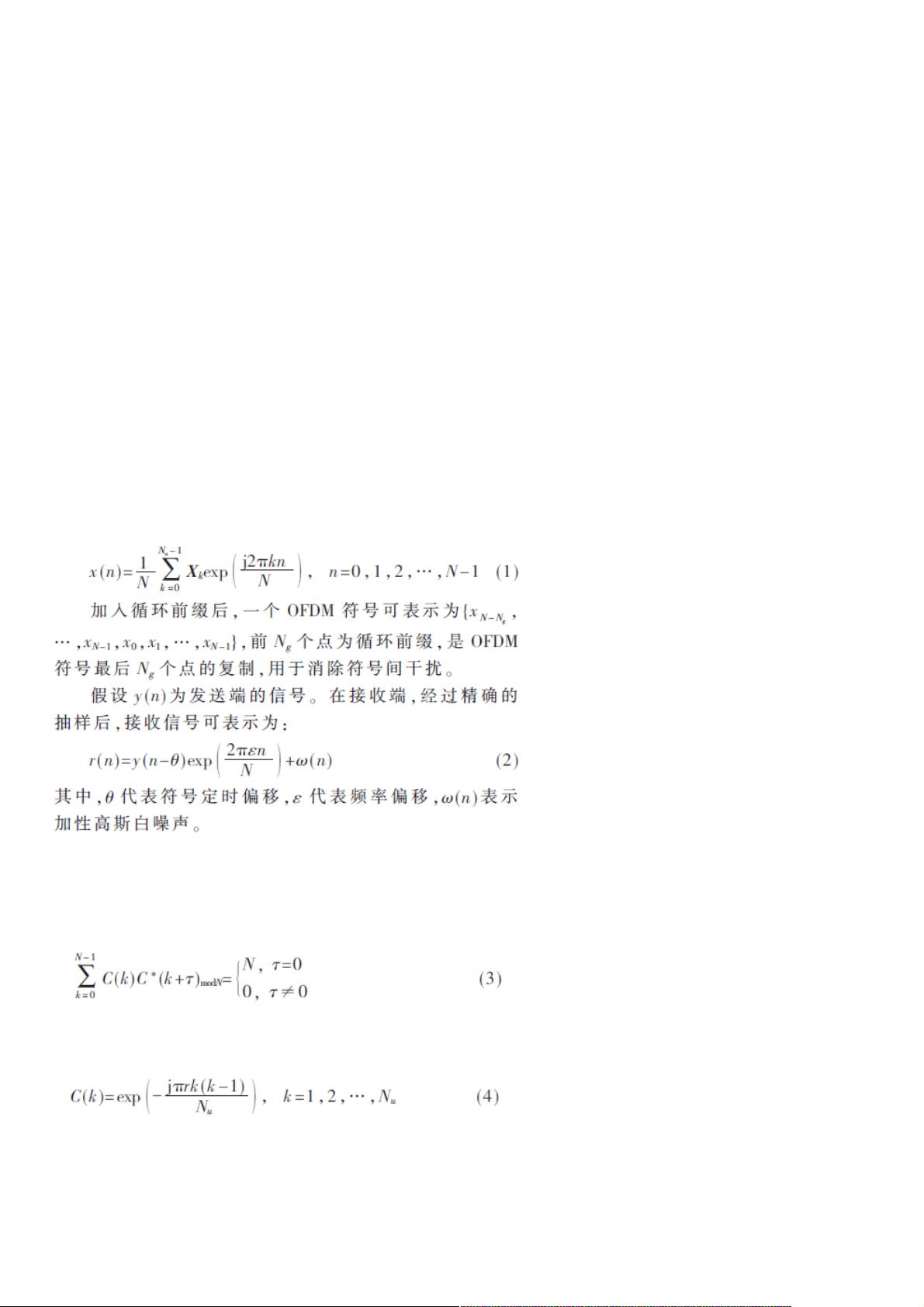

本文针对正交频分复用(OFDM)系统中的时频同步问题,提出了一种基于CAZAC序列的高效同步方法,并提供了FPGA实现的详细框架和实测效果。在OFDM系统中,时频同步至关重要,因为任何时钟偏差或频率偏移都会破坏子载波间的正交性,导致同信道干扰,降低通信质量。传统的同步算法如基于循环前缀(CP)的方案和基于特殊结构的算法,在某些情况下可能无法提供足够的同步精度或存在实现复杂度高的问题。

本方案首先利用时域中的同步参考符号进行分段相关,得出定时估计。接着,结合最大似然法进行粗略的时偏和频偏估计,以提高同步的初始准确性。随后,通过快速傅里叶变换(FFT)将同步参考符号从时域转换到频域,利用CAZAC序列的特性——其自相关性形成脉冲函数,且傅里叶变换后仍保持CAZAC特性——进行整偏估计。CAZAC序列的恒定包络和低峰均比有助于减少同步过程中的误差。最后,通过比较两个填充了不同CAZAC序列的同步参考符号在频域的表现,进行精细的时频偏估计,进一步提升同步精度。

CAZAC序列,全称为零自相关区序列,其在不同时间偏移下的自相关函数为零,这使得它们在同步应用中表现出优异的性能。在本文中,使用两个不同生成多项式r1和r2产生的CAZAC序列C1(k)和C2(k),分别填充到两个OFDM符号的子载波上,以利用它们的差异性进行同步。此外,还生成了一个长度为Nu的序列C3(k),其生成多项式为r3=|r2-r1|,用于辅助同步过程。

FPGA实现部分,文章详细描述了各个模块的硬件设计,包括数据处理单元、相关器、FFT单元和同步控制器等,这些模块协同工作,实现高效的时频同步。实测结果显示,该方案在定时估计性能和频偏估计精度上优于传统方法,并具有良好的工程实用性,适合实际通信系统中的部署。

总结来说,本文提出的基于CAZAC序列的OFDM时频同步方案,不仅在理论上具有较高的同步精度,而且在FPGA实现上资源占用较少,易于集成,对于提升OFDM系统的整体性能有显著作用。这种方法为解决OFDM系统同步问题提供了一种新的、实用的途径,特别是在应对多径衰落和频偏问题时,表现出了优越性。

232 浏览量

116 浏览量

295 浏览量

168 浏览量

164 浏览量

616 浏览量

186 浏览量

266 浏览量

116 浏览量

weixin_38629362

- 粉丝: 6

- 资源: 967