2位CMOS同步计数器设计详解与HSPICE模拟

需积分: 9 154 浏览量

更新于2024-08-04

收藏 1.2MB DOC 举报

在本篇文章中,作者针对的是一个基于半导体集成电路技术的2位二进制计数器设计项目。该设计利用了Hspice软件和Virtuoso软件,结合数字电路课程的知识,主要目标是通过CMOS工艺来实现。设计的核心内容包括以下几个部分:

1. 设计任务与要求:

- 设计任务明确,目标是利用32nm工艺进行设计,并要求学生熟悉和掌握集成电路芯片电路设计及模拟技术。

- 具体任务包括:确定设计方案,绘制电路原理图,编写Hspice网表文件,进行功能验证、性能分析(如功耗、延时),以及对电路参数如管子尺寸的调整。

2. 设计思路与方案:

- 计数器采用同步设计,采用了两个上升沿触发的D触发器作为计数的基本单元,这保证了计数的同步性。

- 电路设计中涉及的主要逻辑门电路包括8个传输门、9个非门和1个异或门,这些是构建二进制计数器的关键组件。

- 原理图中可以看到PMOS和NMOS管的运用,这是CMOS工艺的核心,利用双极型晶体管实现低功耗和高集成度。

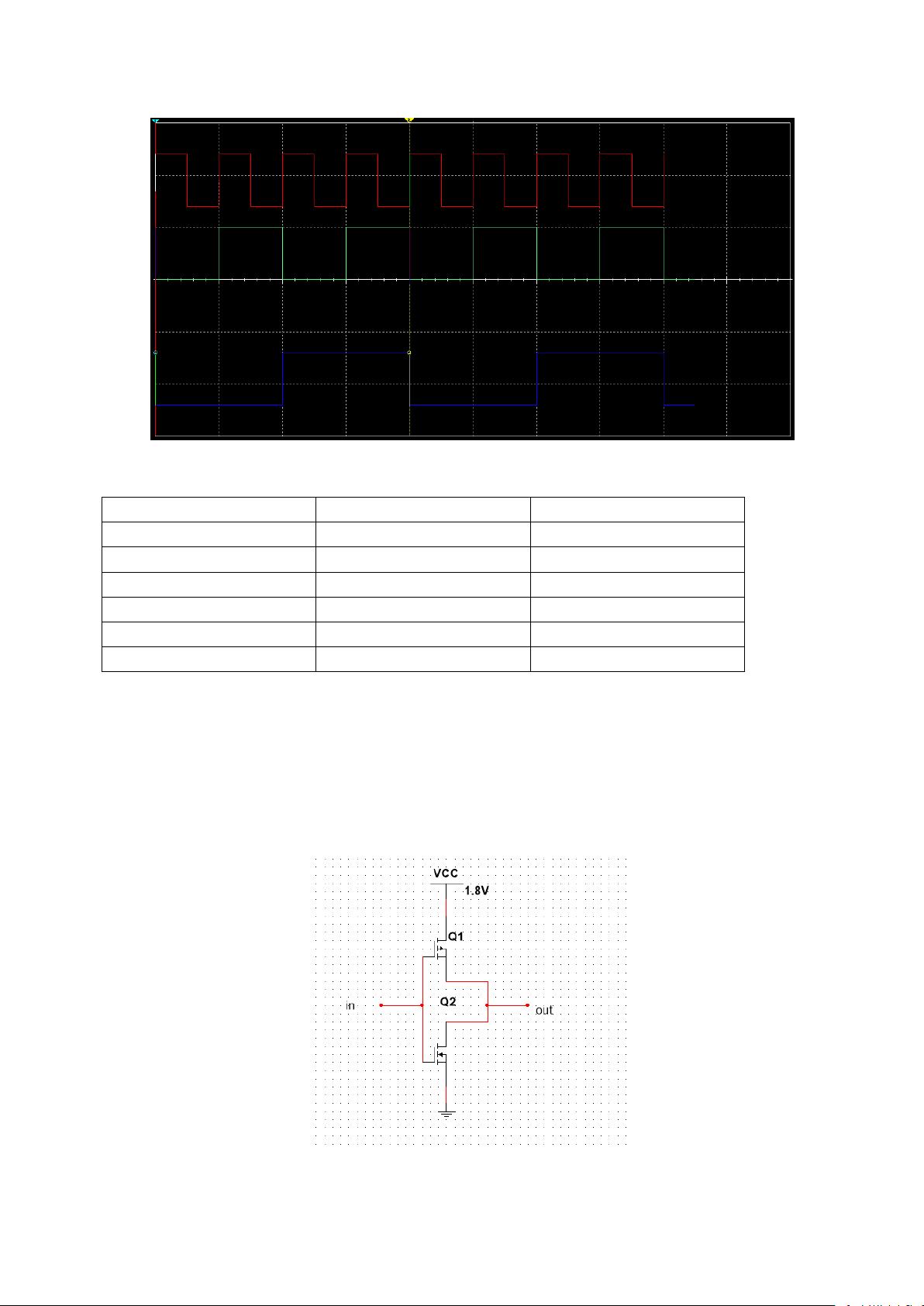

3. 仿真与结果分析:

- 功能仿真着重检查计数器是否按照预期工作,通过观察十进制数的波形和高位输出,验证计数逻辑的正确性。

- 负载驱动能力的仿真旨在评估计数器在不同外部条件下的工作稳定性,确保其能有效驱动负载。

- 功耗和延时的仿真提供了关于电路效率的重要数据,这对于实际应用中的性能优化至关重要。

- 管子尺寸的改变,如W和L的调整,影响了电路的特性,通过动态仿真分析,可以优化设计参数以达到最佳性能。

4. 总结:

- 本文提供了一个完整的设计流程,从任务设定到实际操作,再到结果分析,展示了理论知识如何转化为实际设计的过程,有助于学习者深入理解并实践数字电路设计技巧。

通过这篇文章,读者将了解到如何在实际工程环境中运用Hspice和Virtuoso等工具,进行电路设计、仿真和性能评估,同时提升对CMOS工艺和数字逻辑的理解。对于希望从事集成电路设计的学生或工程师来说,这是一个实用且具有教学价值的学习资源。

2195 浏览量

4105 浏览量

811 浏览量

1776 浏览量

1088 浏览量

4682 浏览量

点击了解资源详情

1570 浏览量

2024-11-03 上传

Solr、

- 粉丝: 21

- 资源: 16

最新资源

- rabbitmq3.8.9&otp21.3配套版本)

- taskcat:测试所有CloudFormation内容! (使用TaskCat)

- 傅里叶级数:可以找到一个函数的傅里叶级数-matlab开发

- TripPlanner:首次测试

- WebSocket-Chatroom:使用gorilla,nhooyr.io包实作WebSocket聊天室

- STM32F4xx中文参考手册(1).zip

- prosper-loan-dataset-findings:该数据集包含113,937笔贷款,每笔贷款有81个变量,包括贷款金额,借款人利率(或利率),当前贷款状态,借款人收入以及许多其他变量

- ChipGenius芯片精灵V4.00 --U盘芯片检测工具

- eSmithCh_V5_14:交互式史密斯圆图,绘制必要的线条来解决传输线或电子耦合问题。尝试并享受它-matlab开发

- 行业-2020年AI新基建白皮书.rar

- jQuery数字滚动累加动画插件

- 码头工人注册表

- 学历教育财务管理 宏达学历教育报名财务管理系统 v1.0

- datastructure_exercise

- github-file-icons::card_index_dividers:一个浏览器扩展,为GitHub,GitLab,gitea和gogs提供了不同的文件类型不同的图标

- Multiple-markers-on-google-maps