VHDL实现8位数字频率计与MODELSIM仿真详解

需积分: 9 88 浏览量

更新于2024-12-24

收藏 147KB DOC 举报

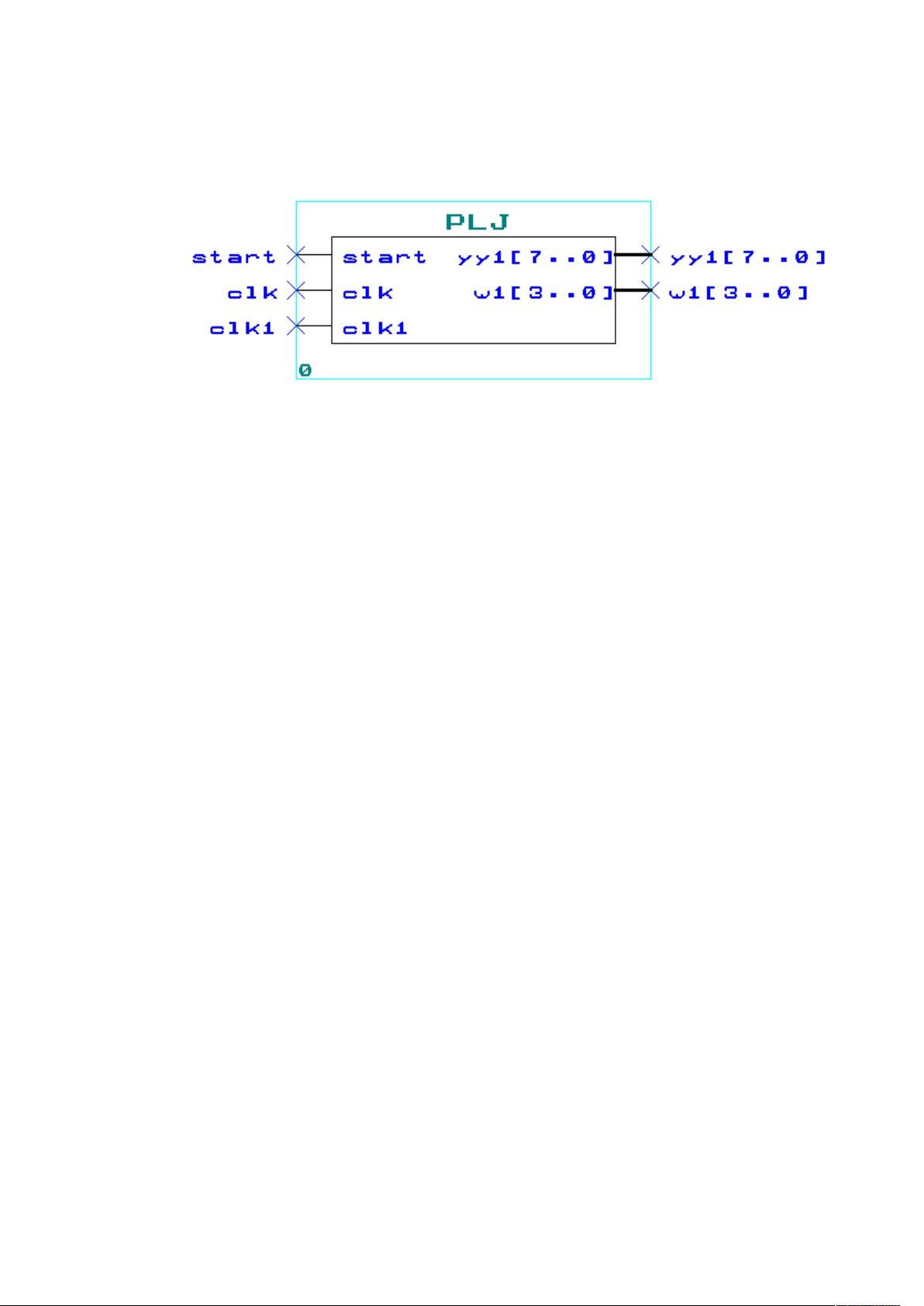

本文档详细介绍了如何使用VHDL语言设计和实现一个8位数字频率计模块,用于精确测量输入信号的频率。该频率计的核心部分是一个4位显示的频率计数器,结合7位十进制计数器和BCD码转换,能够自动选择并动态显示有效数据的高4位,以kHz为单位。设计中涉及到的关键组件包括复位信号(start)、系统时钟(clk)、被测信号(clk1)以及输出的八段码(yy1)和数码管位选信号(w1)。

在VHDL实体(plj)部分,定义了输入端口如复位(start)、系统时钟(clk)和被测信号(clk1),以及输出端口如八段码显示和数码管位选信号。实体中还声明了多个内部信号,如十进制计数器(b1-b7)、BCD码寄存器(bcd)、计数器系数(q和qq)、使能信号(en)和小数点控制信号(sss)。

在行为级架构(behavof PLjis)中,有两个主要进程。第一个进程(process second)负责处理持续时间一秒的闸门信号,通过复位信号(start)初始化计数器q,并在系统时钟上升沿递增,当q达到最大值后重置为0。这个进程还控制使能信号en,仅在没有复位且被测信号有效时才使计数器工作。

第二个进程(process and2)则根据en信号和被测信号(clk1)的状态来更新BCD码寄存器bcd,同时控制小数点的显示。当计数器结果达到一定条件时,会将有效数据的高4位bcd代码存储到bcd0-bcd3中,以便于后续的动态显示。

此外,文档还包含了与MODELSIM仿真器的集成,通过仿真波形图来验证程序的正确性,这对于理解VHDL设计的实际运行行为非常关键。通过模拟信号变化,可以观察到频率计如何随着输入信号频率的变化实时更新显示,以及小数点的切换等行为。

总结来说,本资源提供了一个实用的VHDL设计实例,涵盖了从频率计的设计思路、模块划分到实际电路行为的仿真过程,对初学者理解和实现类似的数字逻辑项目具有很高的参考价值。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2011-11-02 上传

2009-05-12 上传

2022-09-20 上传

2022-09-22 上传

csuhuangzhixin

- 粉丝: 0

- 资源: 8

最新资源

- mealprep:Vue.js Web应用程序将食谱rolodex,meapprepper和卡路里计算器结合在一起

- jedis-2.8.0-API文档-中文版.zip

- Draft Tue Nov 20 10:59:58 CST 2018-数据集

- 图片内隐藏文件-易语言

- Flappy-Bird:Flappy Bird的原生Android克隆:front-facing_baby_chick:

- 如何使用自由口连接多个S7-200.zip西门子PLC编程实例程序源码下载

- ao-security:最佳实践安全性变得可用

- spfylibrary-1.0

- DataVisualizationJSON:来自 JSON 输入 URL 的数据可视化

- svelte-router

- C决赛:我在亨利·福特学院举行的C班的最后作业

- yukiyuki

- grunt-dom-munger:使用CSS选择器读取和操作HTML的艰巨任务

- CoFFEE-开源

- dffdf:dfdf

- Python库 | aws_cdk.aws_neptune-1.118.0-py3-none-any.whl