基于EDA技术的序列信号检测器设计与VHDL实现

需积分: 33 58 浏览量

更新于2024-07-31

3

收藏 390KB DOC 举报

"EDA课程设计—序列信号检测器"

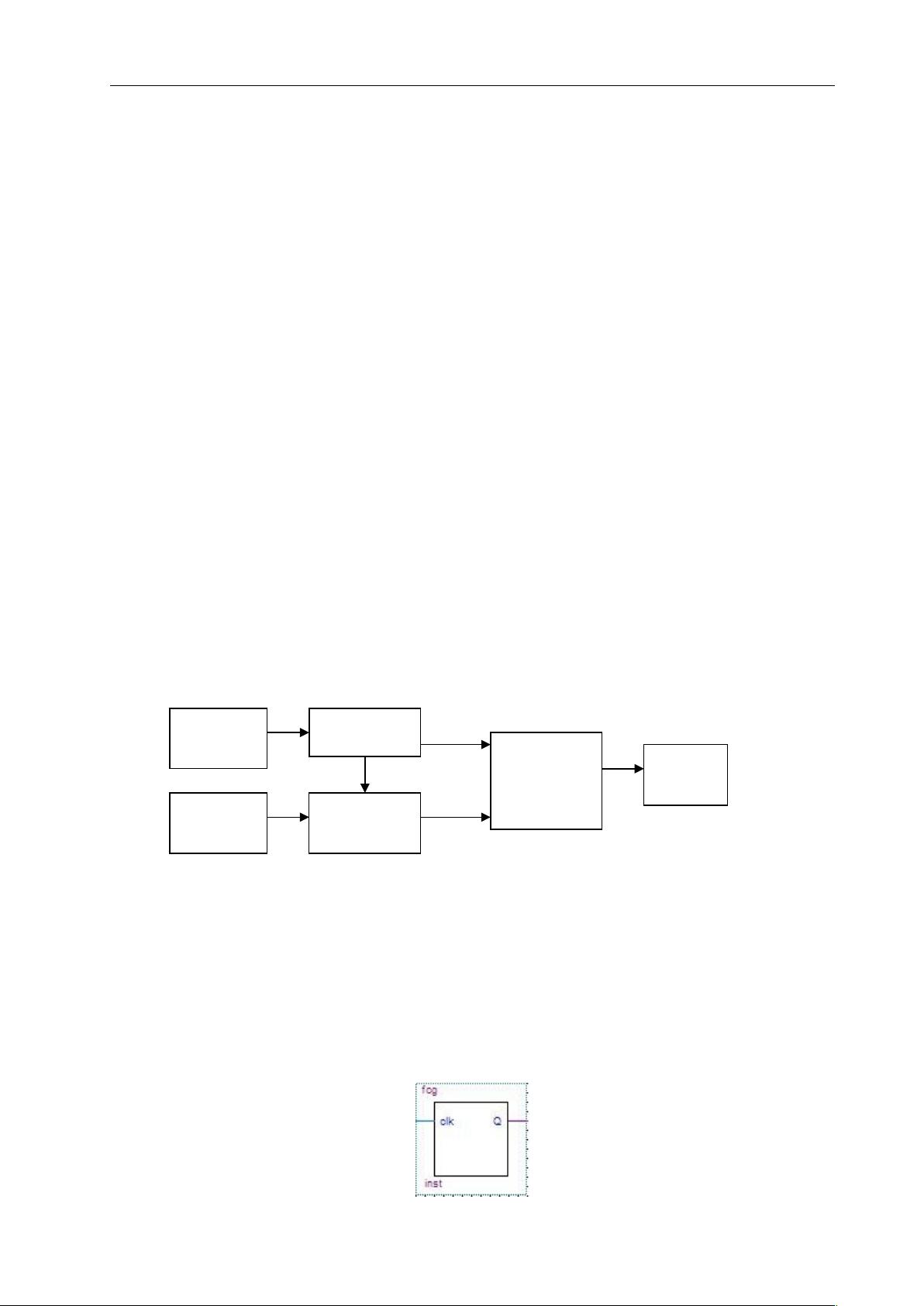

在本次EDA课程设计中,目标是创建一个序列信号检测器,该设备能识别并检测输入序列是否为特定的模式,即"1110101101"。设计的重点在于构建一个有限状态机(FSM),这种机器能够根据输入序列的状态变化进行逻辑判断,从而确定输入是否匹配预设的序列。

有限状态机是一种抽象计算模型,它有若干个状态,并且每个状态根据输入和当前状态会转移到下一个状态。在这个设计中,FSM需要能够识别输入序列中的每个数字,并根据这些数字逐个过渡到相应的状态,直到完整序列被检测到。状态转换图是描述这种行为的图形表示,它显示了不同状态之间的转移关系以及触发这些转移的输入条件。

为了实现这个FSM,需要使用VHDL(Very High-Speed Integrated Circuit Hardware Description Language)进行编程。VHDL是一种硬件描述语言,允许设计师在行为、数据流、寄存器传输和门级等多个抽象级别描述数字系统。在VHDL中,可以定义FSM的数据结构、状态变量和状态转换逻辑,以实现对输入序列的检测。

在编写好VHDL代码后,将使用EDA工具,如Altera的Quartus II,进行编译、综合、仿真和实现。Quartus II是一款强大的综合软件,支持多种设计输入格式,包括VHDL,能将高级设计抽象转化为实际的逻辑门级电路。它还内置了仿真器,可以验证设计在不同输入序列下的正确性。

在验证无误后,设计会被映射到EPM7128SLC84-15芯片上。这是一款CPLD(Complex Programmable Logic Device)芯片,具有较高的可编程性和灵活性,适合实现这样的序列检测逻辑。CPLD内部的宏单元会在编程后根据VHDL代码配置,实现所需的序列检测功能。

这个EDA课程设计涵盖了从概念到实现的全过程,包括了状态机设计、硬件描述语言编程、逻辑综合、芯片选型和硬件实现。通过这样的项目,学生不仅可以深入理解EDA技术,还能熟悉VHDL语言和现代电子设计流程,对于未来从事相关领域的研究和工作具有极大的实践价值。

283 浏览量

248 浏览量

362 浏览量

624 浏览量

441 浏览量

416 浏览量

2336 浏览量

987 浏览量

395 浏览量

ydd627706076

- 粉丝: 0

- 资源: 2

最新资源

- 单片机开发与典型应用设计

- Wrox.Professional.Visual.Studio.Extensibility.Mar.2008

- SQL*Loader学习资料

- IBM 掌握Ajax系列

- strutsbook

- 精通JAVA——sping面向对象轻量级架构

- 电脑知识初级篇电子书

- Algorithms.for.Programmers - ideas.and.source.code.Draft.Oct.2008

- linux配置Java开发

- Manning.Hibernate.Search.In.Action.Dec.2008

- Java 2 高级程序设计百事通

- Struts in Action 中文修正版.pdf

- 谭浩强 c语言程序设计

- 2008上半年网络管理员上午试题

- 数据库开发新版电子书_A Developer's Guide to Data Modeling for SQL Server

- 华为的编程规范和范例